Viterbi decoding based multi-path parallel loop block back trace technique

A technology of decoding and backtracking length, applied in other decoding technologies, error correction/detection using convolutional codes, digital transmission systems, etc., can solve the problems of register exchange algorithm area occupation and high power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

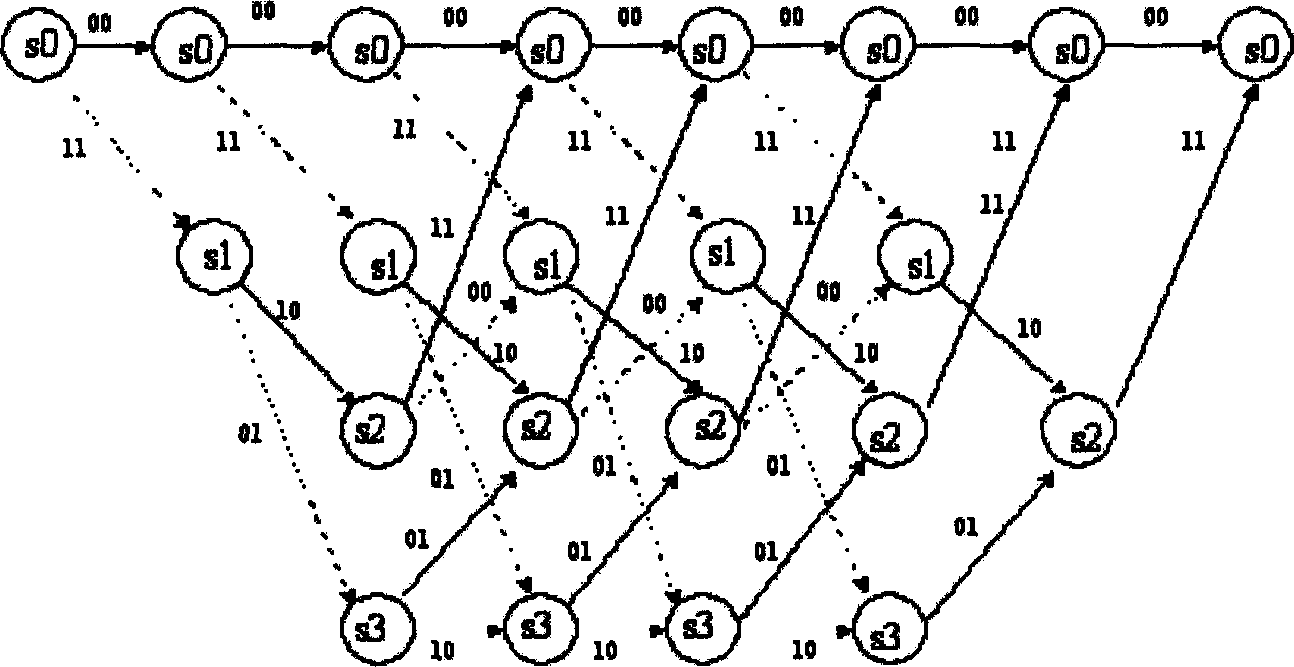

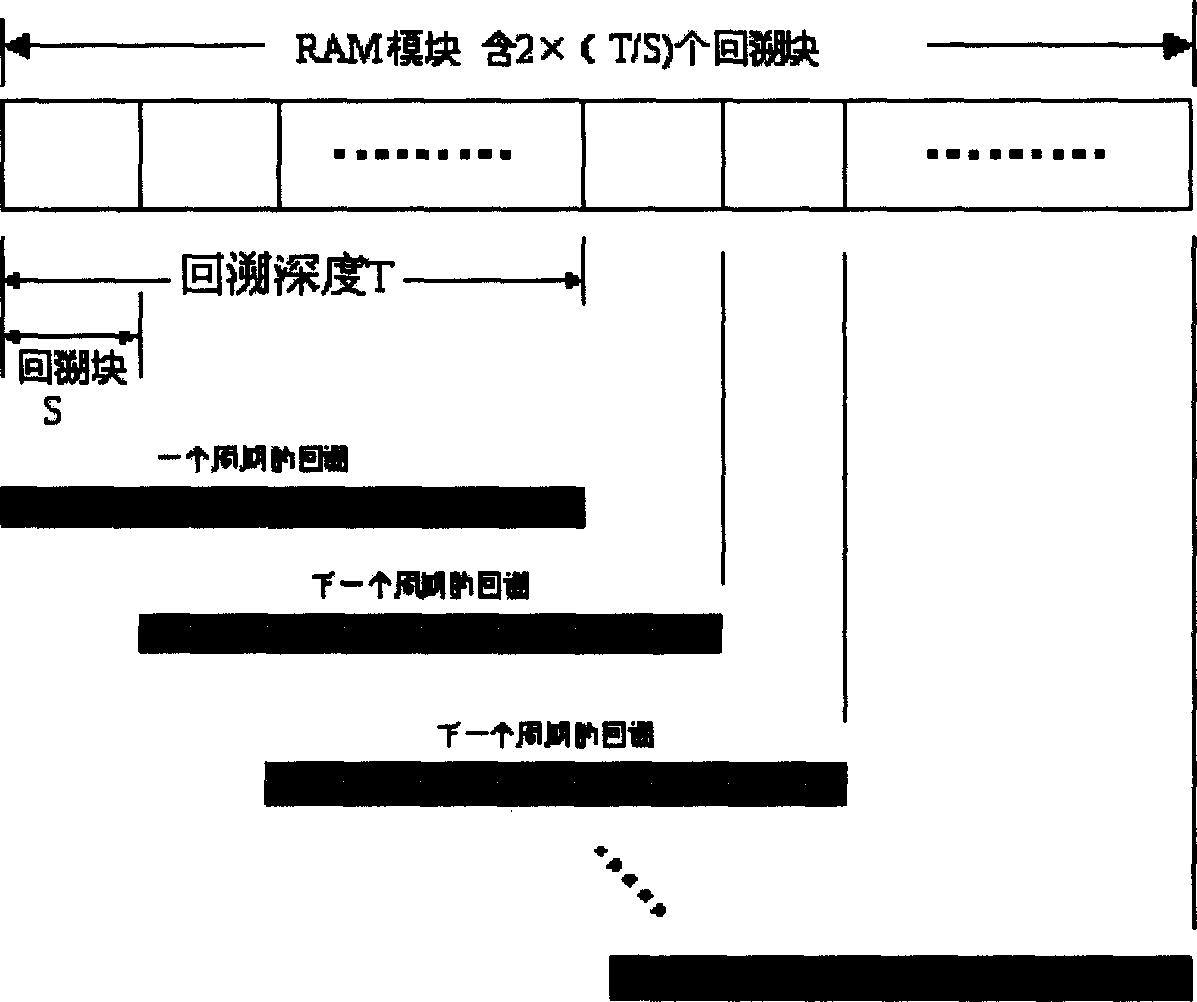

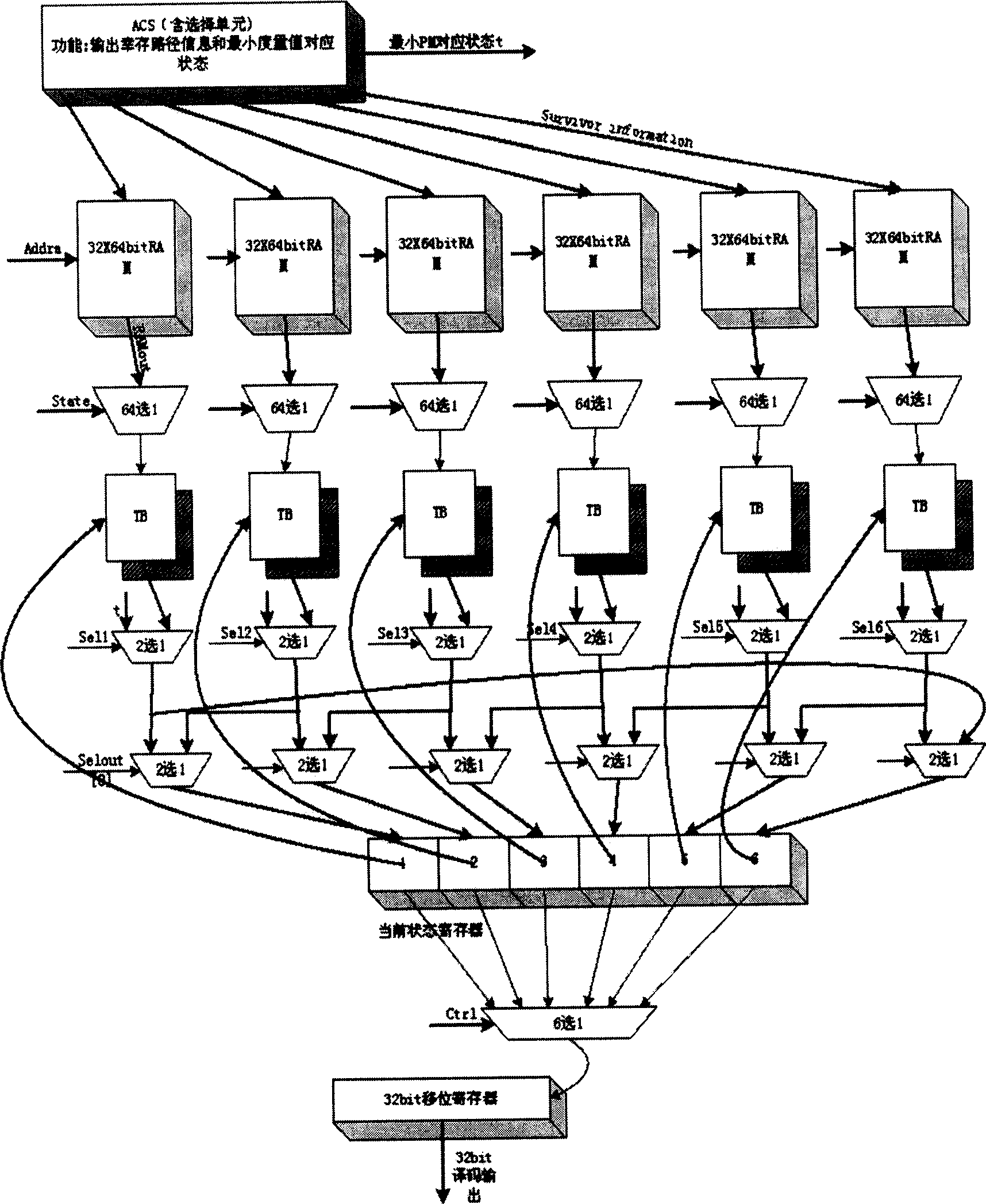

[0023] An implementation example of multi-path parallel loop block backtracking algorithm based on Viterbi decoding. The IEEE802.11a wireless LAN physical layer protocol stipulates that the source of the data sender must pass the convolutional code (133, 171) 8 Encoding, the data receiving end uses this Viterbi backtracking algorithm for decoding, and the decoding structure diagram is shown in the attached figure 1 , the parameters of the Viterbi decoder are set as the backtracking depth T = 96, the backtracking block size S = 32bit, and its decoding performance meets the practical requirements. The specific implementation steps are given below:

[0024] 1. A multi-channel parallel loop block backtracking algorithm based on Viterbi decoding. The branch metric and path metric of Viterbi decoding use the well-known radix-2 butterfly ACS network, and the convolutional code (133, 171) 8If the constraint length is 7, the convolutional code encoder has 6 registers, which are equiv...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More