Semiconductor device capable of being connected to external terminals by wire bonding in stacked assembly

An external terminal, semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problems of increased signal propagation delay, increased transistor junction capacitance, and large transistor size, etc. Avoid the effect of increasing the area and increasing the speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

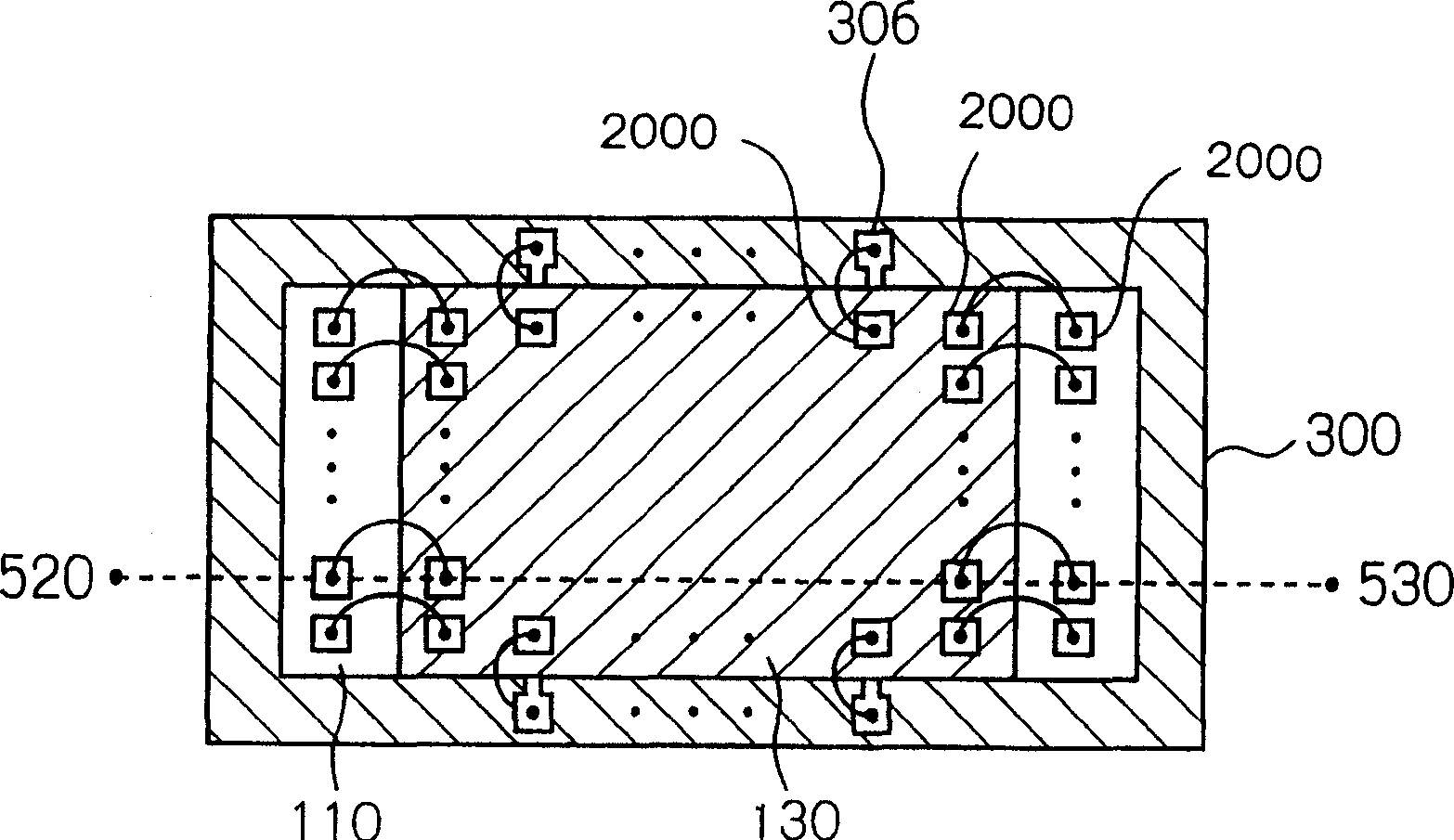

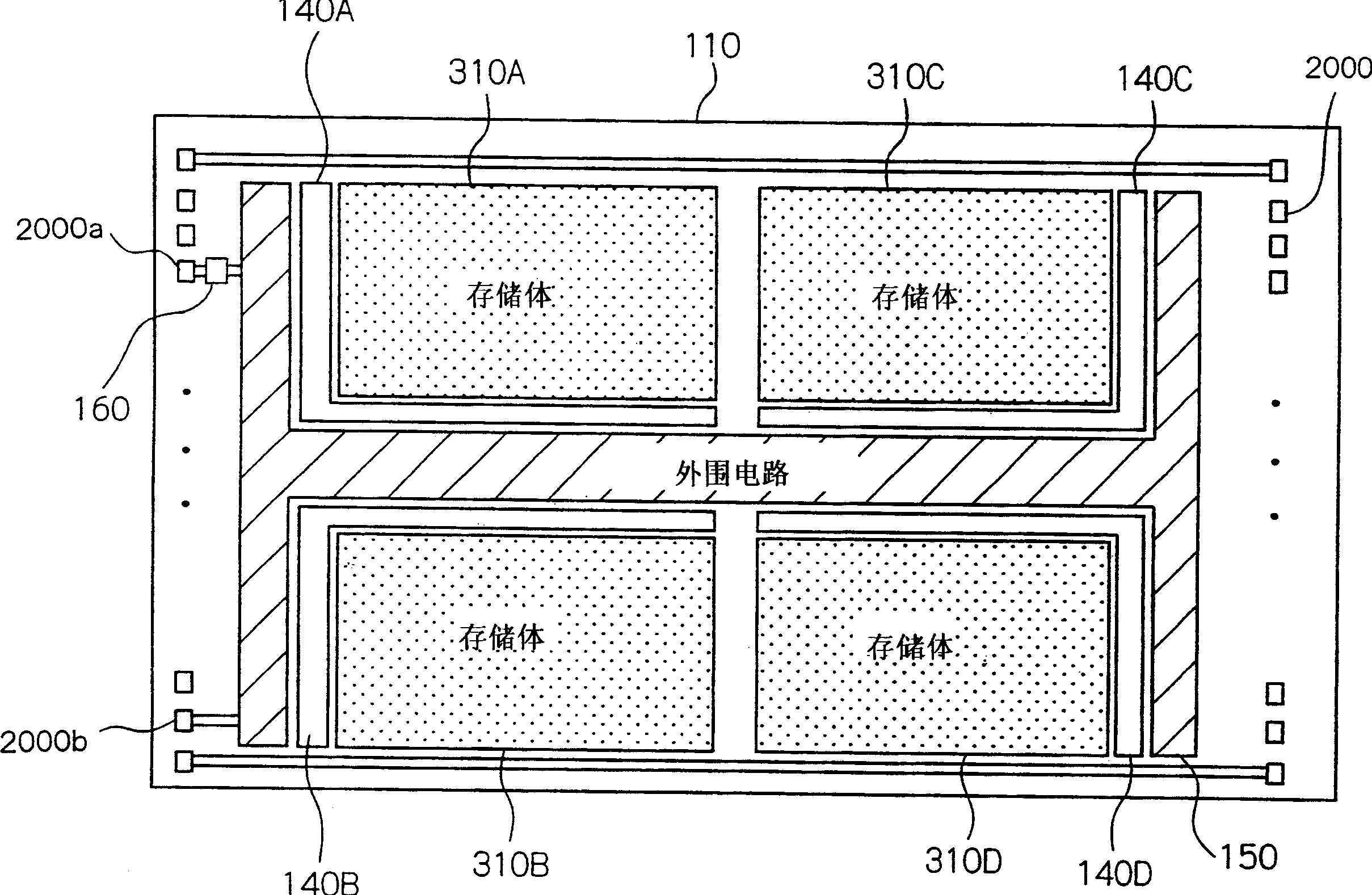

[0082] Figure 8A is a plan view showing the arrangement of the MCP according to the first embodiment of the present invention, and Figure 8B is Figure 8A An enlarged top view of the pad of the MCP shown in .

[0083] Such as Figure 8A As shown in , the MCP includes a lower memory chip 10 , an upper memory chip 20 and a CPU chip 30 as a component for controlling the lower and upper memory chips 10 , 20 . The lower and upper memory chips 10, 20 are of the same type and the same size. The lower memory chip 10 has pads 11a to 11e disposed close to and along one side 18 thereof. Similarly, the upper memory chip 20 has pads 21a to 21e disposed close to and along one side 28 thereof, and the CPU chip 30 has pads 31a to 31e disposed close to and along one side thereof.

[0084] The upper memory chip 20 is stacked on the lower memory chip 10 with the side 28 shifted in position from the side 18 in a direction perpendicular thereto so that the pads 11a to 11e of the lower memory c...

no. 2 example

[0134] According to a second embodiment of the present invention, one MCP includes three stacked memory chips.

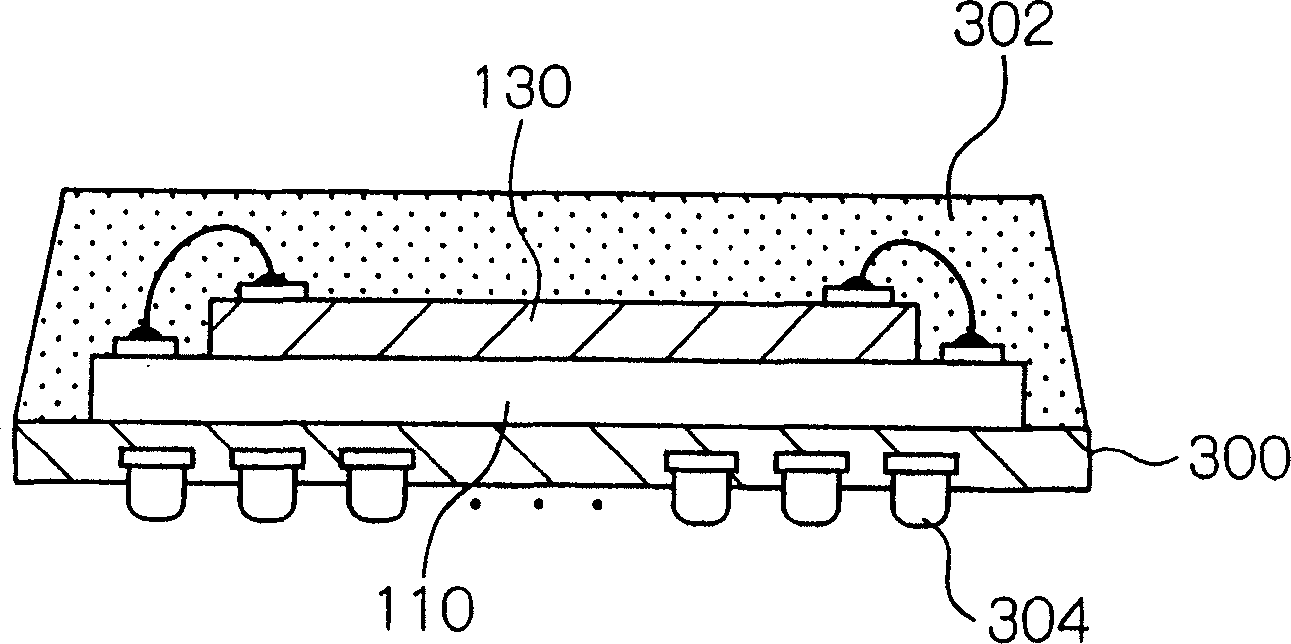

[0135] Figure 15 An MCP according to a second embodiment of the invention is shown in cross-section.

[0136] Such as Figure 15 As shown in , the MCP has two flash memories 91, 92 and DRAM 90. DRAM 90 may be replaced by SRAM (Static Random Access Memory).

[0137] Such as Figure 15 As shown in , two memories 91, 92 are stacked one on top of the other, as in the case of the memory chip according to the first embodiment, and a DRAM 90 is stacked on a flash memory 91. As in the first embodiment, the flash memories 91, 92 and DRAM 90 are connected by wire bonding to perform desired operations between the flash memories 91, 92 and DRAM 90 . The pads of the flash memories 91, 92 connected to the pads of the DRAM 90 are associated therein in the same manner as heretofore, and the above connection will not be described in detail below.

[0138] As in the first embo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More