Transmitter circuit, receiver circuit, clock data recovery phase locked loop circuit, data transfer method and data transfer system

A transmission system and transmission circuit technology, applied in the field of coding circuits, can solve the problems of insufficient reduction of clock recovery errors, missynchronization, and quality degradation of transmission paths.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

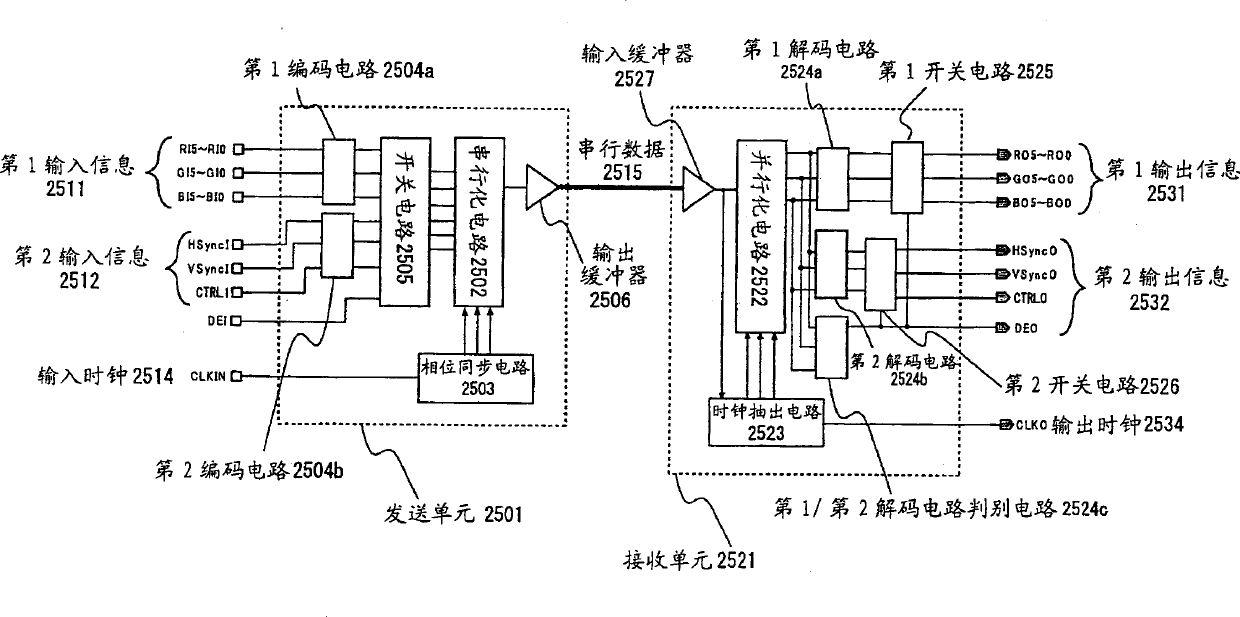

[0220] In this embodiment, another example of the first encoding circuit 2504a of the digital data transmission system of the present invention described in the above embodiments will be described. In addition, since other configurations are the same as those described in the above-mentioned embodiment, description thereof will be omitted here.

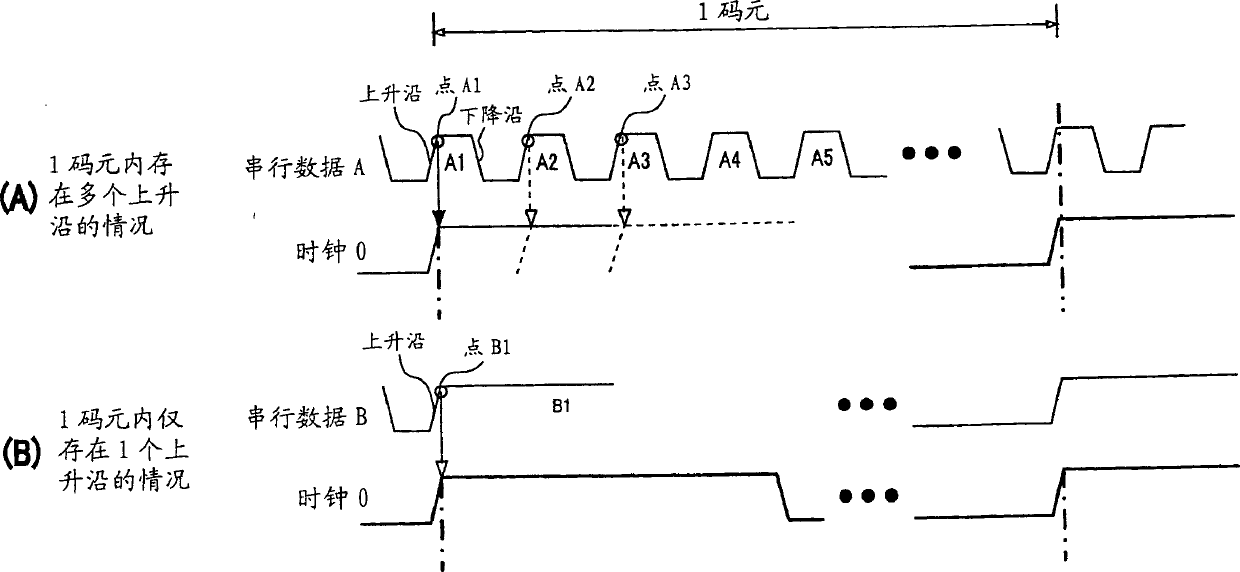

[0221] Refer to FIG. 30 . FIG. 30 is a diagram showing an example of data errors that occur when digital data is serially transmitted. In the data transmission system of the present invention, since serial digital data is transmitted at high speed using a pair of wires or cables, in the case of long-distance transmission by extending the length of wires or cables, or in the case of wiring or cables When the characteristics are poor, the waveform of digital data becomes dull, and bit errors due to ISI (Intersymbol Interference: Intersymbol Interference) tend to occur. This data error, as shown in FIG. 30 , appears conspicuously when ...

Embodiment 2

[0230] Example 2 is another example of the encoding method of the data transmission system described in the above-mentioned embodiments. In addition, since other configurations are the same as those described in the above-mentioned embodiment, description thereof will be omitted here.

[0231] The characteristic feature of this embodiment is that the transmitting unit 2501 has a DC balance circuit and performs encoding so as to achieve DC balance of the serial data. This DC balance circuit counts the accumulation of "high" (=1) and the accumulation of "low" (=0) of encoded data, and feeds back a signal corresponding to the counted number to the evaluation function. This feedback causes the evaluation function to select an encoding mode so that the accumulation of "high" (=1) and the accumulation of "low" (=0) of encoded data converge to the same number. The function of this DC balance circuit is called DC balance processing.

[0232] Here, the encoding method in the data tra...

Embodiment 3

[0246] Embodiment 3 is another example of the clock restoration phase synchronization circuit (clock extraction circuit) in the data transmission system of the above-mentioned embodiment.

[0247] Refer to Figure 36. FIG. 36 is a hardware block diagram showing the circuit configuration of a clock restoration phase synchronization circuit (clock extraction circuit) 2600 as a receiving circuit of the present invention. The clock extraction circuit 2600 of this embodiment is a clock extraction circuit that further includes the trimming frequency comparison circuit 80 in the clock extraction circuit 2523 described in the above embodiment. In addition, description of the same constituent elements as those described in the above-mentioned embodiment is omitted here.

[0248] The clock recovery phase synchronization circuit 2600 of this embodiment has a fine-tuning frequency comparison circuit 80, and after frequency adjustment (coarse frequency adjustment) of the voltage-controlled...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More