Solid state imaging apparatus

A solid-state imaging device and pixel technology, which is applied to electric solid-state devices, radiation control devices, image communication, etc., can solve the problems of reducing the dynamic range and sensitivity S/N ratio of the imaging device, and achieves improved sensitivity, reduced pixel area, and reduced aperture. rate increase effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

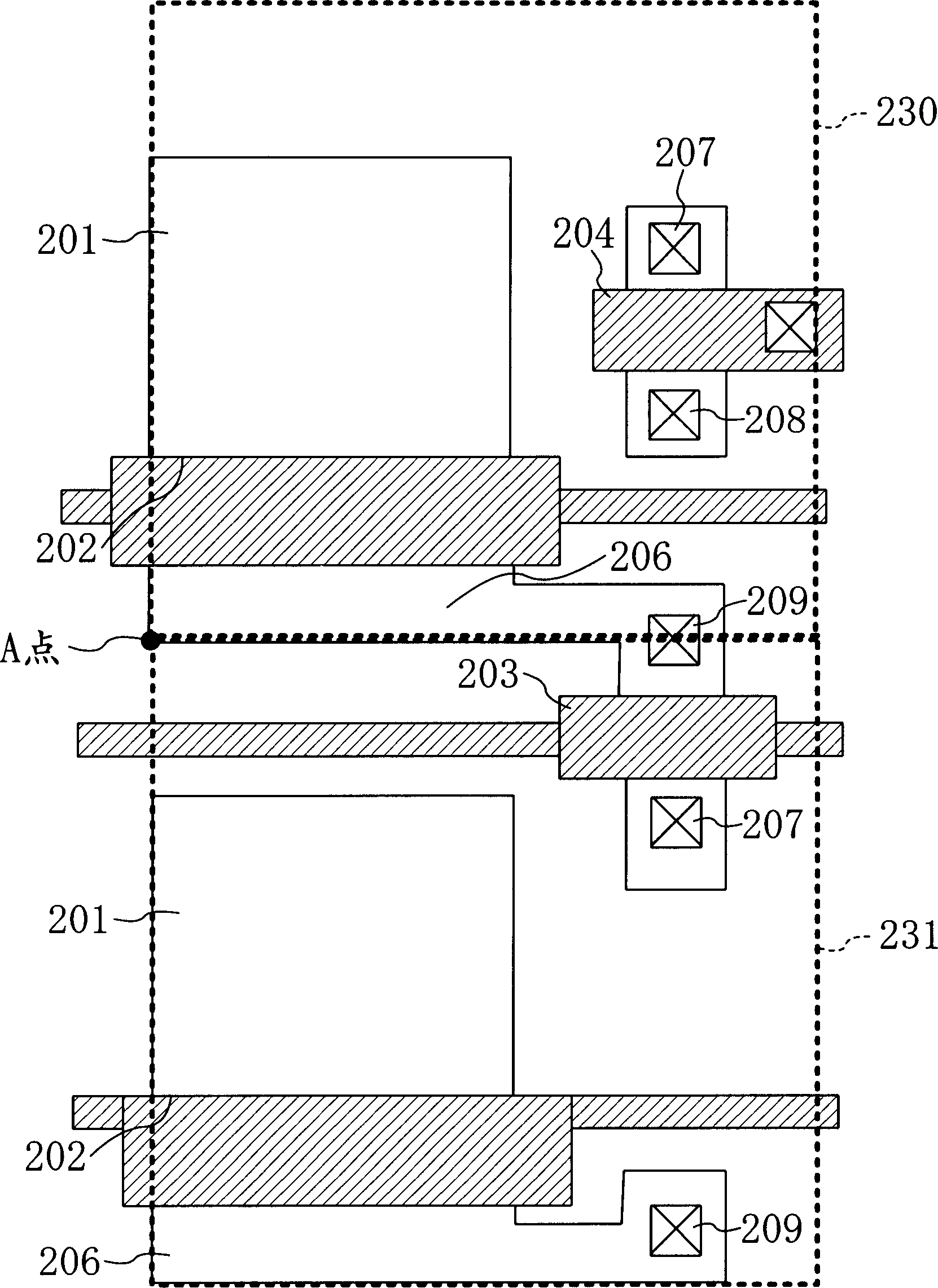

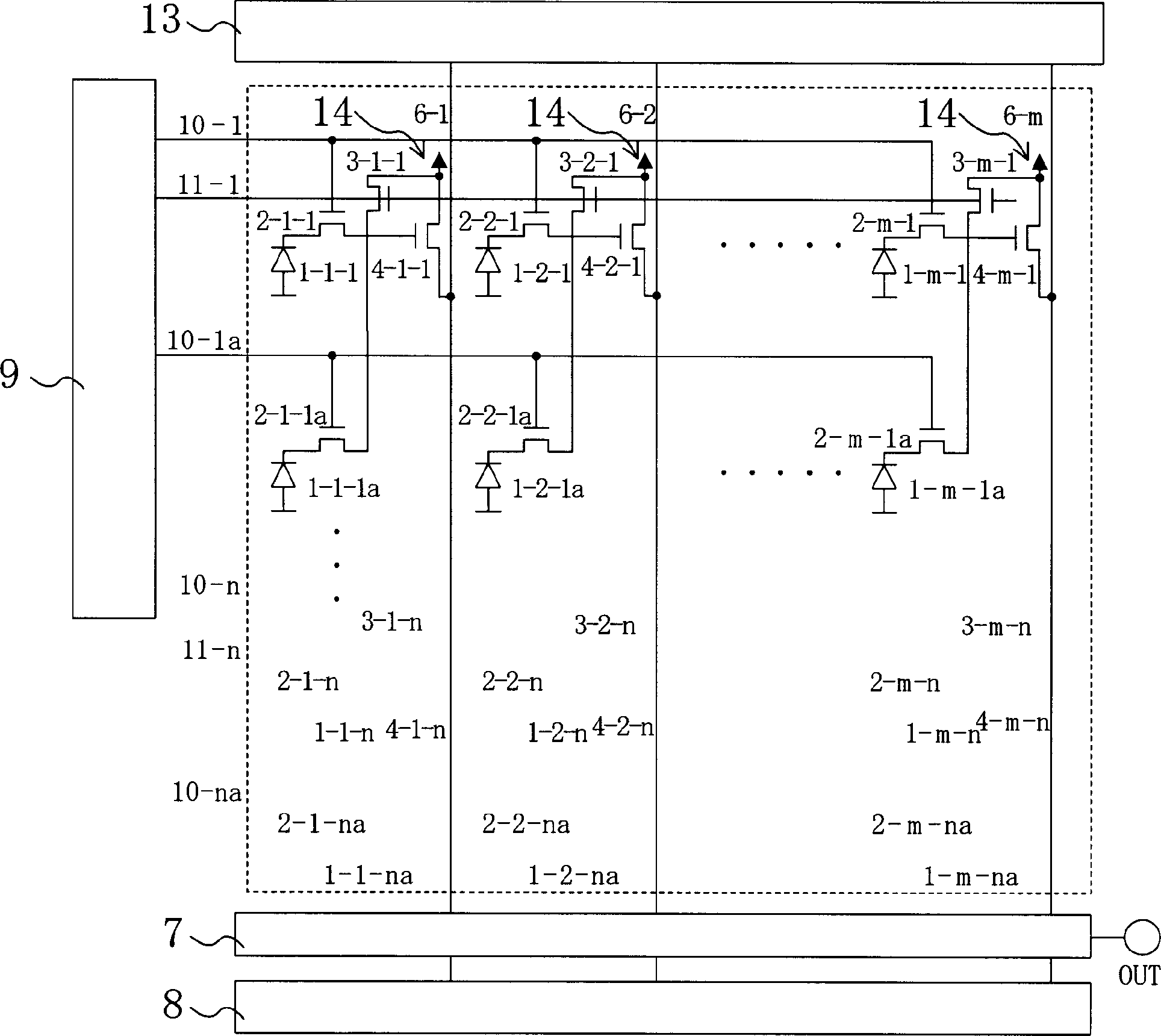

[0061] figure 1 is a diagram showing a pattern planar layout of pixel cells (pixels) of the solid-state imaging device according to the first embodiment of the present invention. In this figure, two pixels 230, 231 are shown. figure 2 is a circuit diagram showing an example of the solid-state imaging device in this embodiment.

[0062] like figure 2 As shown, the solid-state imaging device of this embodiment includes: photodiodes 1-1-1~1-m-n, transfer transistors 2-1-1~2-m-n, reset transistors 3-1-1~3-m-n, Amplifying transistors 4-1-1 to 4-m-n, row signal lines 6-1 to 6-m, row signal accumulation section 7, column selection section 8, row selection section 9, transfer transistor control lines 10-1 to 10- n. Reset transistor control lines 11 - 1 to 11 - n , load transistor group 13 and pixel portion power supply 14 . Here, both m and n are integers greater than or equal to 2.

[0063] The photodiodes 1-1-1~1-m-n convert the incoming light into electrical signals; the tr...

no. 1 example 1

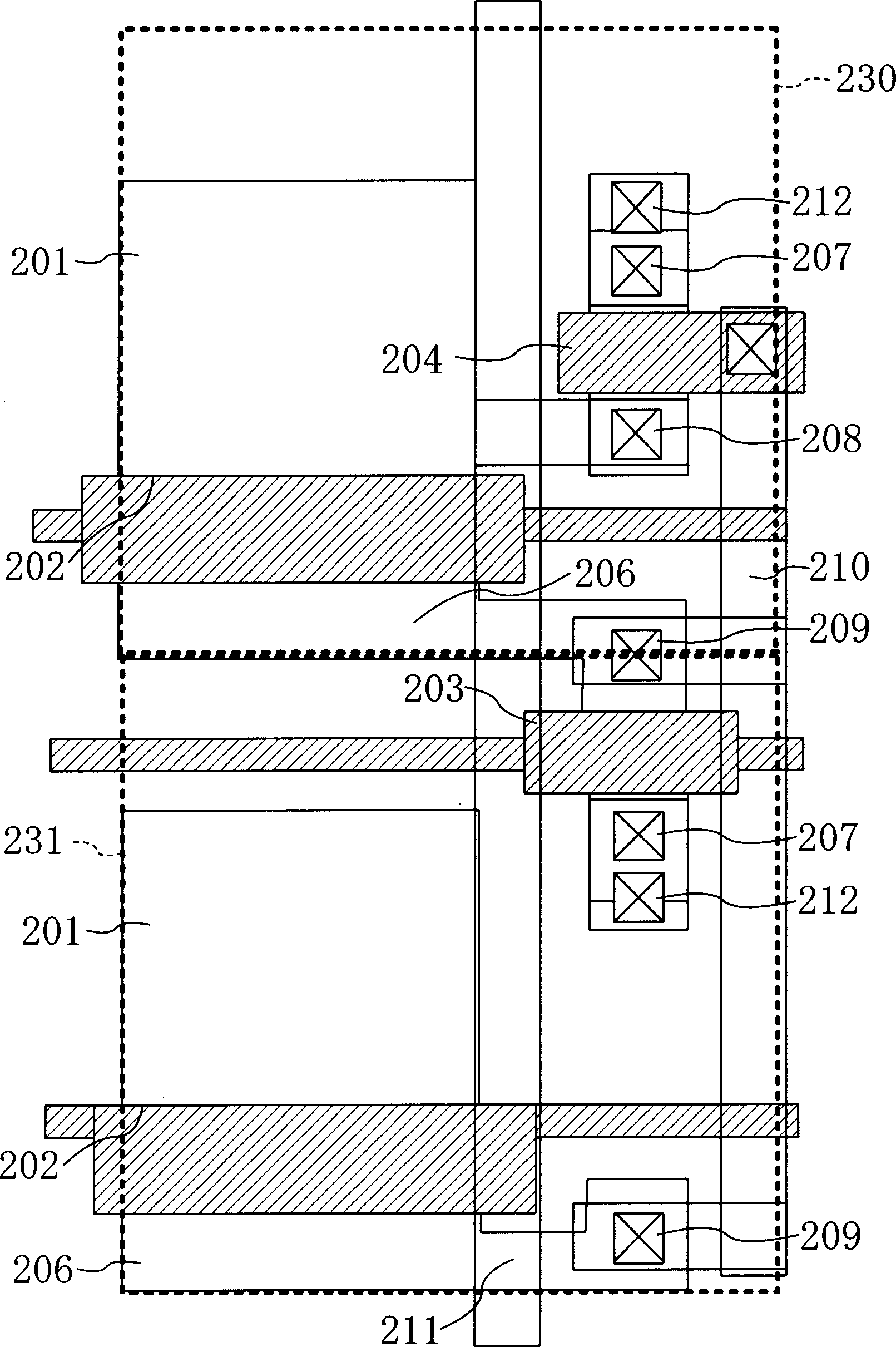

[0083] Figure 5 It is a diagram showing the pattern plan layout of the pixel cell portion of the solid-state imaging device according to the second embodiment of the present invention. This figure shows specific two pixel cell portions in a plurality of pixel cells of the same shape that are periodically arranged in a solid-state imaging device. Like the first embodiment, the pattern plan layout of the pixel cell in this embodiment is the pattern plan layout of a three-transistor type CMOS sensor in which two pixels share a reset transistor and an amplification transistor. Just to add, Figure 5 Aluminum wiring and the like are not shown, and the circuit configuration of the pixel cell as the solid-state imaging device of this embodiment is described in Figure 13 In the same pixel circuit as a plurality of pixels share 1 amplification device.

[0084] The adjacently arranged first pixel 230 and the second pixel 231 each have: a photodiode 201; a transfer transistor for tr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More