Method for ion implantation of high-voltage transistor LDD

A high-voltage transistor and ion implantation technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of poor reliability and the inability of transistors to further increase the breakdown voltage, so as to reduce hot carriers effect, improve reliability, and increase breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

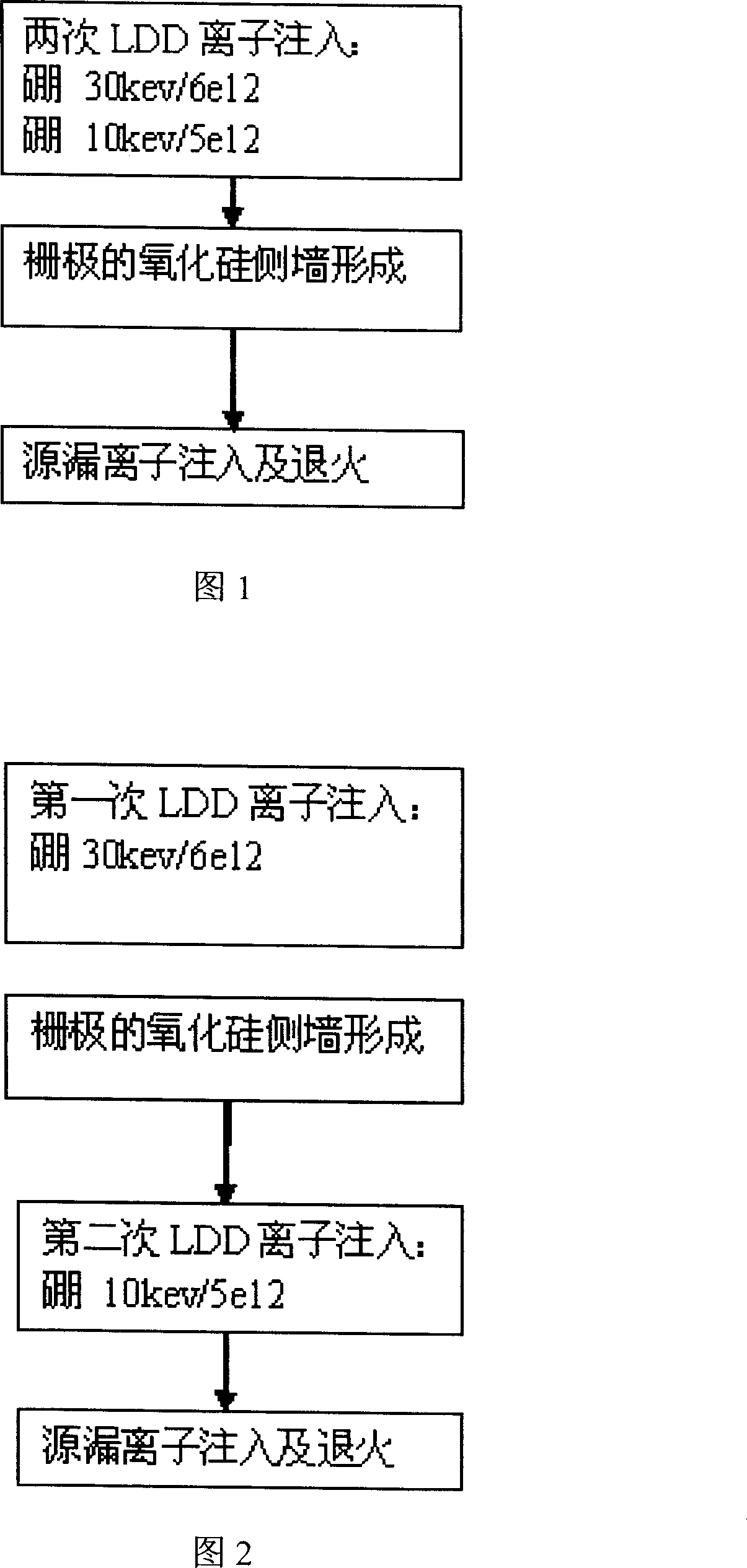

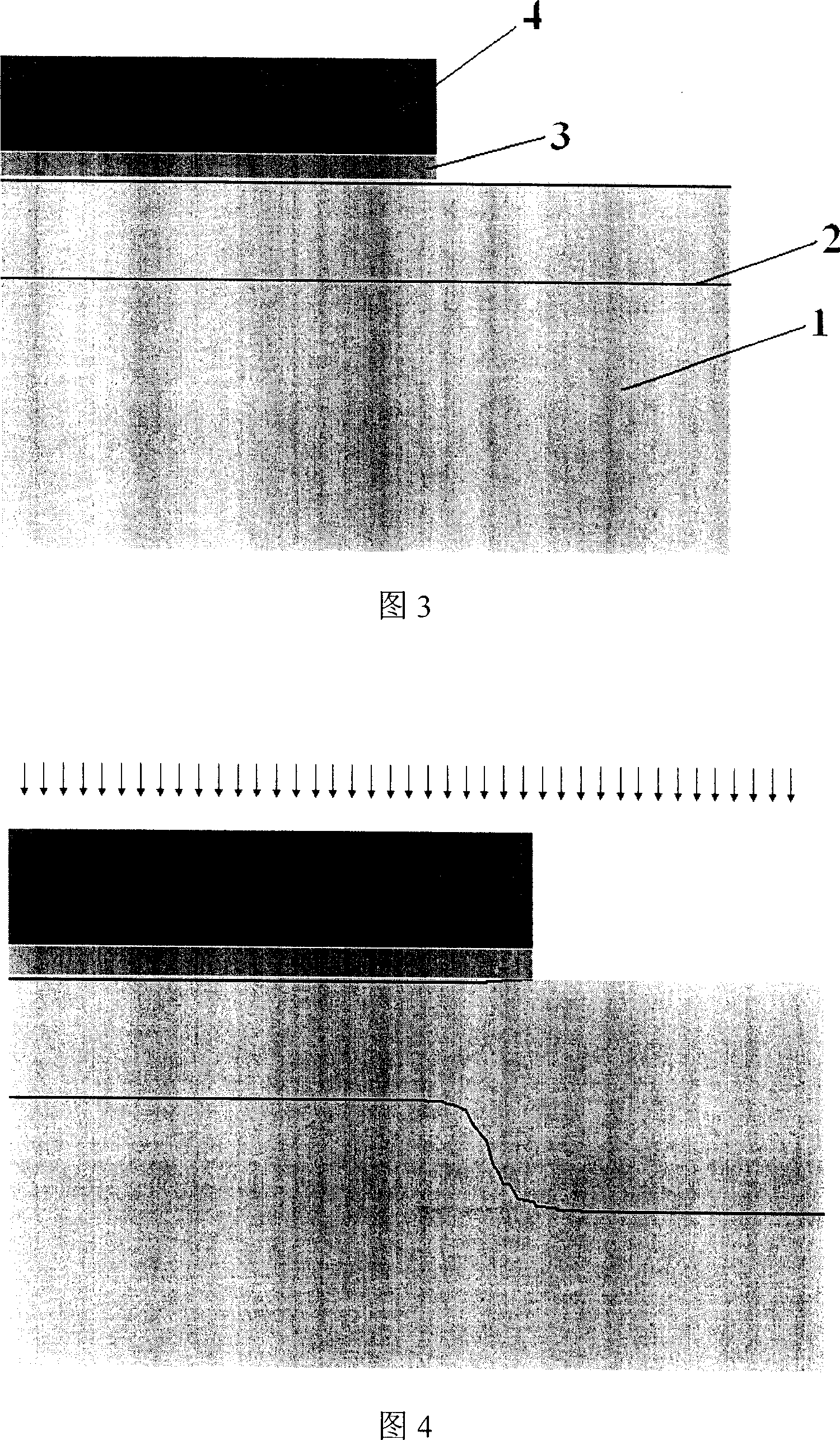

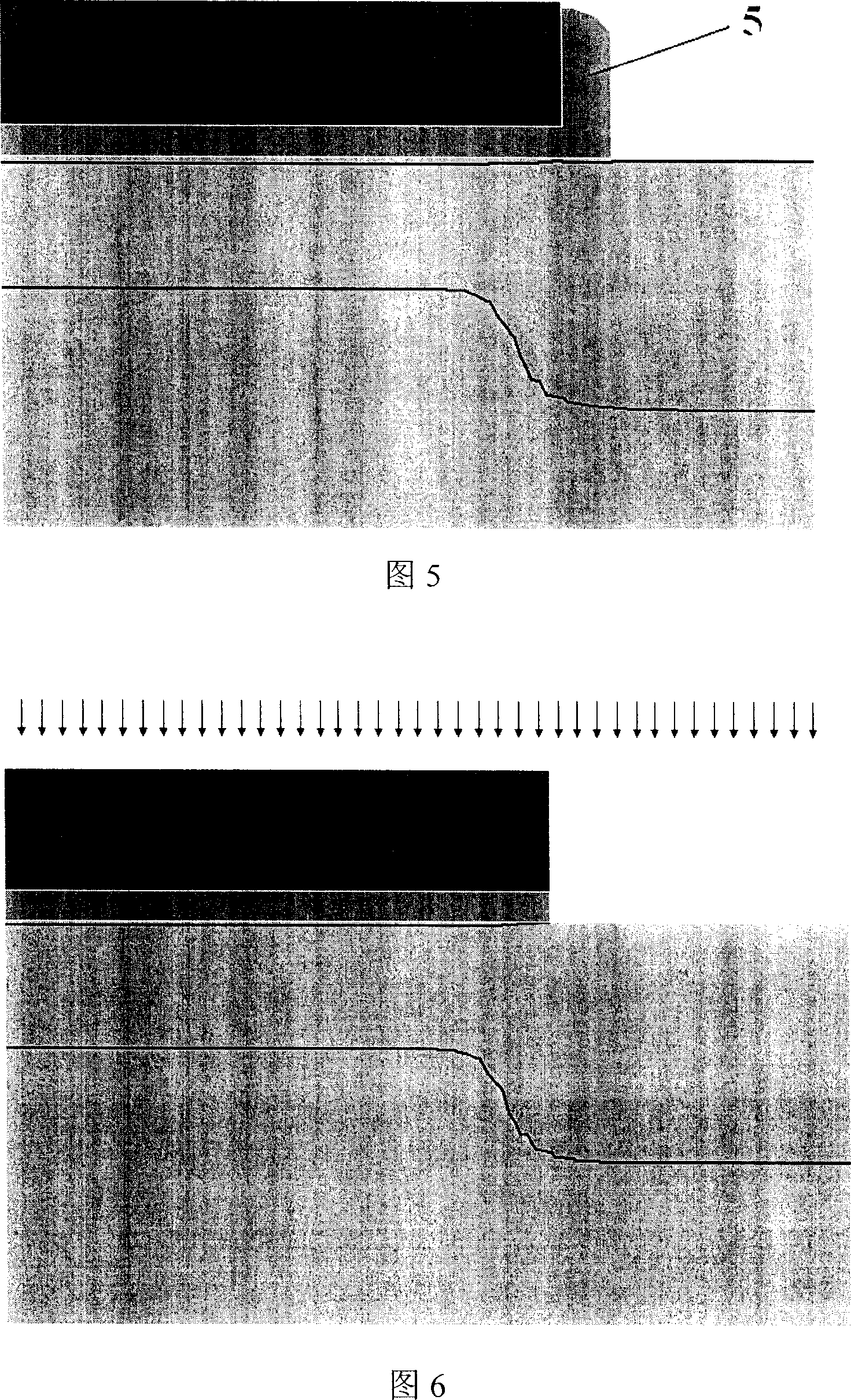

[0024] The flow chart of the LDD ion implantation method of the high-voltage transistor of the present invention can be seen in FIG. 2, which specifically includes four steps. FIG. 3 shows a device structure that has not been ion implanted, which includes the underlying silicon substrate 1, gate silicon oxide 3, and polysilicon 4. For this device, the first LDD ion implantation is performed, the implanted element is boron, the implanted boron dose is 30keV, and the energy is 6e12. After this step, the PN junction interface 2 will be deformed, as shown in FIG. 4. Then the silicon nitride sidewall spacer 5 of the gate is formed, as shown in FIG. 5. Then perform the second LDD ion implantation, the implanted element is still boron, the implanted boron dose is 10kev, and the energy is 5e12. As shown in Figure 6, the energy of this LDD ion implantation is lower than that of the first LDD ion implantation energy. Finally, source and drain ion implantation and annealing are performed. As...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More