Static discharging protective element structure for improving trigger effect

A technology of electrostatic discharge protection and components, applied in the direction of electrical components, electric solid devices, circuits, etc., can solve the problems that the ESD protection circuit cannot be guaranteed to be connected in parallel with finger devices, and achieve a strong protection effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

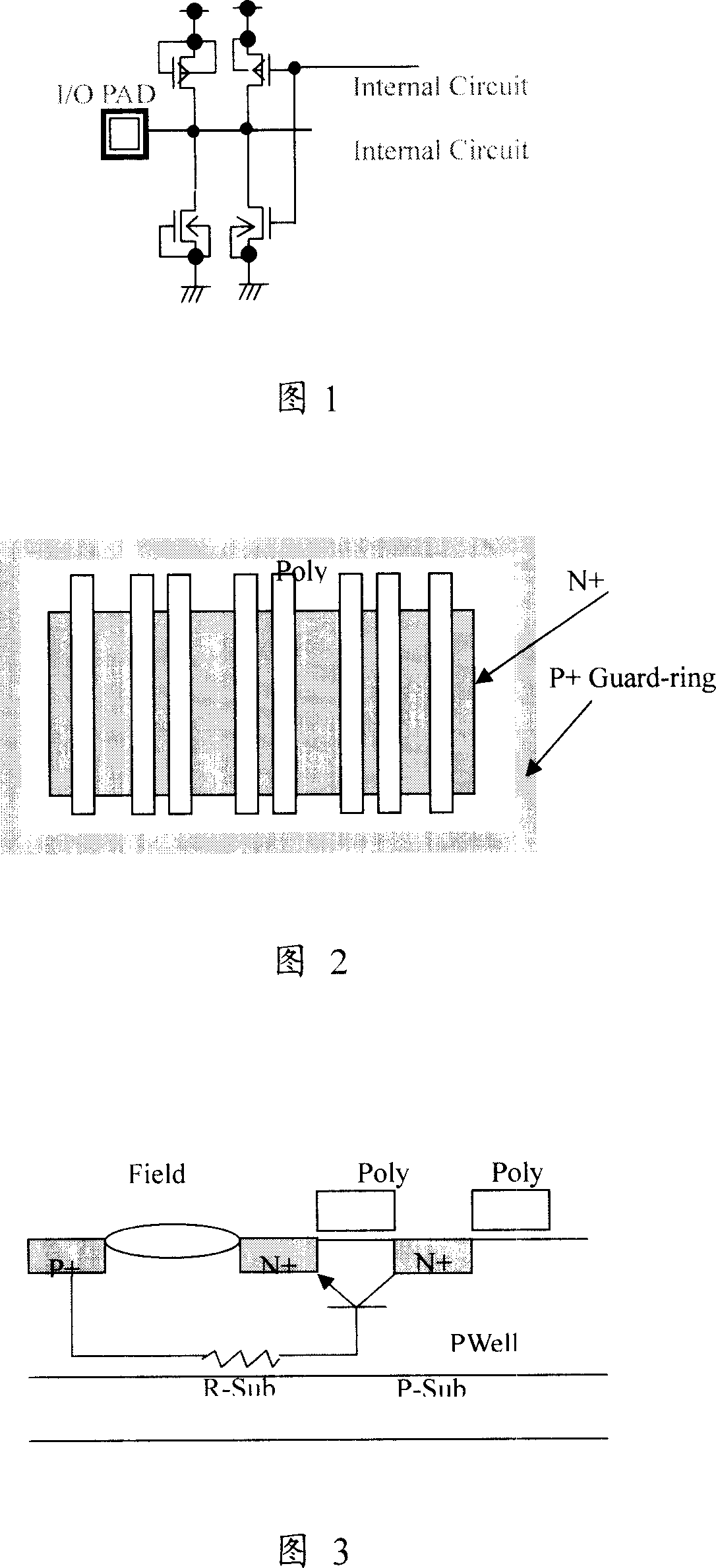

[0016] As shown in FIG. 4 , an ESD protection element structure of the present invention improves the traditional layout method by inserting an N-well ring between the Nch Buffer transistor and the well-controlled guard-ring.

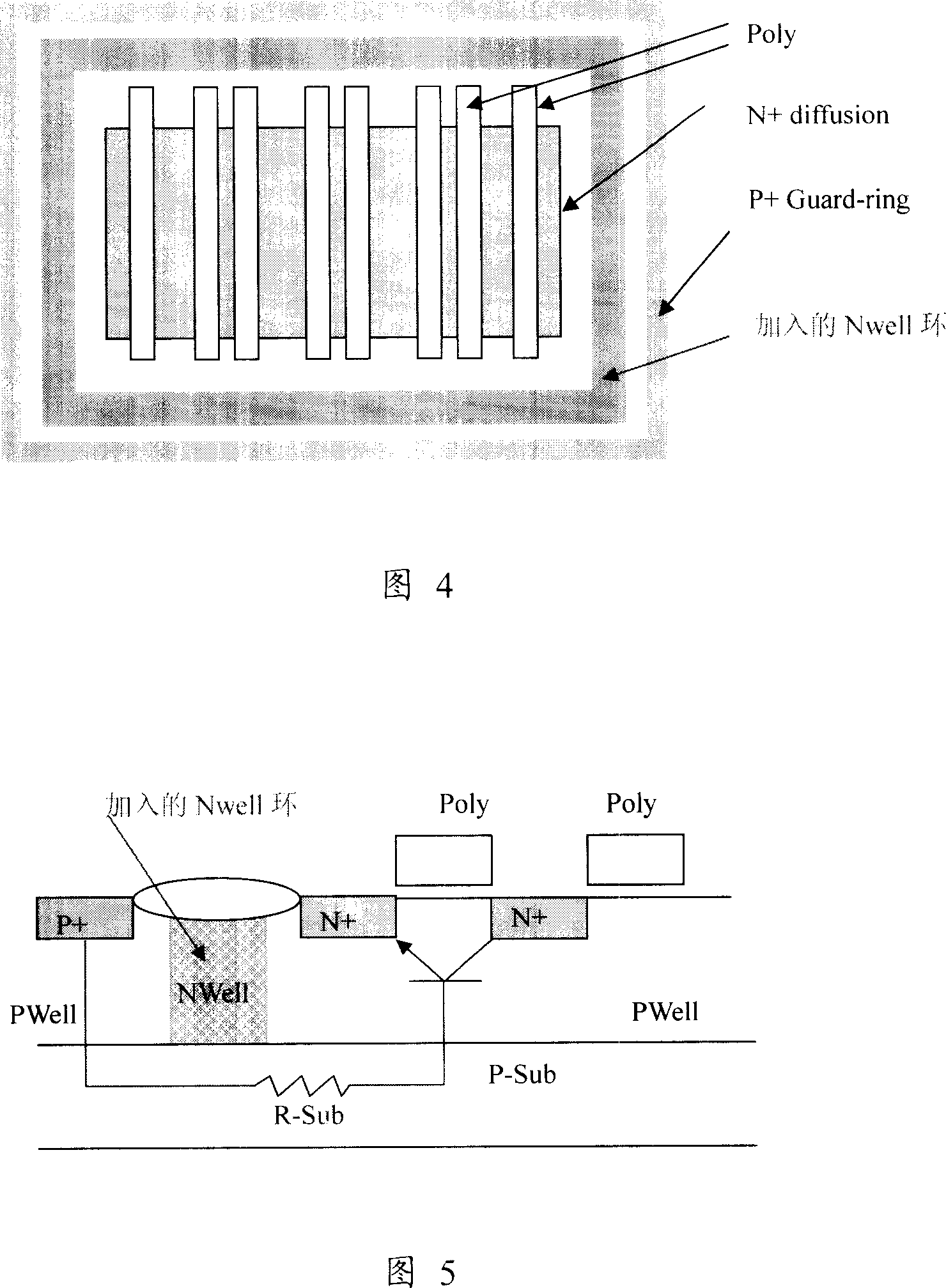

[0017] As shown in Figure 5, from the schematic cross-sectional view of the NMOS, the NMOS element structure is formed on a P-type well of a substrate, and the NMOS element structure includes a gate, which is arranged in the P-type well; a first An N+ diffusion region is arranged in the P-type well and is used as a drain of the NMOS device structure; a second N+ diffusion region is arranged in the P-type well and is used as a source of the NMOS device structure ; A P+ diffusion region is set in the P-type well as a protection ring, and an N well ring is provided between the P+ protection ring and the N+ diffusion region. In addition, the NMOS element structure also includes a plurality of lightly doped drains arranged in the P-type well around the gate,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More