Method of forming a metal wiring in a semiconductor device

a metal wiring and semiconductor technology, applied in the direction of semiconductor/solid-state device details, chemical vapor deposition coating, coating, etc., can solve the problems of low efficiency of cvd method, low deposition speed and cost, and shorten the lifetime of metal wiring, so as to achieve the effect of easy forming a copper wir

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0010] The disclosed method will be described in detail by way of a preferred embodiment with reference to accompanying drawings.

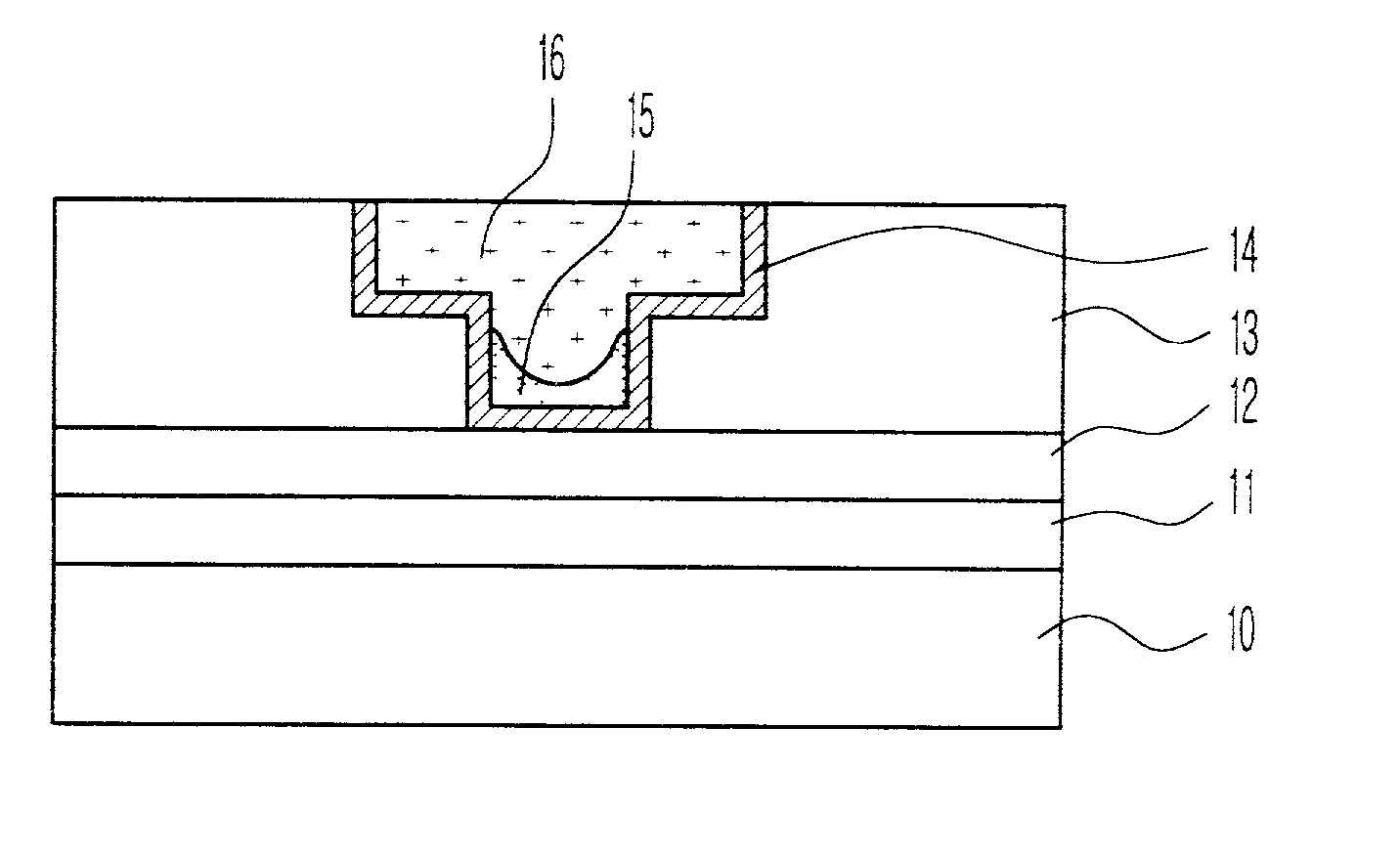

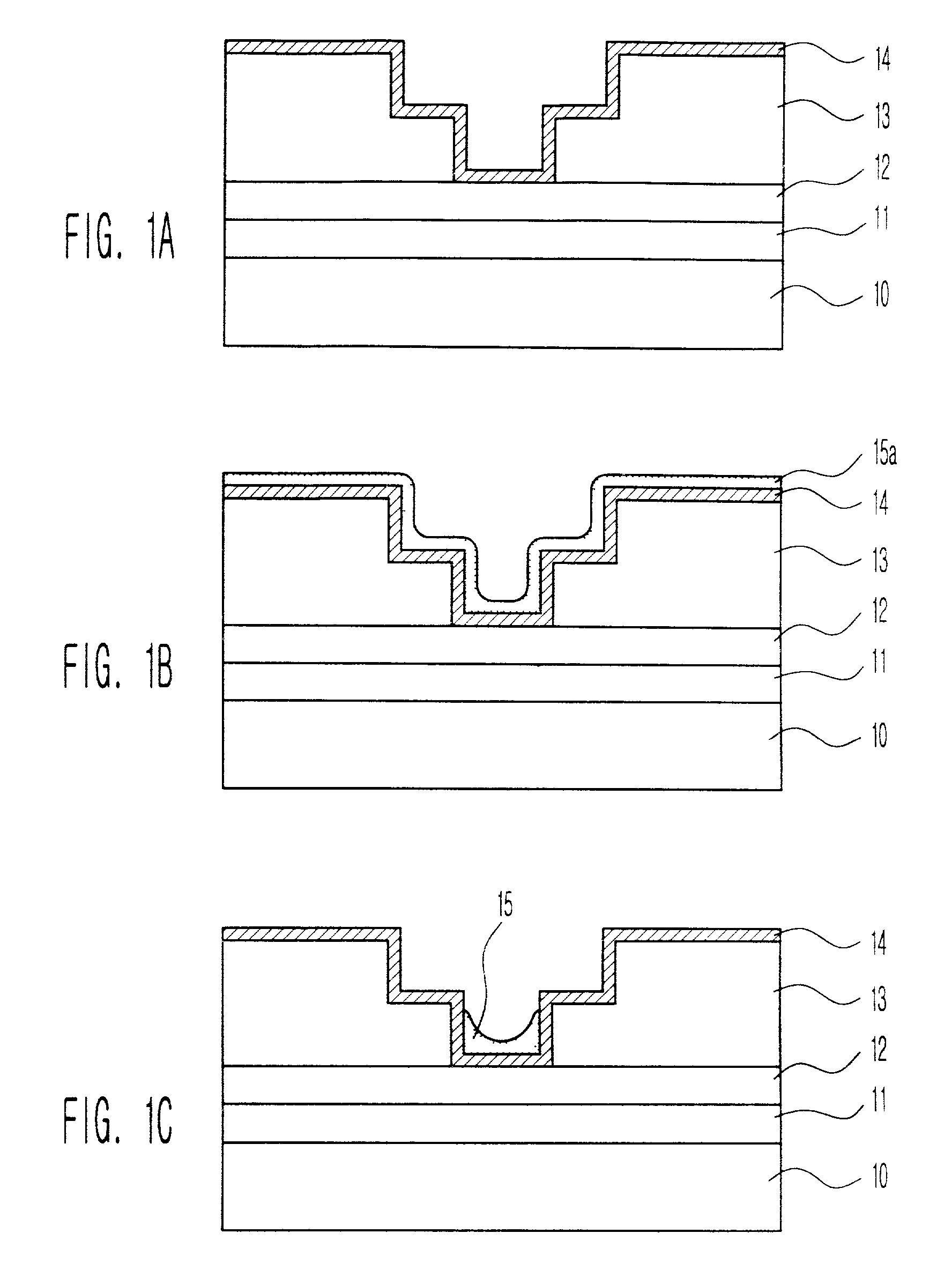

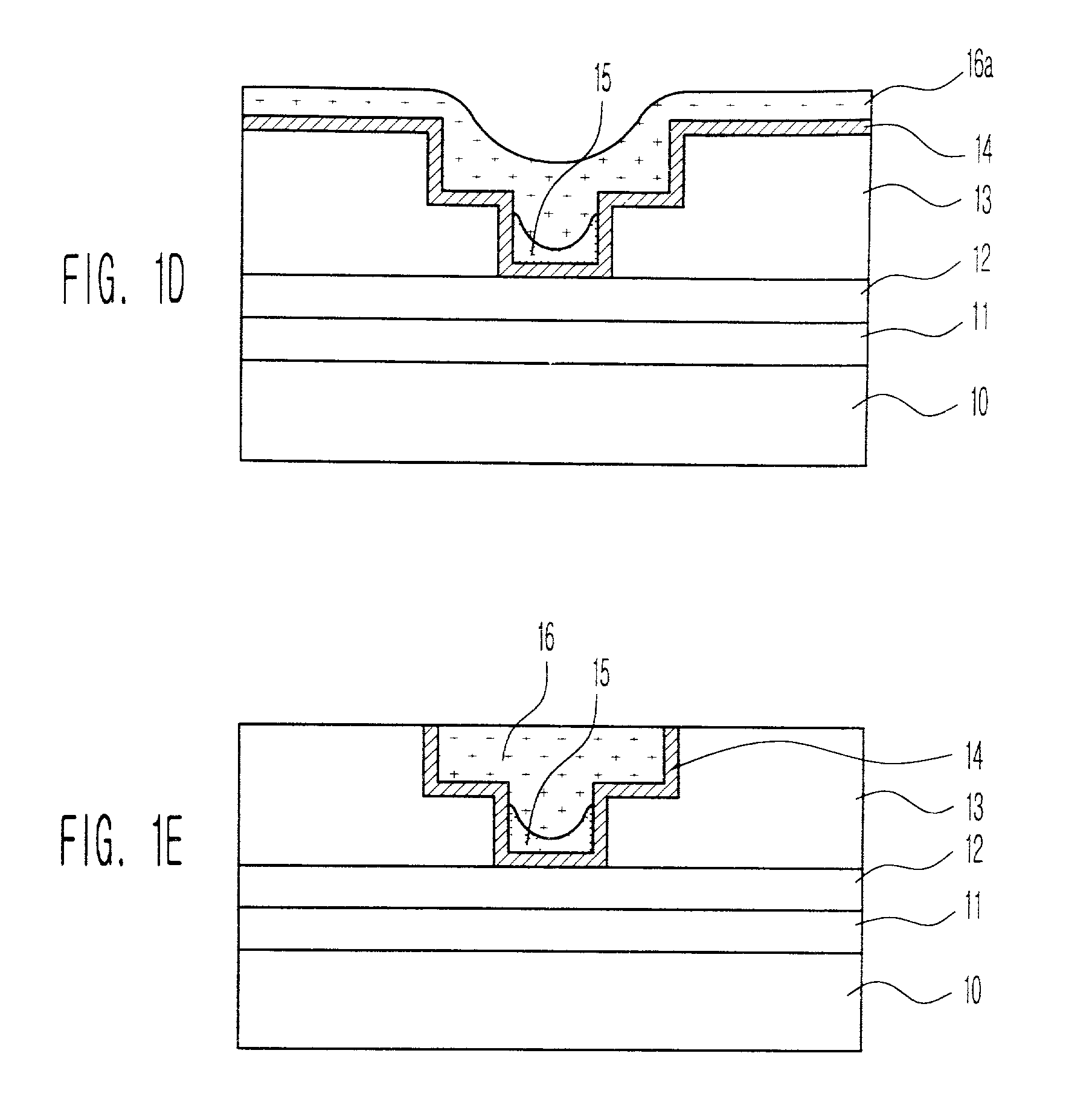

[0011] Referring now to FIG. 1A, an insulating film 1, a lower metal layer 12 and a second insulating film 13 are sequentially formed on a semiconductor substrate 10 in which various components for forming a semiconductor device is formed. A damascene pattern consisting of a trench and / or via is then formed in the second insulating film. Next, a cleaning is performed to remove an oxide layer remaining on the surface of the lower metal layer 12 exposed by the damascene pattern. Thereafter, a diffusion prevention film 14 is formed on the second insulating film 13 including the damascene pattern. The surface of the diffusion prevention film 14 is exposed to a plasma process in order to facilitate formation of a subsequent chemical enhancer layer 15a or a seed layer 15a which is formed in thickness ranging from about 50 to about 500 .ANG. using copper (Cu) on ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Time | aaaaa | aaaaa |

| Time | aaaaa | aaaaa |

| Pressure | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More