Semiconductor device and method for manufacturing the same

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

embodiment 1

[0075] Embodiment 1

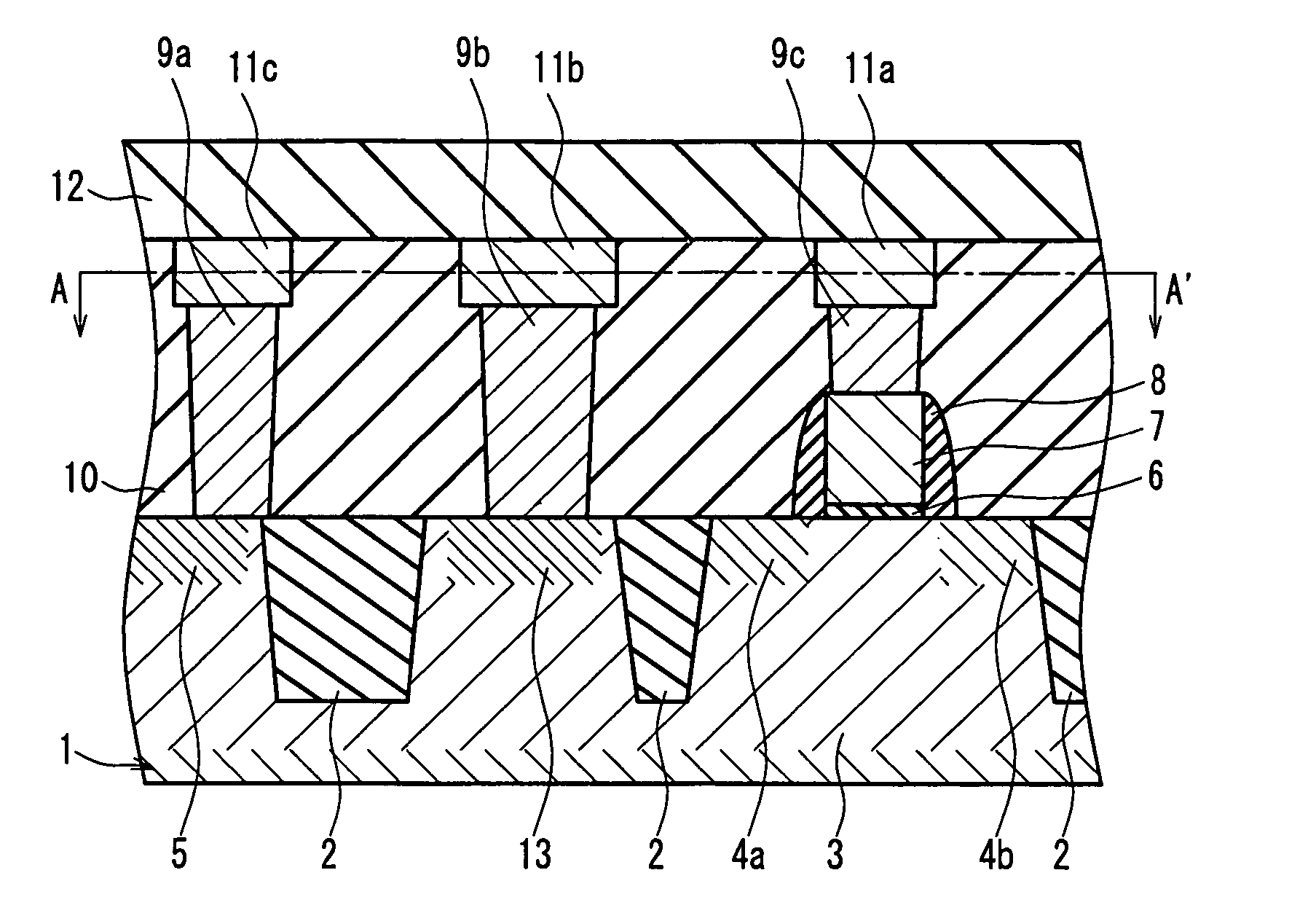

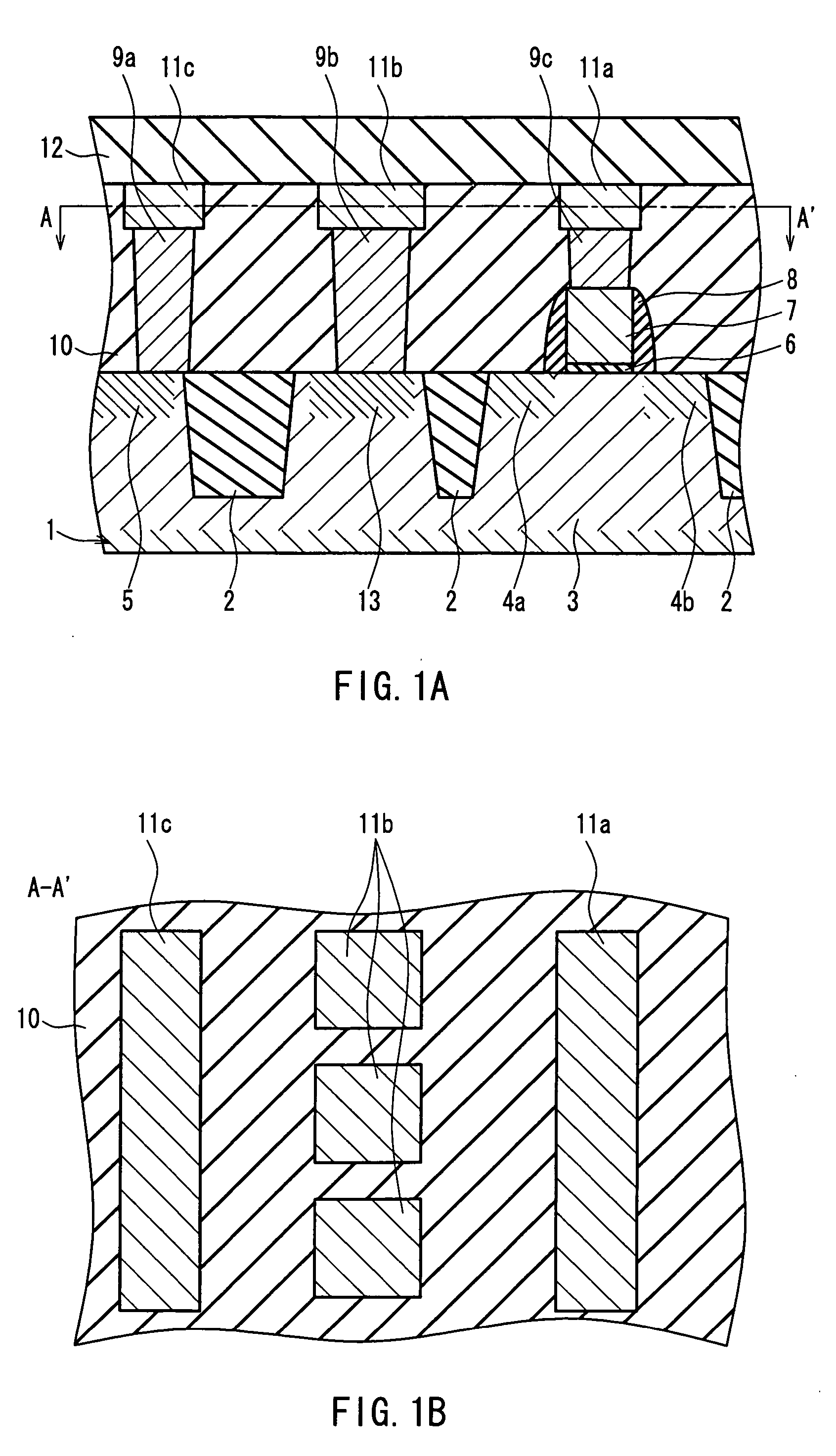

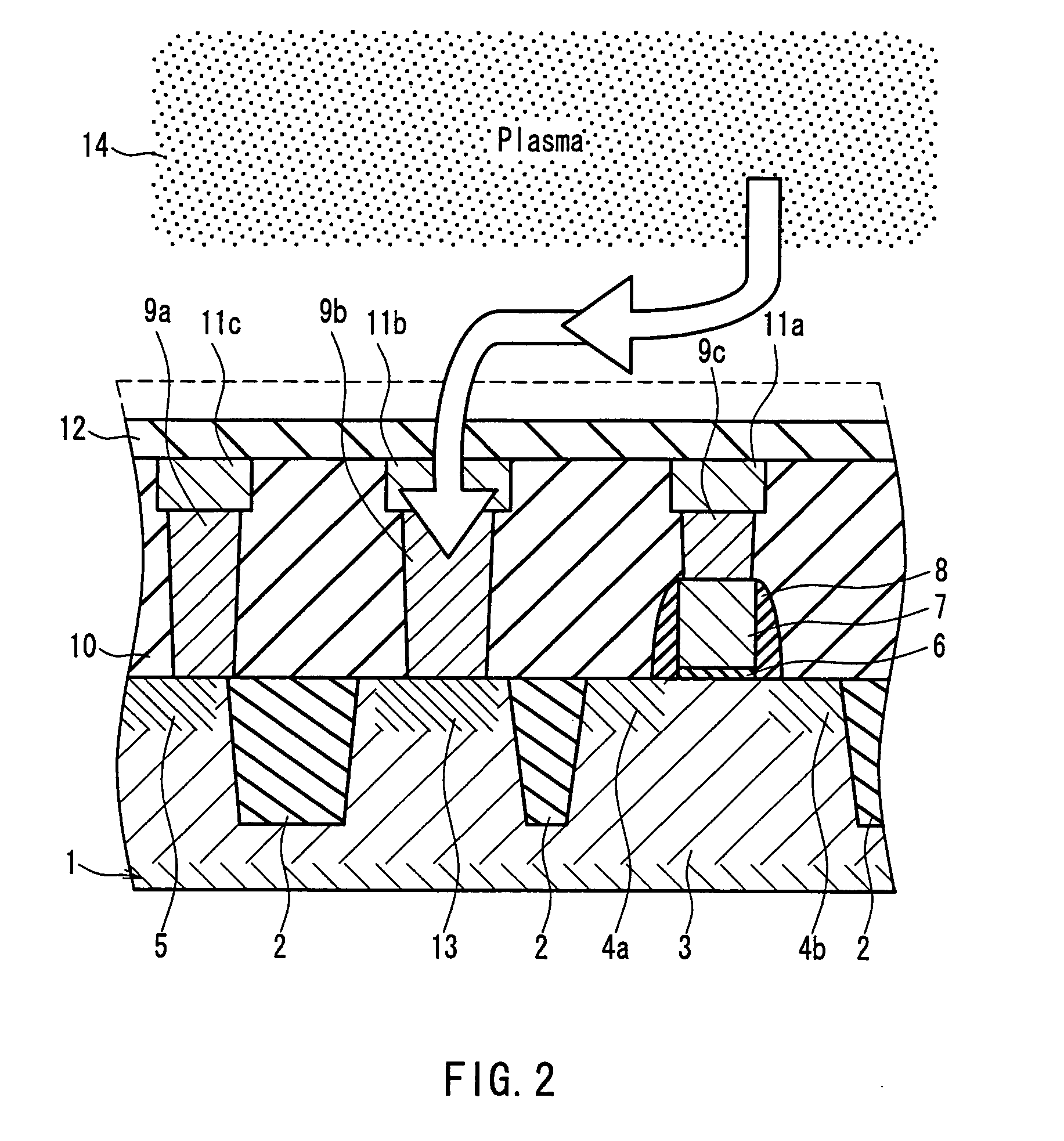

[0076] Hereinafter, a semiconductor device and a method for manufacturing the semiconductor device of Embodiment 1 of the present invention will be described with reference to FIGS. 1 and 2. First, the configuration of the semiconductor device of Embodiment 1 will be described with reference to FIG. 1.

[0077] As shown in FIG. 1A, the semiconductor device of Embodiment 1 includes an n-type silicon substrate 1 as in the semiconductor device shown in FIG. 11 described in “Background Art”, and a plurality of element separations 2 are formed on the silicon substrate 1 at a predetermined interval so as to be exposed on the silicon substrate 1.

[0078] Between the element separations 2 on the silicon substrate 1, an n-channel MOS transistor is formed with a p-well 3 formed in the internal portion of the n-type silicon substrate 1, a gate insulating film 6 and a gate electrode 7 formed of n+ polysilicon, and a source (n+) region 4a and a drain (n+) region 4b that are provi...

embodiment 2

[0096] Embodiment 2

[0097] Next, a semiconductor device and a method for manufacturing the semiconductor device of Embodiment 2 of the present invention will be described with reference to FIGS. 3 and 4. First, the configuration of the semiconductor device of Embodiment 2 will be described with reference to FIG. 3. In FIGS. 3 and 4, the portion denoted by the same reference numeral as in FIG. 1 is the same portion as in FIG. 1.

[0098] As shown in FIG. 3, in Embodiment 2, unlike in Embodiment 1, a conductor 11d that is a second dummy conductor is provided. The conductor 11d also is formed simultaneously with the conductors 11a and 11b by the damascene method, but the entire circumference of the conductor 11d is insulated by the underlying interlayer insulating film 10 and the interlayer insulating film 12, and the conductor 11d is electrically suspended.

[0099] Next, a method for manufacturing the semiconductor device of Embodiment 2 and a function of dummy conductors will be describe...

embodiment 3

[0113] Embodiment 3

[0114] Next, a semiconductor device and a method for manufacturing the semiconductor device of Embodiment 3 of the present invention will be described with reference to FIGS. 6 to 9. First, the configuration of the semiconductor device of Embodiment 3 will be described with reference to FIG. 6.

[0115] As shown in FIG. 6A, the semiconductor device of Embodiment 3 includes a p-type silicon substrate 101 as in the semiconductor device shown in FIG. 13 described in “Background Art”, and a plurality of element separations 102 are formed on the silicon substrate 101 at a predetermined interval so as to be exposed on the silicon substrate 101.

[0116] Between the element separations 102 on the silicon substrate 101, a p-channel MOS transistor is formed with an n-well 103 formed in the internal portion of the silicon substrate 101, a gate insulating film 106 and a gate electrode 107 formed of p+ polysilicon, and a source (p+) region 104a and a drain (p+) region 104b that a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More