Signal-processing apparatus and electronic apparatus using same

a technology of electronic equipment and processing equipment, applied in the direction of multiple processing units, instruments, television systems, etc., can solve the problems of large processing amount, inability to mount to the built-in system, and inability to improve the processing efficiency of calculators

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

(First Embodiment)

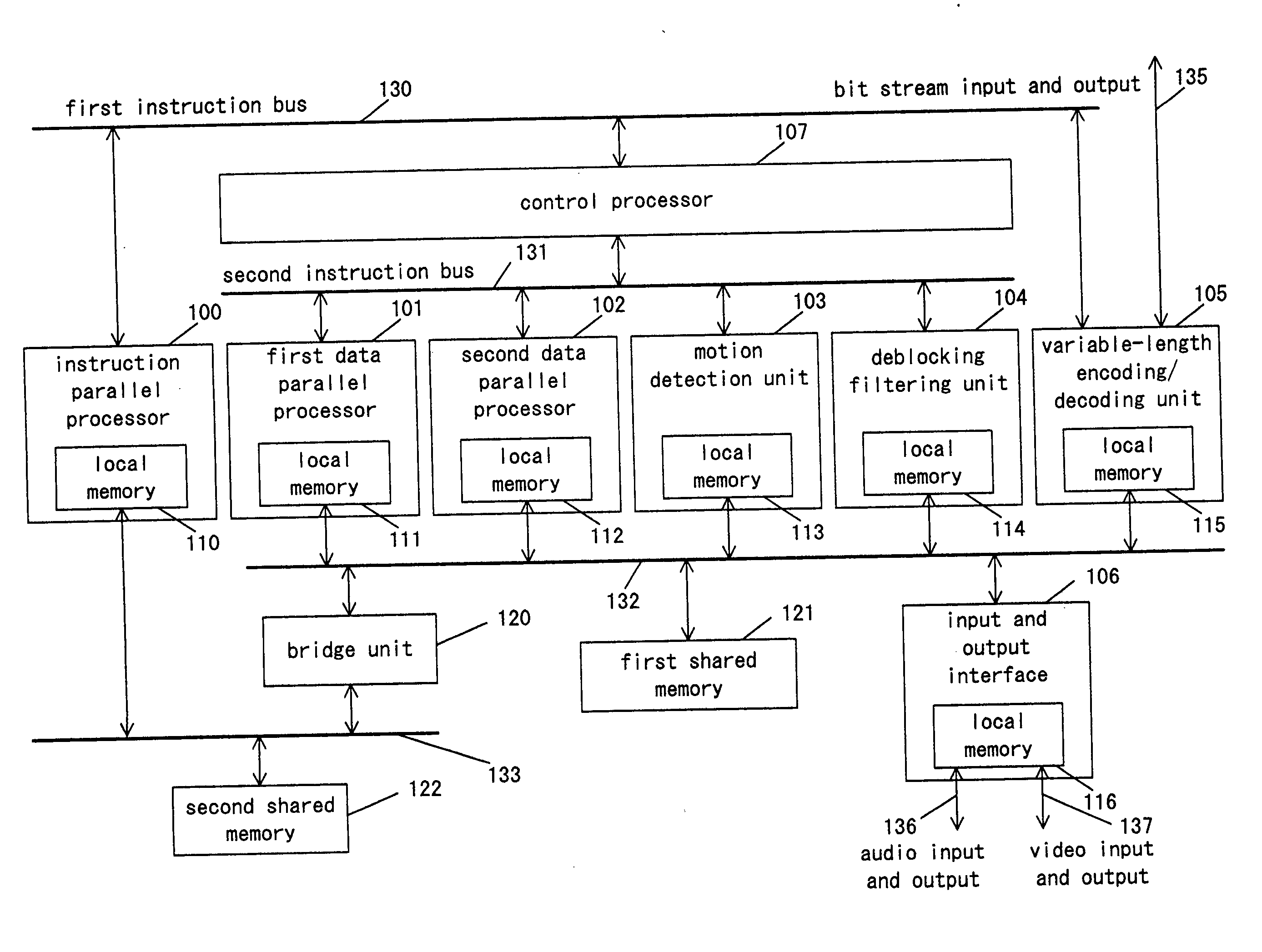

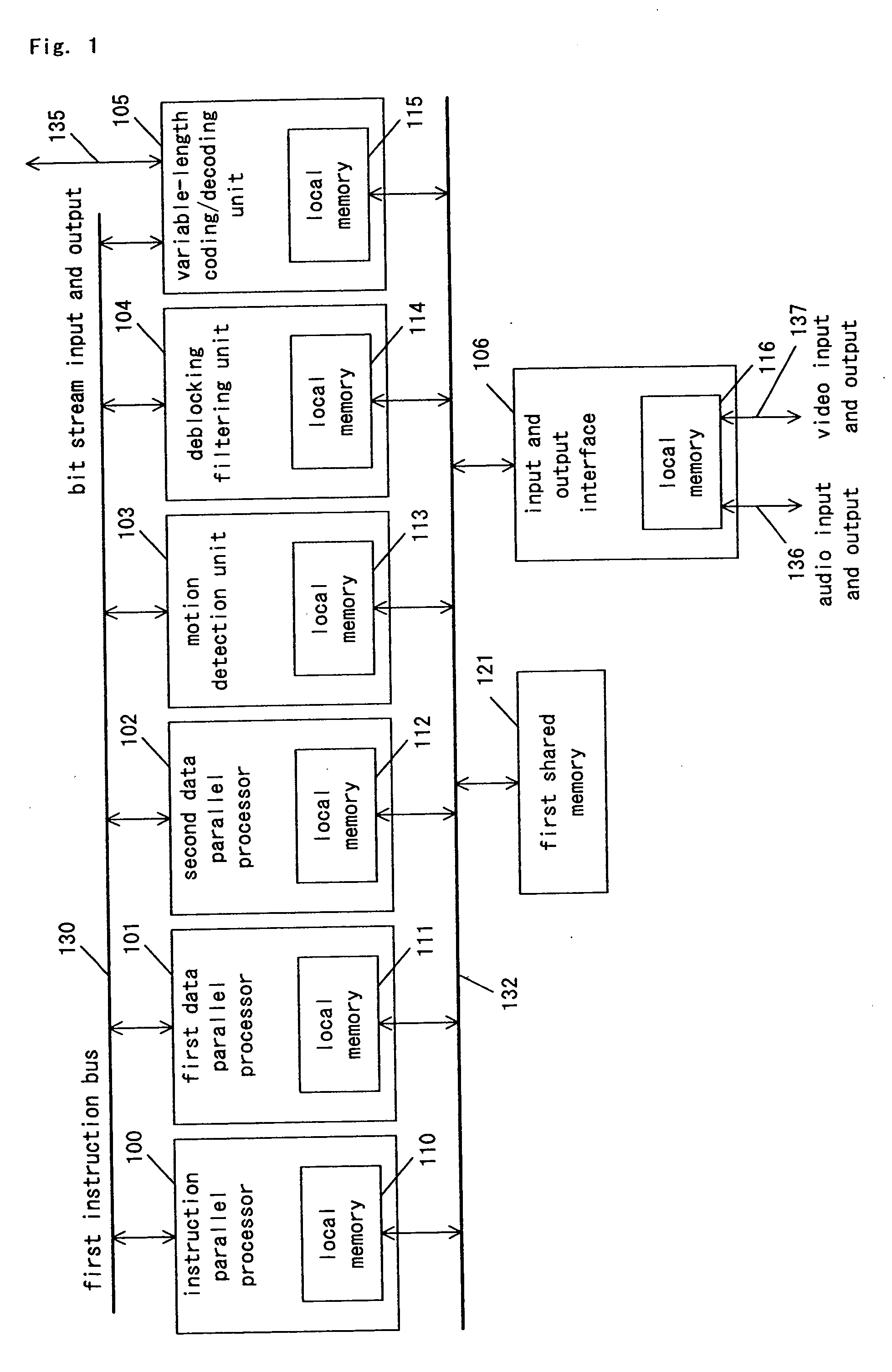

FIG. 1 is the block diagram of the signal-processing apparatus in the first embodiment of the present invention. The signal-processing apparatus of the present embodiment comprises: an instruction-parallel processor 100 having a local memory 110; a first data-parallel processor 101 having a local memory 111; a second data-parallel processor 102 having a local memory 112; a motion detection unit 103 having a local memory 113; a de-blocking filtering unit 104 having a local memory 114; a variable-length coding / decoding unit 105 having a local memory 115; an input and output interface 106 having a local memory 116; a first shared memory 121; a first instruction bus 130; and a first data bus 132. The processors 100 to 102 and the units 112 to 116 are connected to the first instruction bus 130, and the local memories 110 to 116, the first shared memory 121 and the input and output interface 106 are connected to the first data bus 132. The variable-length coding / decoding...

second embodiment

(Second Embodiment)

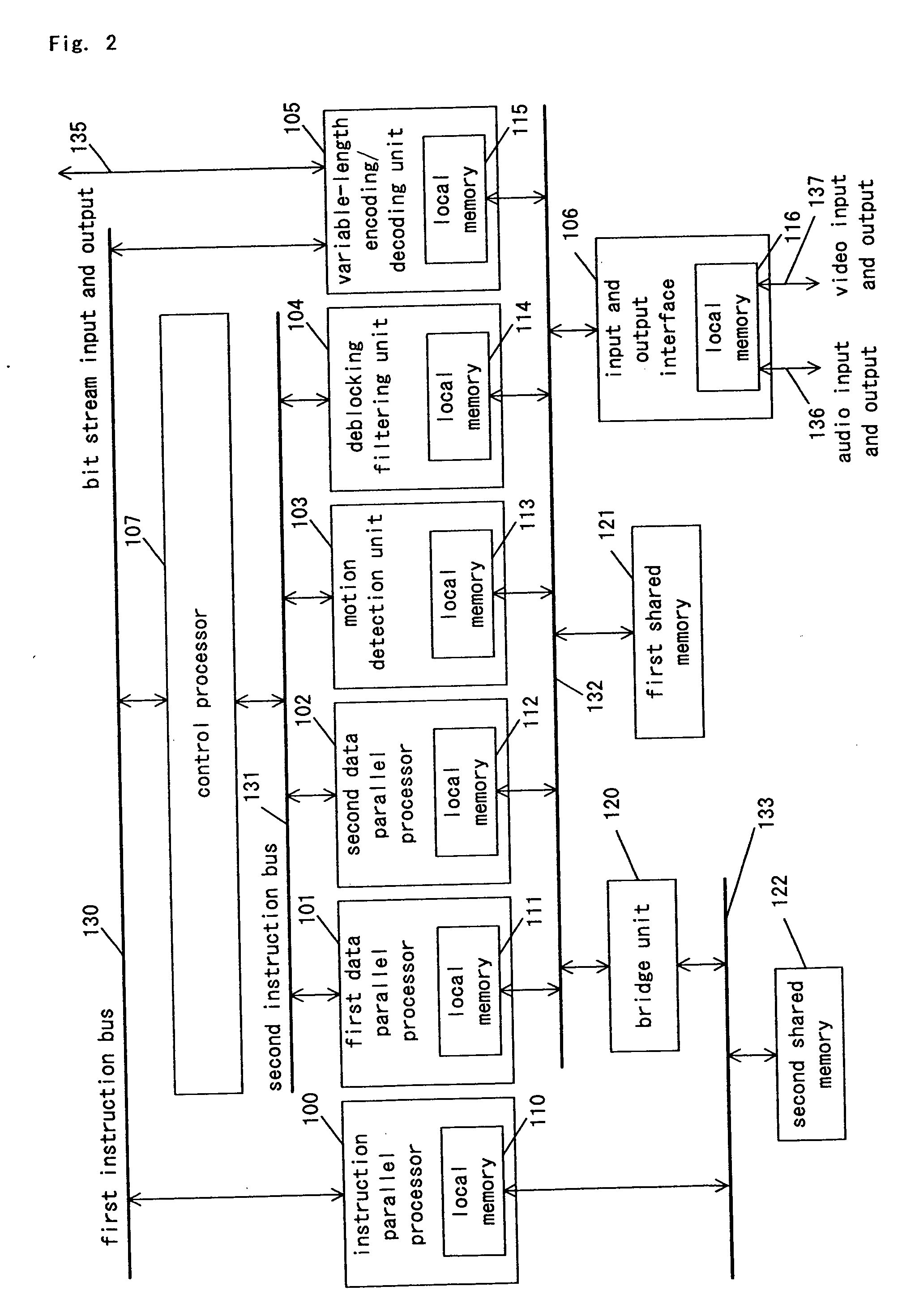

FIG. 2 is the block diagram of the signal-processing apparatus in the second embodiment of the present invention. In FIG. 2, components similar to those of FIG. 1 are denoted by the same reference numerals, and descriptions thereof are omitted.

The signal-processing apparatus of the present embodiment further comprises, compared to the signal-processing apparatus of the first embodiment, a control processor 107, a second shared memory 122, a second instruction bus 131, a second data bus 133, and a bridge unit 120 connecting the first data bus 132 and the second data bus 133.

The instruction-parallel processor 100, the control processor 107 and the variable-length coding / decoding unit 105 are connected to the first instruction bus 130.

The control processor 107, the first data-parallel processor 101, the second data-parallel processor 102, the motion detection unit 103 and the de-blocking filtering unit 104 are connected to the second instruction bus 131.

The l...

third embodiment

(Third Embodiment)

FIG. 3 is the block diagram showing a video encoder in the third embodiment of the present invention.

The video encoder of the present embodiment is an encoder capable of the MPEG-4 AVC. Each component is given a name adequately expressing a function of the video encoder corresponding to the MPEG-4 AVC.

The video encoder of the present embodiment shown in FIG. 3 comprises the signal-processing apparatus of the second embodiment. Therefore, the correspondence between the components of FIG. 3 and the components of FIG. 2 will be shown first.

The processing of a coding controller 301 and a mode switcher 303 are performed by the instruction-parallel processor 100 of FIG. 2.

The processing of a motion compensator 312 and a difference detector 302 are performed by the first data-parallel processor 101 of FIG. 2.

The processing of a 4×4 DCT transformer 304, a quantizer 305, an inverse quantizer 306, an inverse 4×4 DCT transformer 307 and a reconstructor 309 are perfo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More