Method and apparatus for infilm defect reduction for electrochemical copper deposition

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

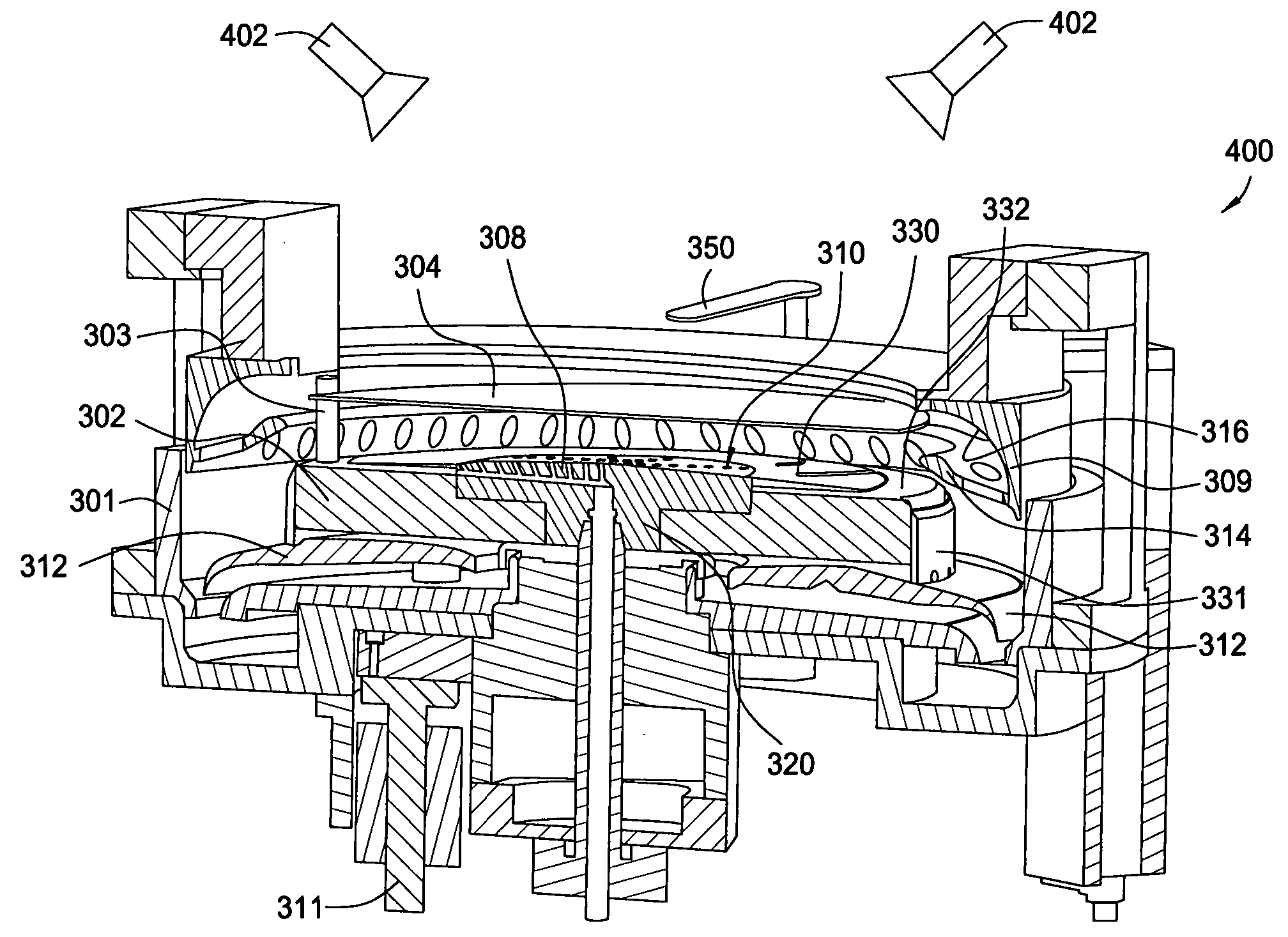

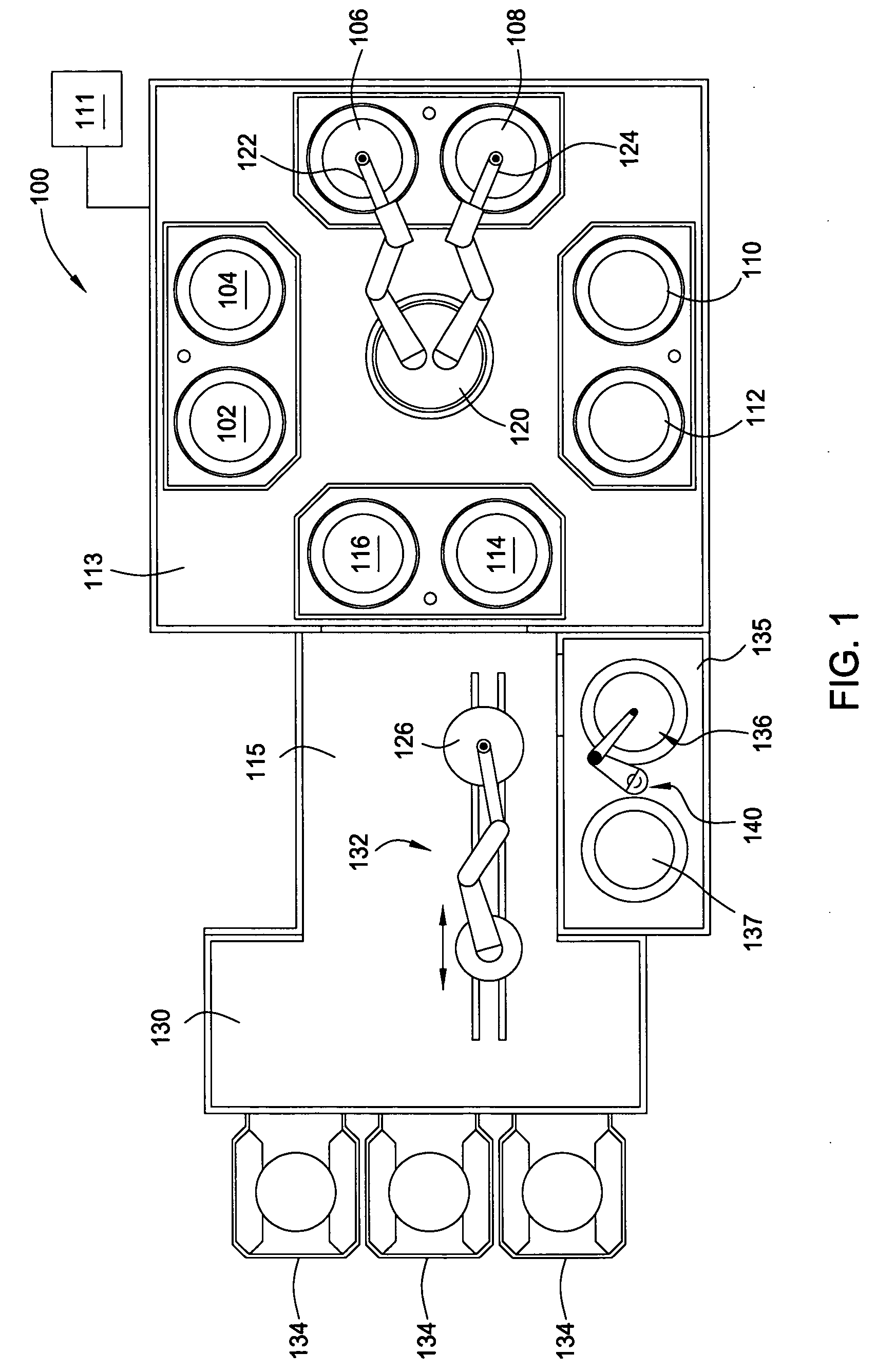

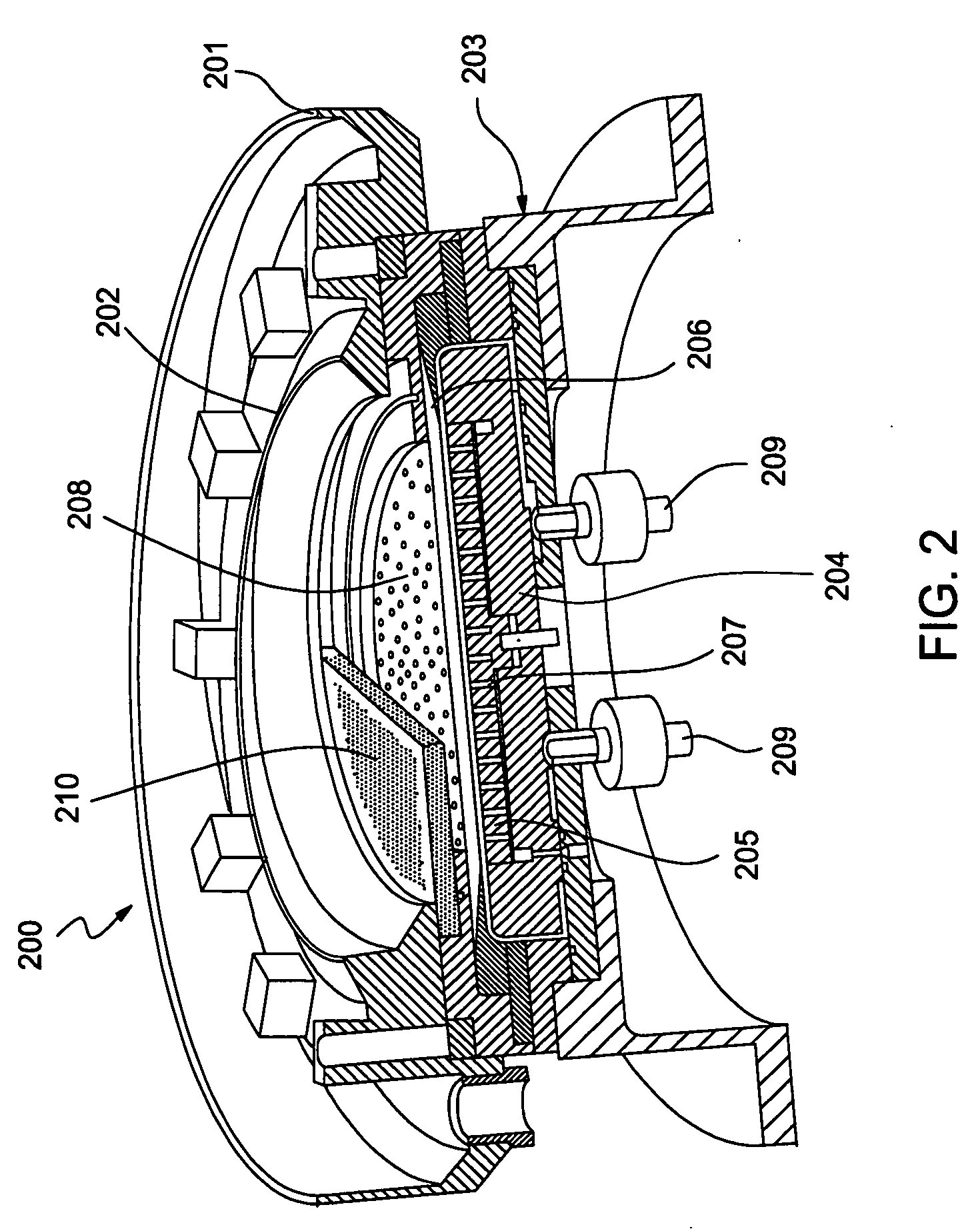

[0019] Embodiments of the invention generally provide an electrochemical plating system configured to plate conductive materials onto semiconductor substrates. The plating system generally includes a substrate loading area in communication with a substrate processing platform. The loading area is generally configured to receive substrate containing cassettes and transfer substrates received from the cassettes into the plating system for processing. The loading area generally includes a robot configured to transfer substrates to and from the cassettes and to the processing platform or a substrate annealing chamber positioned in communication with the loading area. The processing platform generally includes at least one substrate transfer robot and a plurality of substrate processing cells, i.e., ECP cells, bevel clean cells, spin rinse dry cells, substrate cleaning cells, and / or electroless plating cells.

[0020]FIG. 1 illustrates a top plan view of an exemplary ECP system 100 of the ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Temperature | aaaaa | aaaaa |

| Temperature | aaaaa | aaaaa |

| Temperature | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com