Logic circuit

a logic circuit and circuit technology, applied in the field of logic circuits, can solve the problems of requiring excessive time, requiring a large number of parts, and requiring a large number of adder circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

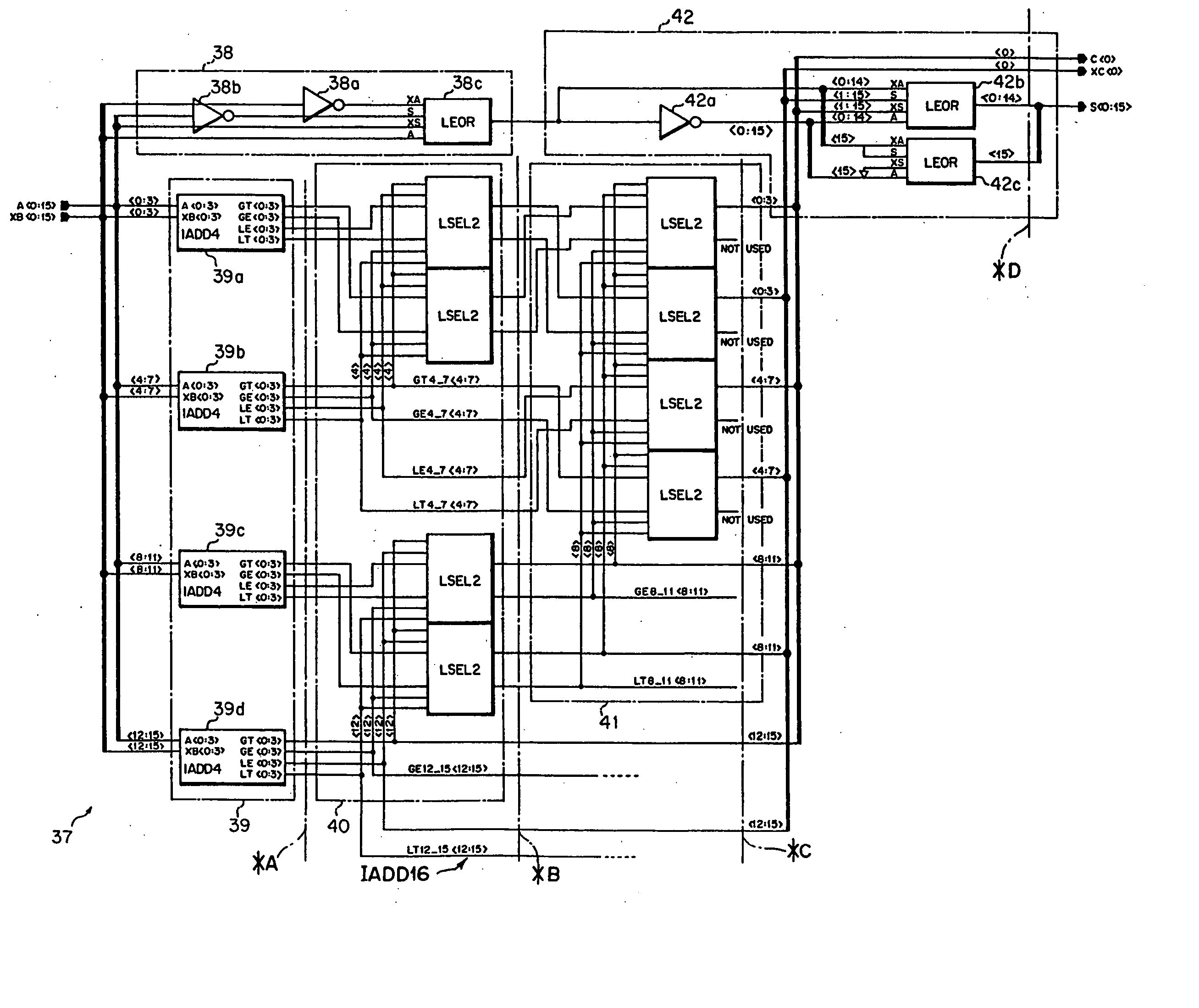

Image

Examples

first embodiment

A. First Embodiment of the Invention

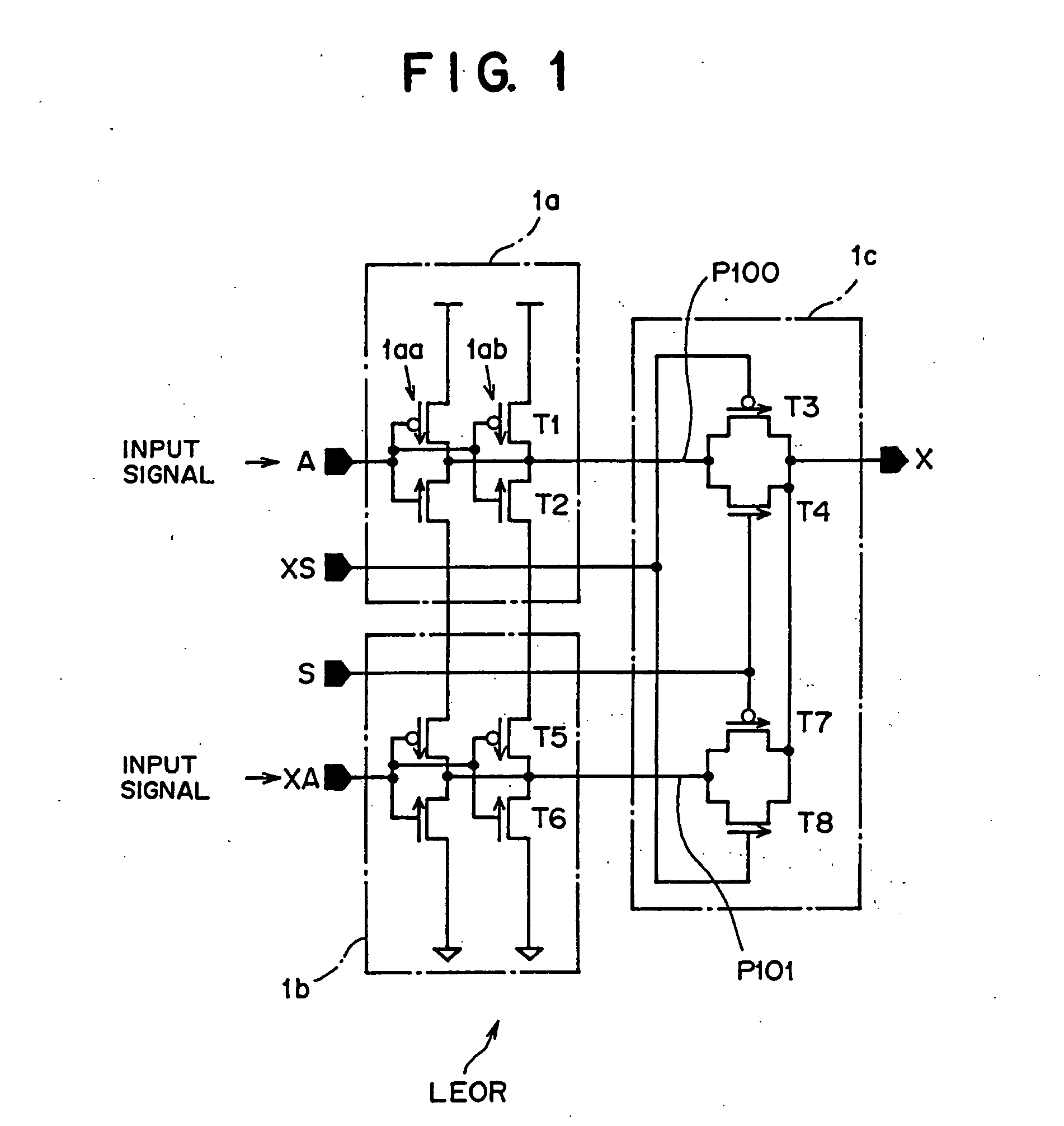

[0075]FIG. 1 is a block diagram showing a construction of a first leaf cell according to an embodiment of the present invention. Referring to FIG. 1, the cell LEOR shown is a CMOS logic circuit composed of a first inversion section 1a, a second inversion section 1b, and a transmission section 1c, and has terminals A, XS, S, XA and X.

[0076] The first inversion section 1a inverts a first input signal having one of positive logic and negative logic and outputs the inverted signal. The first inversion section 1a includes two CMOS logics 1aa and 1ab connected in parallel. A signal inputted from the terminal A is inputted to the transistor gates of the two CMOS logics 1aa and 1ab. When the input signal from the terminal A is 1, a gate T1 has an off state and a gate T2 has an on state, and a signal line P100 has a ground potential. On the other hand, when the input signal from the terminal A is 0, the gate T1 is on and the gate T2 is off, and the signal...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More