Controlling execution of a block of program instructions within a computer processing system

a computer processing system and program instruction technology, applied in the field of data processing systems, can solve problems such as adverse effects on overall performan

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

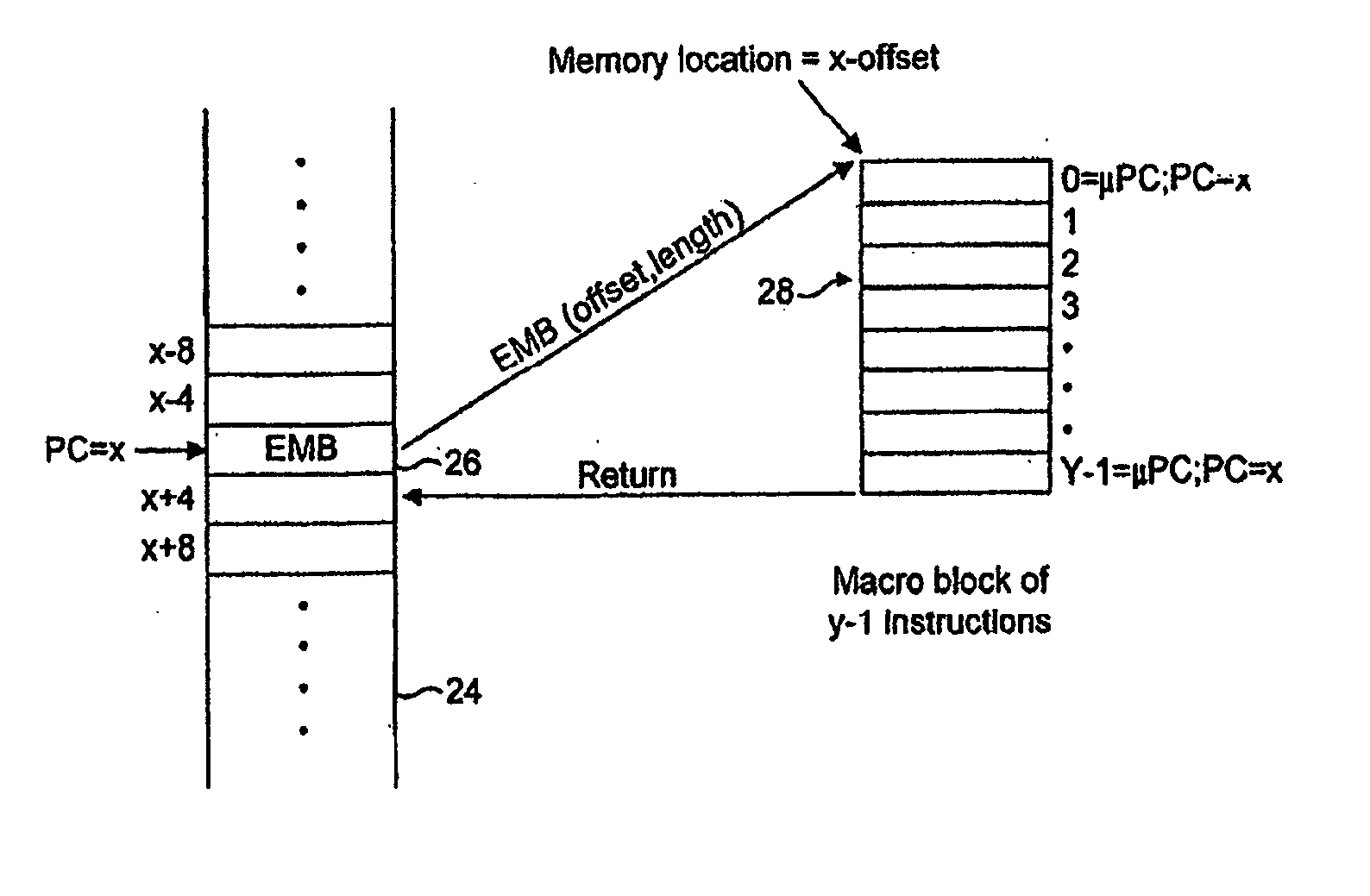

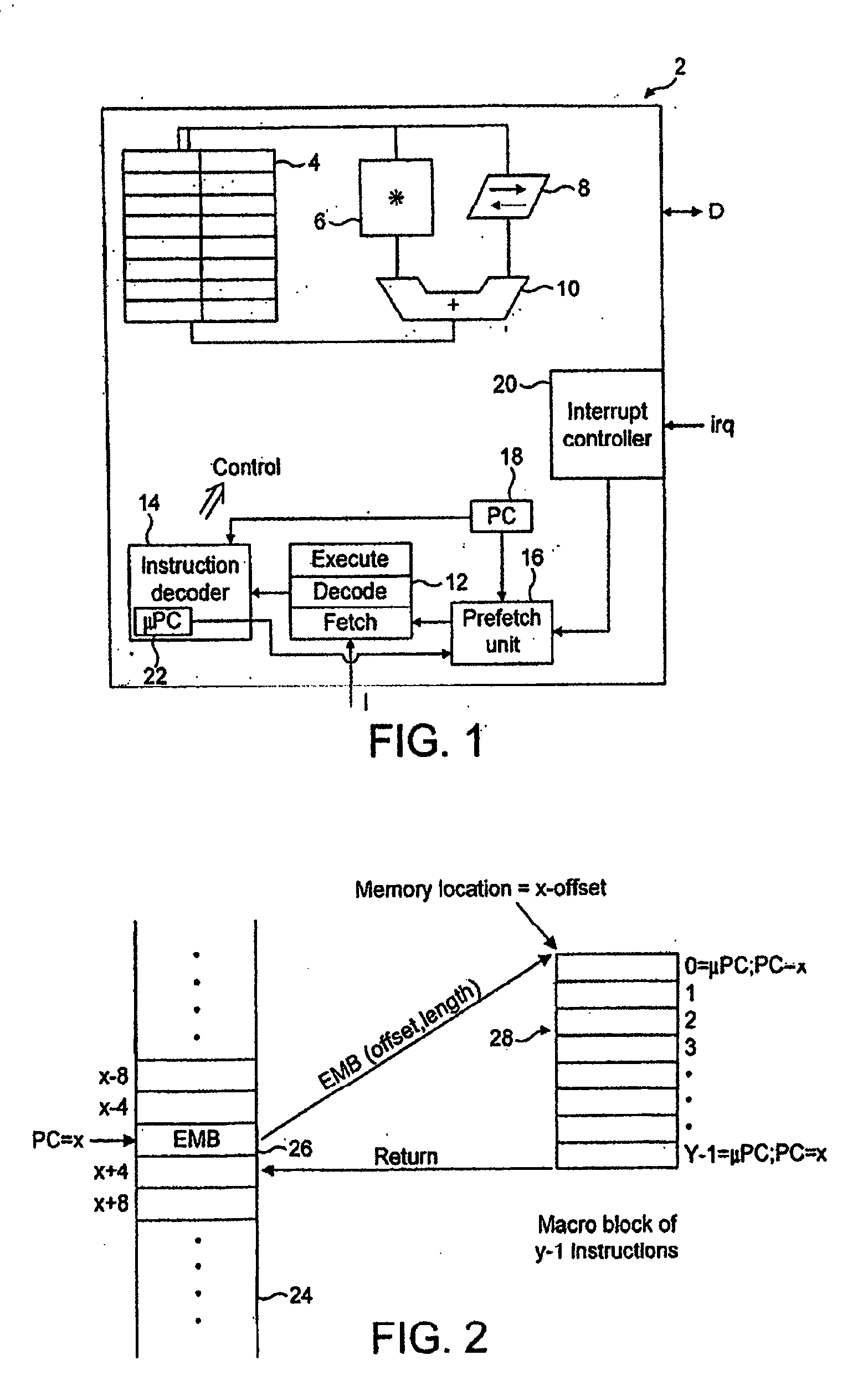

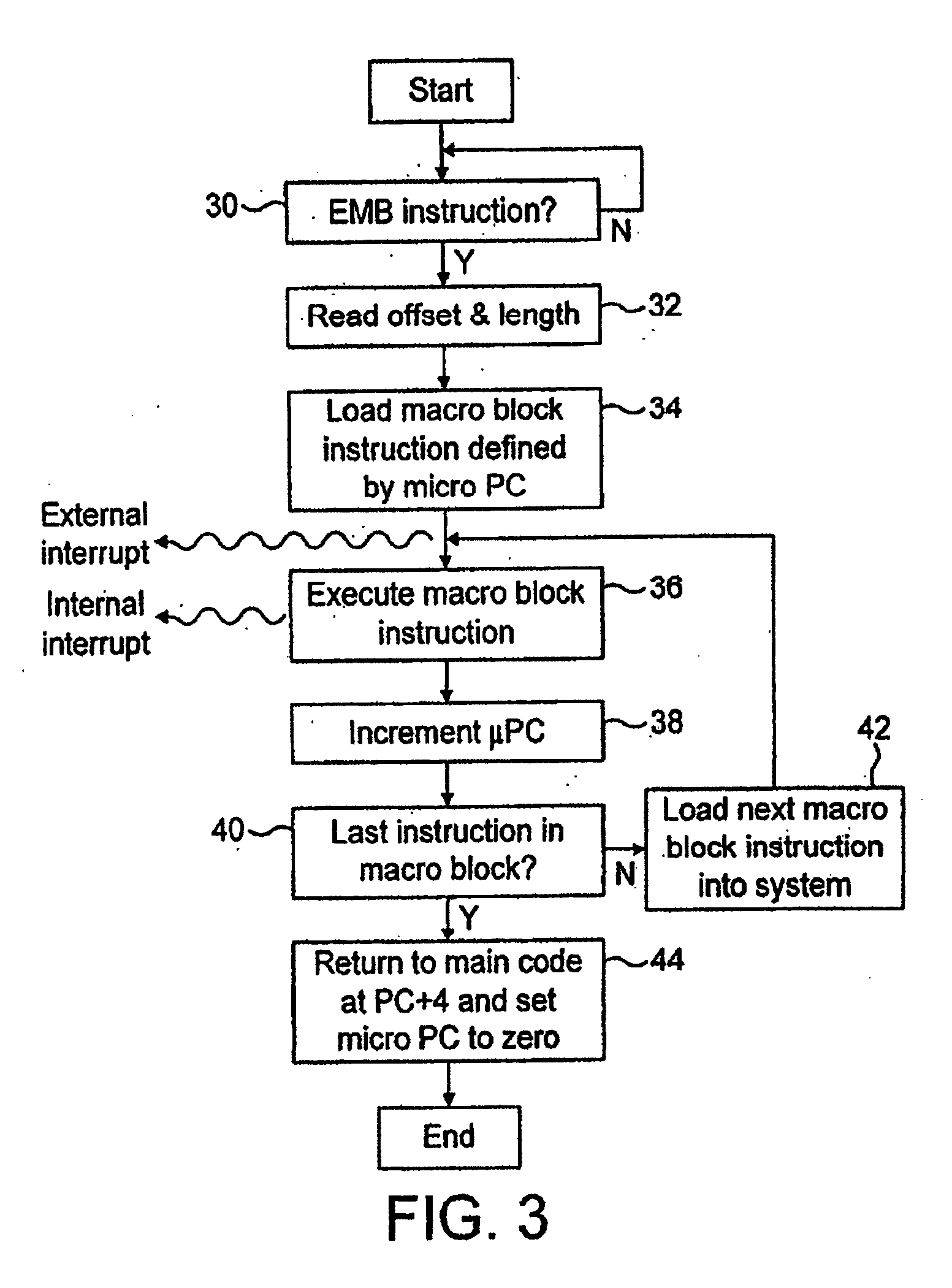

[0051]FIG. 1 shows a data processing apparatus 2 including a register bank 4, a multiplier 6, a shifter 8, an adder 10, an instruction pipeline 12, an instruction decoder 14, a prefetch unit 16, a program counter register 18 and an interrupt controller 20. It will be appreciated that the data processing apparatus 2 as illustrated in FIG. 1 will typically include many further circuit elements, but these have been omitted for the sake of clarity. In operation, instructions are fetched from a memory under control of the prefetch unit 16 and a memory location as specified in the program counter register 18 into the fetch stage of the instruction pipeline 12. The instructions progress along the instruction pipeline 12 to a decode stage and then to an execute stage in accordance with normal microprocessing techniques. The instruction decoder 14 decodes the program instructions in the decode stage and generates control signals which are used to configure the circuit elements, such as the r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More