Substrate processing apparatus

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

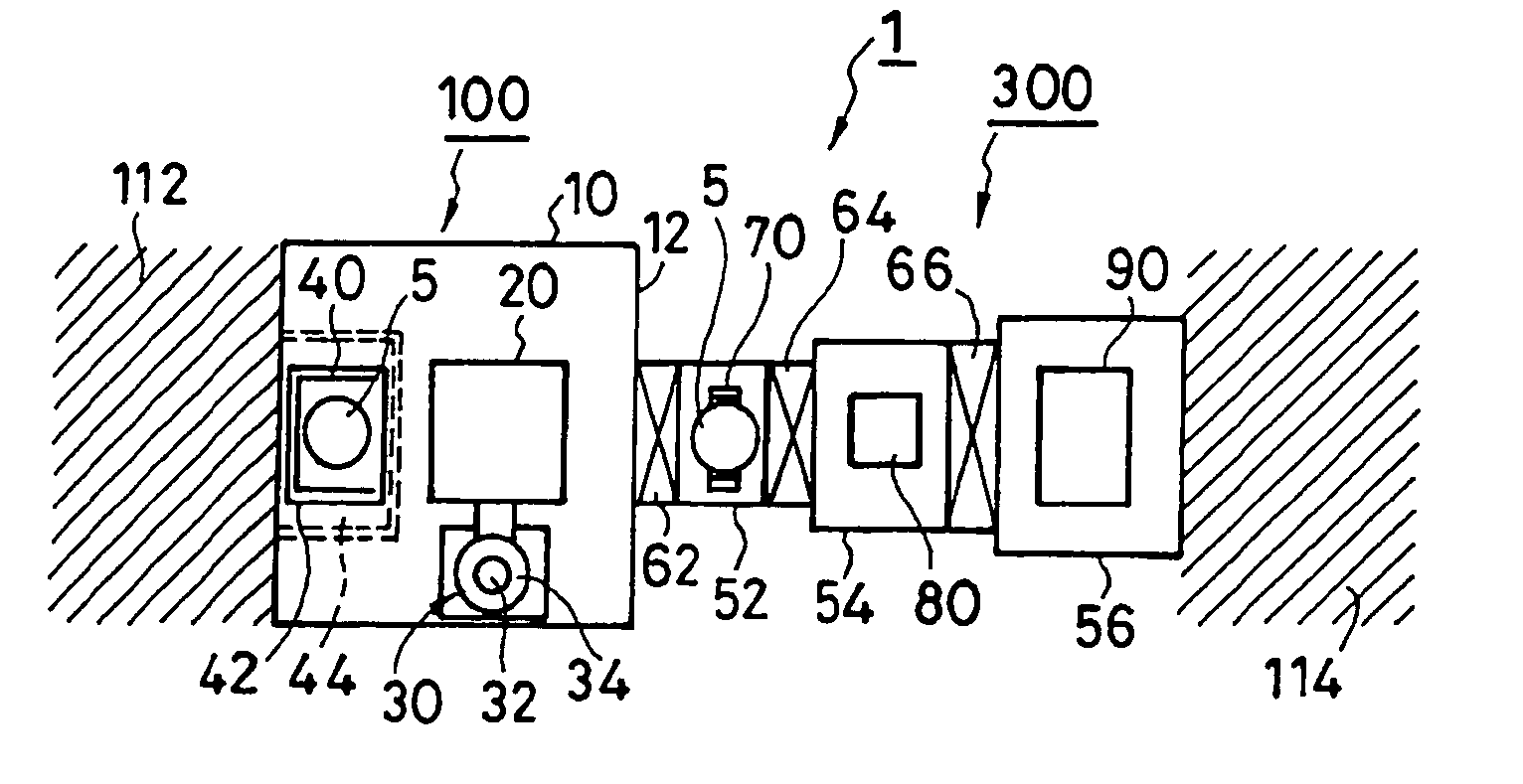

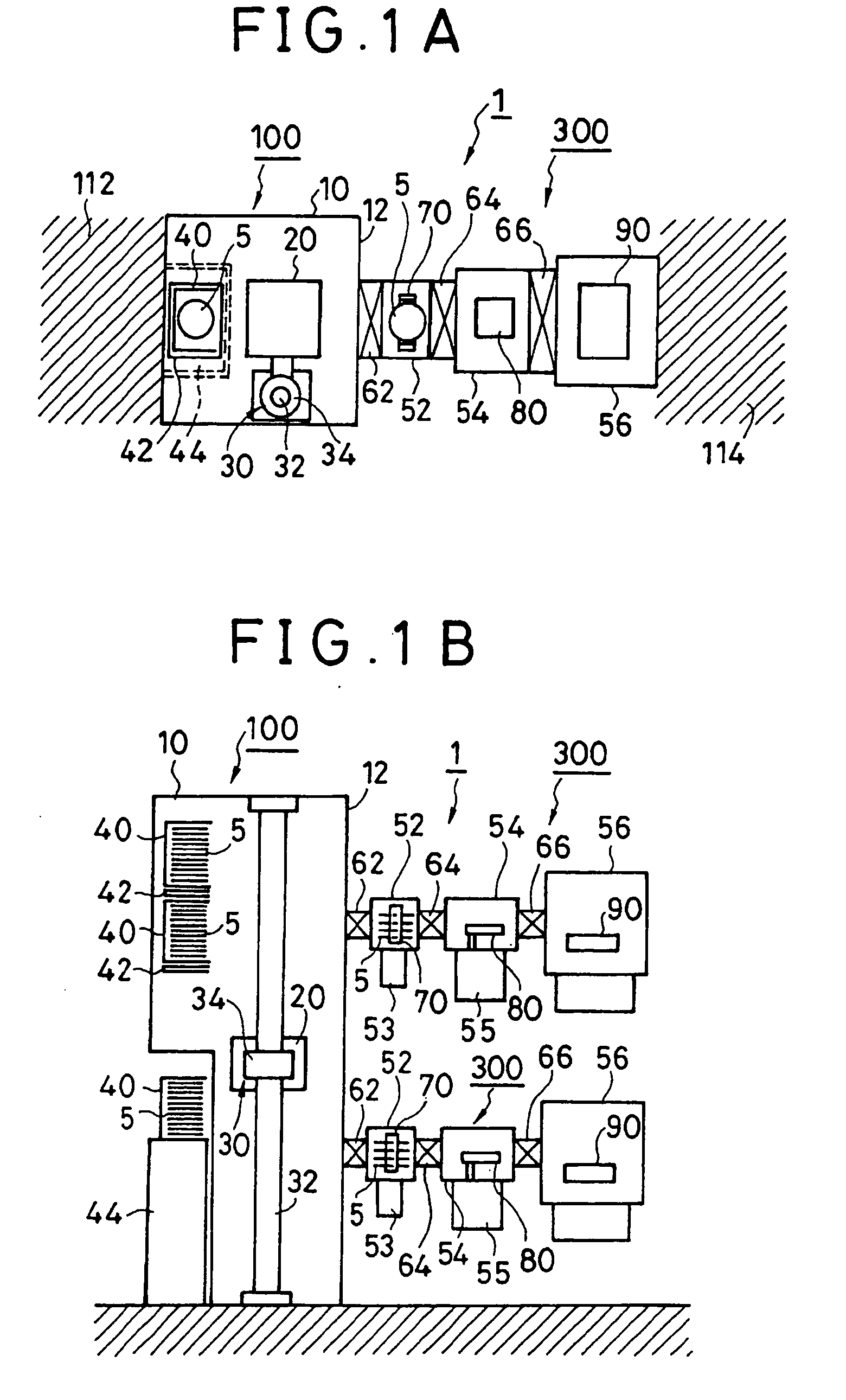

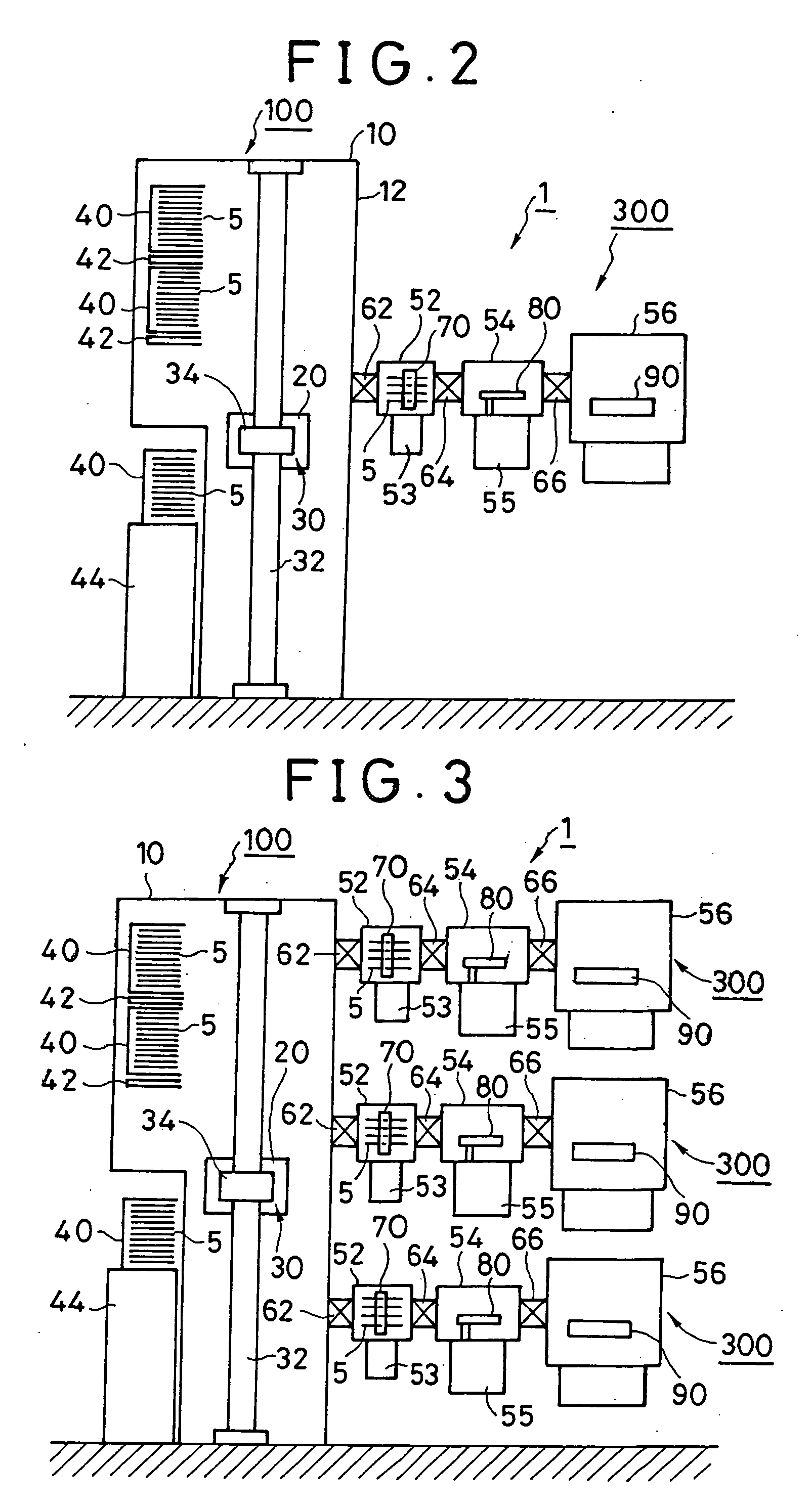

[0059] Referring to FIG. 1A to 9, a semiconductor wafer processing apparatus 1 will be explained by taking the case of a plasma CVD apparatus.

[0060] The semiconductor wafer processing apparatus 1 includes a cassette loader unit 100 and two connection modules 300.

[0061] The cassette loader unit 100 includes a cassette loader chamber 10 having a chamber wall 12 to which the two connection modules 300 are respectively detachably attached. The two connection modules 300 are piled up at a distance in a vertical direction.

[0062] Because the plurality of connection modules 300 are piled up in a vertical direction in this manner, even though the processing efficiency of the wafers 5 is enhanced by using the plurality of connection modules 300, the space occupied in a clean room by the semiconductor wafer processing apparatus 1 is not increased.

[0063] Further, maintenance areas of the semiconductor wafer processing apparatus 1 are only a maintenance area 112 at the side of the cassette l...

second embodiment

[0105]FIGS. 12A and 12B are views for explaining a semiconductor wafer processing apparatus according to the present invention, wherein FIG. 12A is a plan view and FIG. 12B is a sectional view.

[0106] In the above described first embodiment, the gate valve 64 is provided between the load lock chamber 52 and the transfer chamber 54. In the second embodiment, such a gate valve is not provided, and the wafer boat 70 and the wafer transfer robot 80 are provided in a common load lock-cum-transfer chamber 58. Other structure is the same as that of the first embodiment.

third embodiment

[0107] A third embodiment will be explained while taking the case of a plasma CVD apparatus for forming a nitride film or oxide film on a wafer, as a semiconductor wafer processing apparatus 2.

[0108]FIGS. 13A and 13B are views for explaining a semiconductor wafer processing apparatus according to the third embodiment of the invention, wherein FIG. 13A is a plan view, and FIG. 13B is a sectional view. FIGS. 14 and 15 are sectional views and FIGS. 16 to 19 are plan views, all for explaining the semiconductor wafer processing apparatus of the third embodiment.

[0109] The semiconductor wafer processing apparatus 2 comprises: a cassette loader unit 100 in which the elevator 30 and the cassette transferring-cum-wafer transferring robot 20 capable of transferring the wafers 5 vertically and horizontally; gate valves 462 and 464 for opening and closing a gate of each of connection modules 400; a load lock-cum-transfer chamber 452 which is provided therein with a wafer transfer robot 480 for...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More