Self-aligned complementary ldmos

a complementary, self-aligning technology, applied in the direction of semiconductor devices, electrical equipment, transistors, etc., can solve the problem of increasing rdson

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

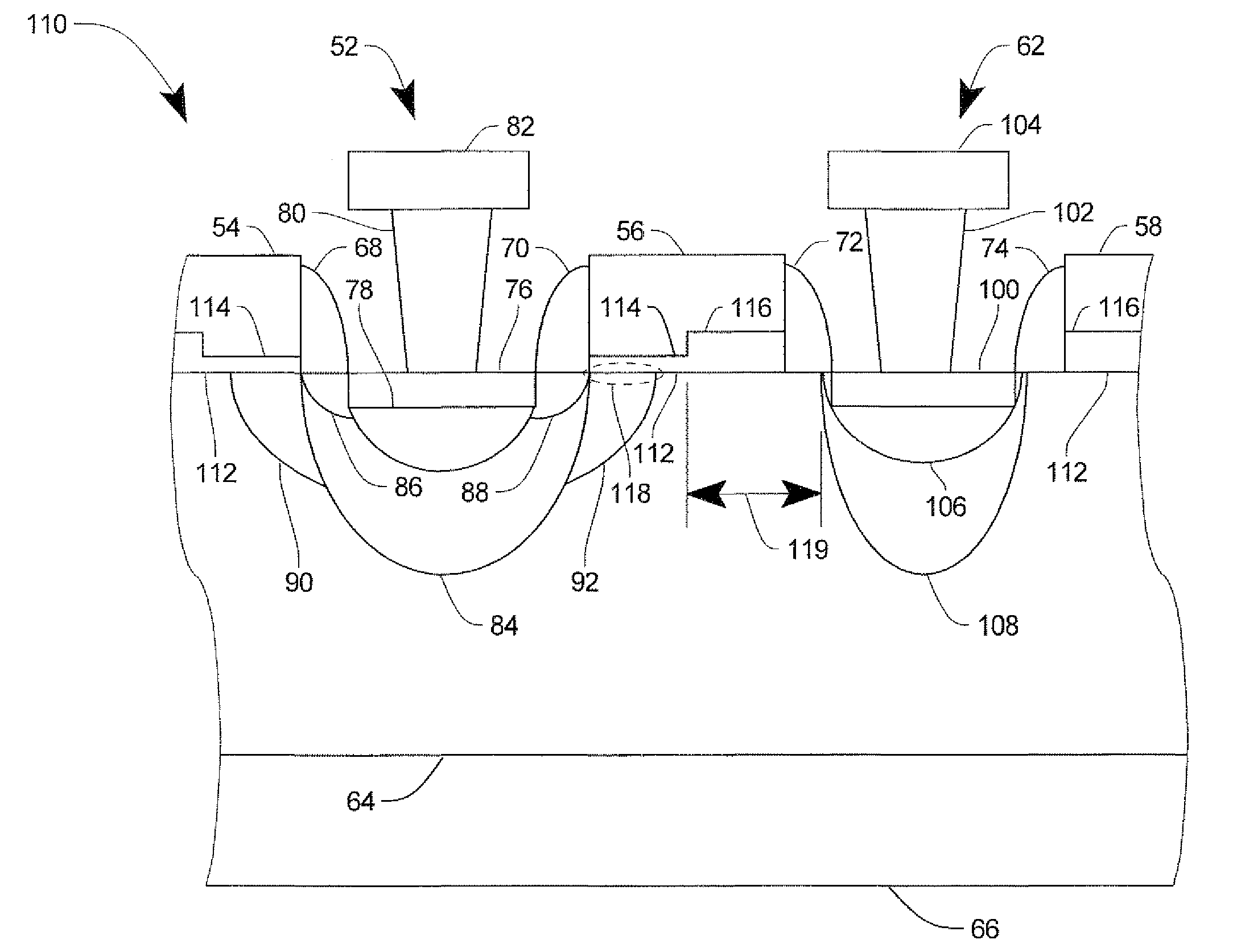

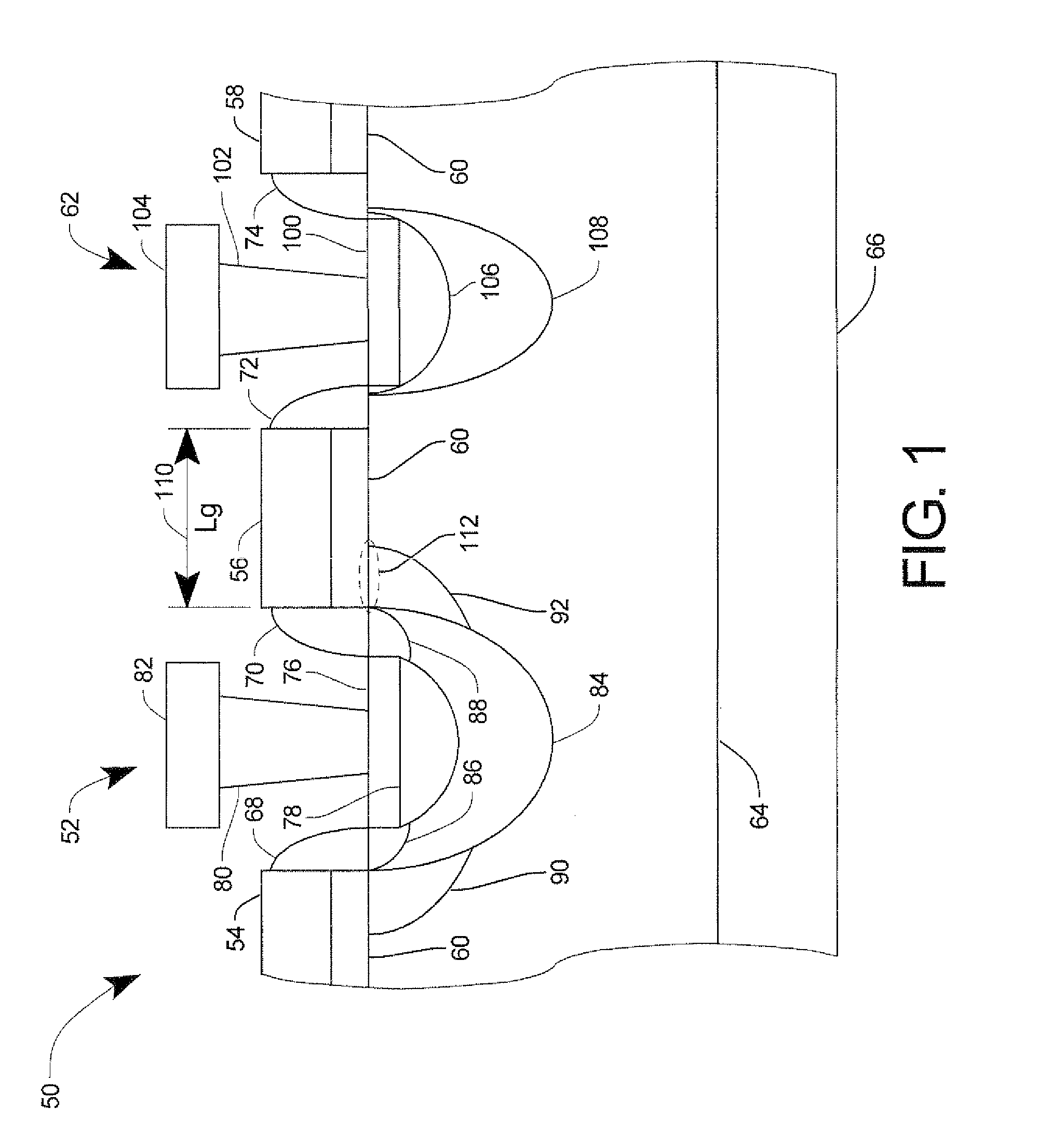

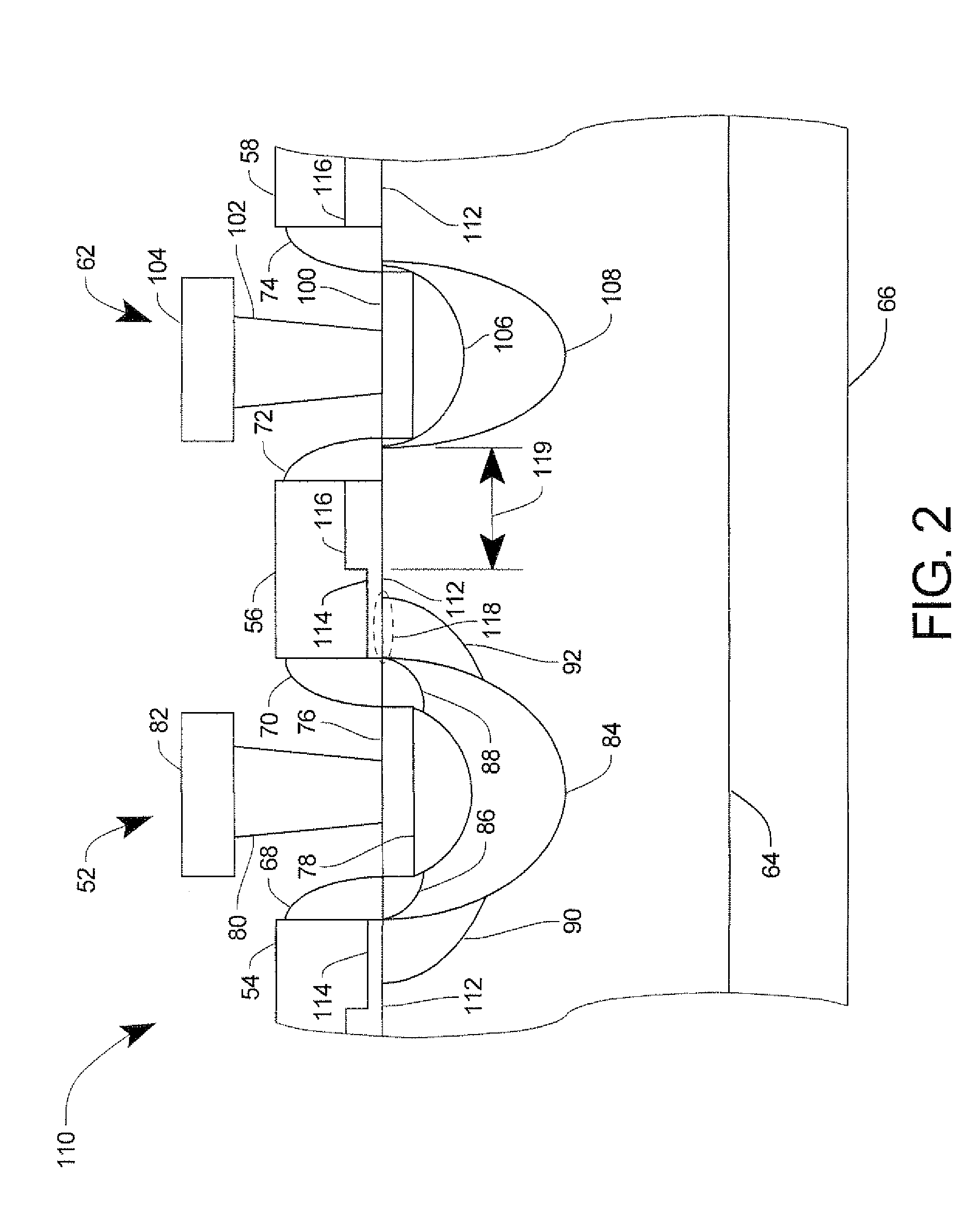

[0047]Referring to FIG. 1, there is shown an n-type embodiment 50 of a fully self-aligned complementary LDMOS device according to one embodiment of the present invention. As shown in FIG. 1 the LDMOS device 50 is a multiple gate device. The LNDMOS 50 includes a source 52, three gates 54, 56, and 58 each having a thick gate oxide 60, and a drain 62. The gate 56 is between the source 52 and the drain 62, while the gate 54 is on the opposite side of the source 52, and the gate 58 is on the opposite side of the drain 62. The source 52 and drain 62 are formed in a high voltage HV NWELL 64. Under the HV NWELL 64 may be another layer 66 which may be an N buried layer or an N isolation layer, built in a P type substrate, depending on the use of the LDMOS 50, such as whether the LDMOS 50 is integrated in a low voltage CMOS platform and if the LDMOS 50 is subjected to relatively high voltages from the source and drain to the substrate compared to lower voltage devices or LDMOS device 50 with ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More