Integrated Circuit Package and a Method for Forming an Integrated Circuit Package

a technology of integrated circuits and components, applied in the direction of electrical equipment, semiconductor devices, semiconductor/solid-state device details, etc., can solve the problems of limiting the improvement that can be achieved, the moisture resistance of the package is increased, and the electrical connection between the chip and the substrate is not working properly, so as to reduce the mechanical strength of the assembly, improve the moisture resistance of the package, and reduce the performance of the underfill layer. effect of function

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

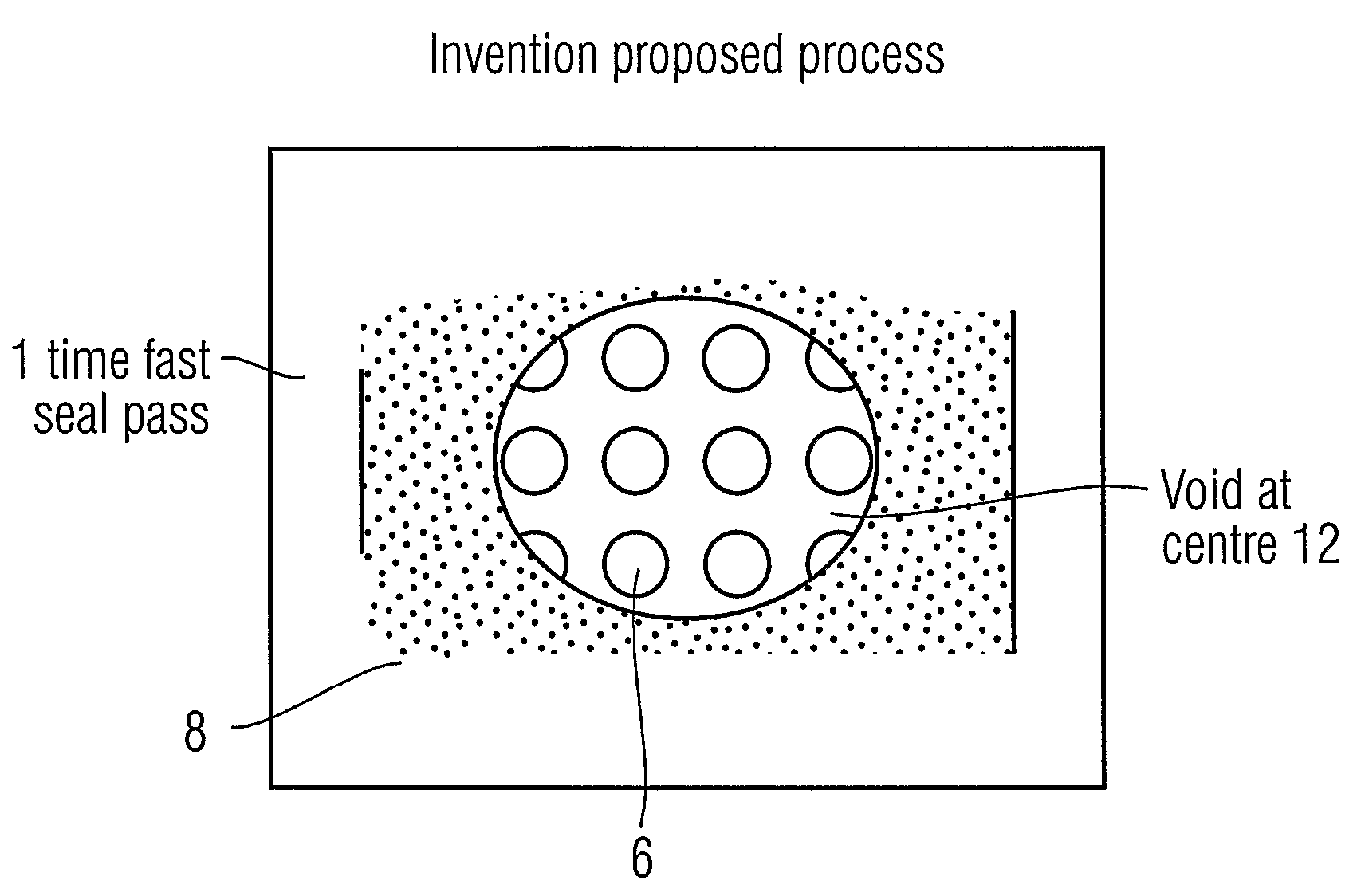

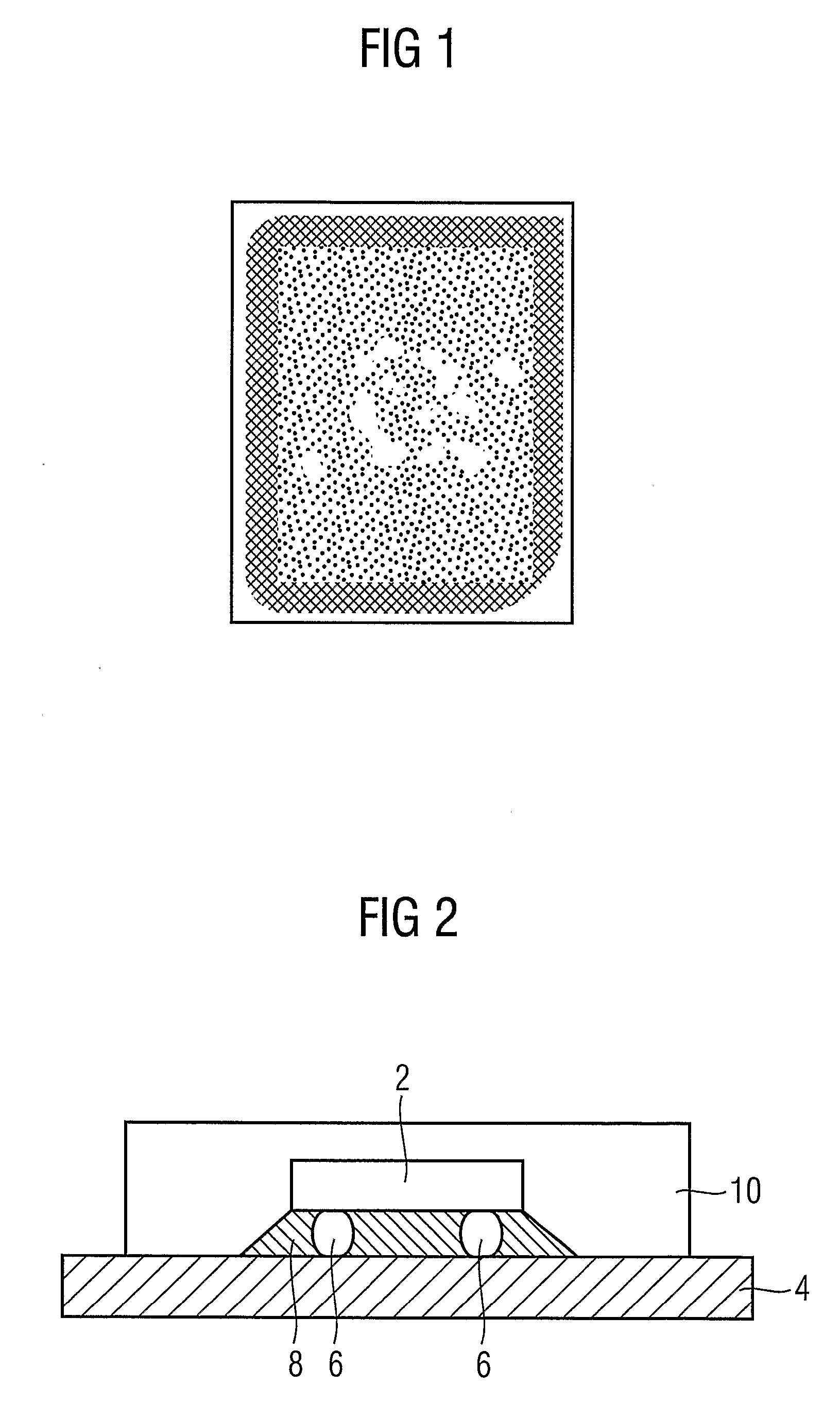

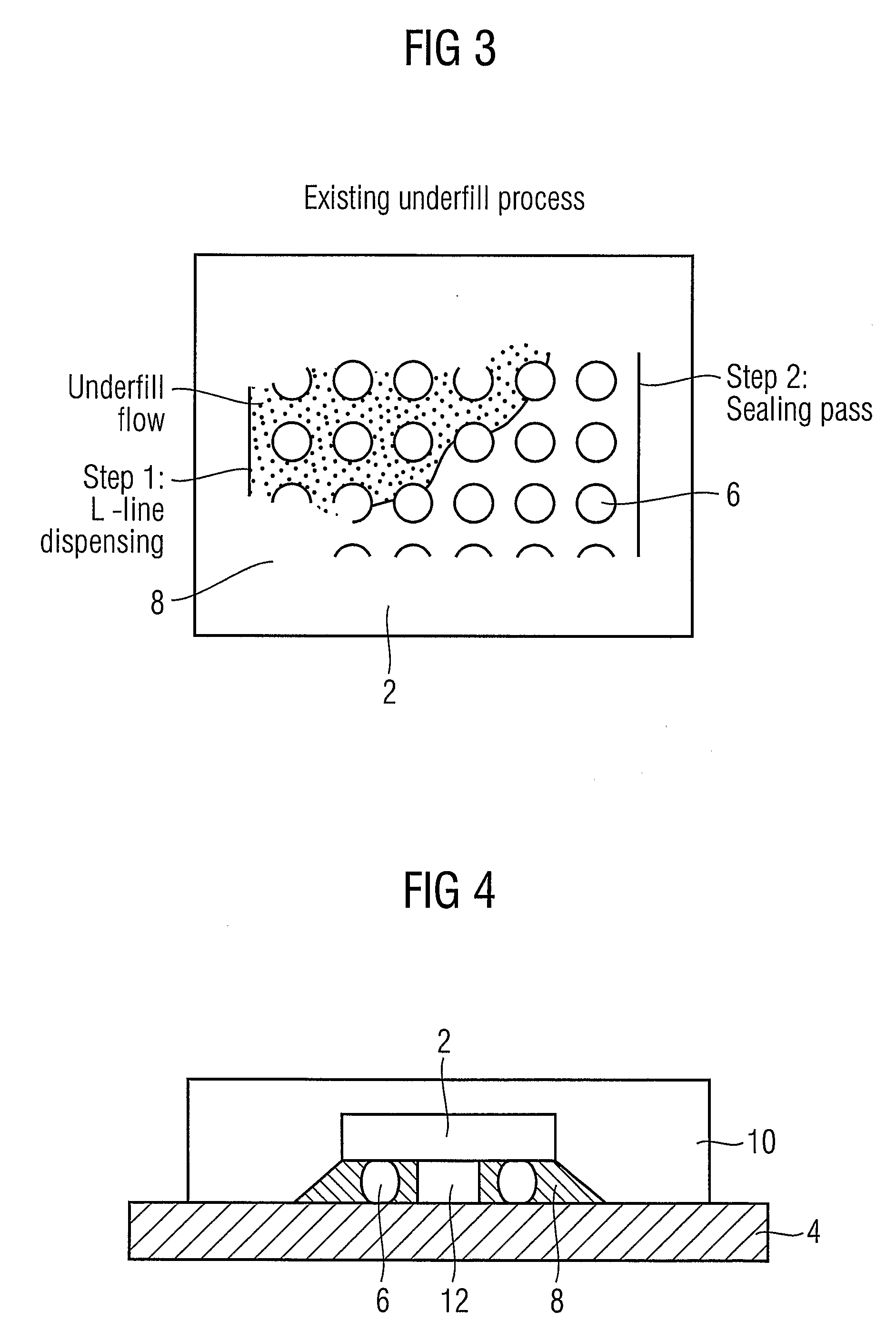

[0022]A conventional Flip Chip package will be described with respect to FIGS. 2 and 3.

[0023]As shown in the cross-section of FIG. 2, a chip 2 is mounted on a substrate, carrier or circuit board 4 by means of conductive bumps 6. In a typical example, the bumps 6 are formed by sputtering, plating or printing a solderable material on the chip 2, and these are connected and soldered to chip bond pads provided on the substrate 4.

[0024]A non-conductive underfill layer 8 is provided under the chip 2. As can be seen in FIG. 2, the underfill material surrounds the bumps 6, and fills the entire region underneath the chip between the chip and the substrate. Typically the underfill extends beyond the outer periphery of the chip. It is typical to provide the underfill material by dispensing the material along one or two sides of the periphery of the chip, allowing the material to flow under the chip to fill the area between the chip and substrate. Where material is deposited along one side only...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More