Chip package structure and method of fabricating the same

a chip and package technology, applied in the direction of solid-state devices, basic electric elements, electric devices, etc., can solve the problems of increasing the additional manufacturing cost of the lead frame, the mask required in the photolithography process of patterning the lead frame, etc., to save the production cost of the chip package structure and reduce packaging costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

second embodiment

[0053]FIG. 6 is a schematic cross-sectional view of a chip package structure according to a second embodiment of the present invention. It should be noted that the same or similar reference numbers used in the second embodiment and in the first embodiment represent the same or the like elements, and the second embodiment is approximately identical to the first embodiment. The difference between the two embodiments will be described hereinafter, and the similarities therebetween are omitted.

[0054]Referring to FIG. 6, the difference between the second embodiment and the first embodiment lies in that a second protrusion part 514 of a metal thin plate 510 has a down-set design in a chip package structure 500. That is to say, an upper surface 510a of the second protrusion part 514 is lower than the upper surface 510a of a first protrusion part 212 and the upper surface 510a of a plurality of third protrusion parts 216. After a lead frame 510′ of the metal thin plate 510 is formed, and th...

third embodiment

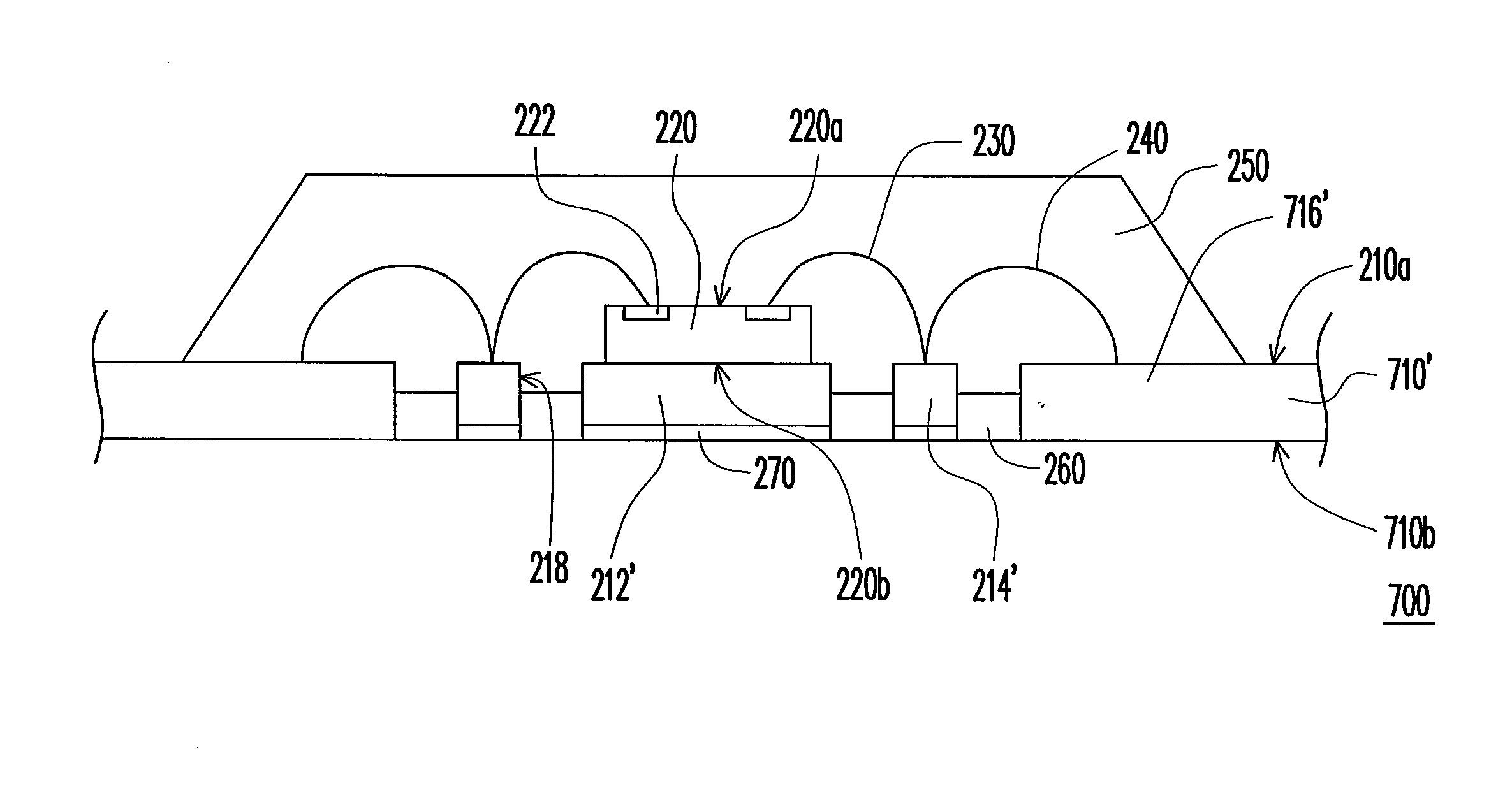

[0055]FIG. 7 is a schematic cross-sectional view of a chip package structure according to a third embodiment of the present invention. It should be noted that the same or similar reference numbers used in the third embodiment and in the first embodiment represent the same or the like elements, and the third embodiment is approximately identical to the first embodiment. The difference between the two embodiments is described hereinafter, and the similarities therebetween are omitted.

[0056]Please refer to FIG. 7. The difference between the third embodiment and the first embodiment lies in that a thickness of a die pad 612′ exceeds the thicknesses of a bus bar 214′ and of a plurality of leads 216′ in a lead frame 610′ of a chip package structure 600. And an upper surface 210a of the die pad 612′ is coplanar with the upper surface 210a of the bus bar 214′ and the upper surface 210a of the leads 216′. After the fabrication of the chip package structure 600 is basically completed, an etch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More