Thin body silicon-on-insulator transistor with borderless self-aligned contacts

a silicon-on-insulator transistor and self-aligning technology, applied in the field of thin body field-effect transistors with electrical contacts, can solve the problems of inoperable devices, considerable challenge in electrical contact formation,

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

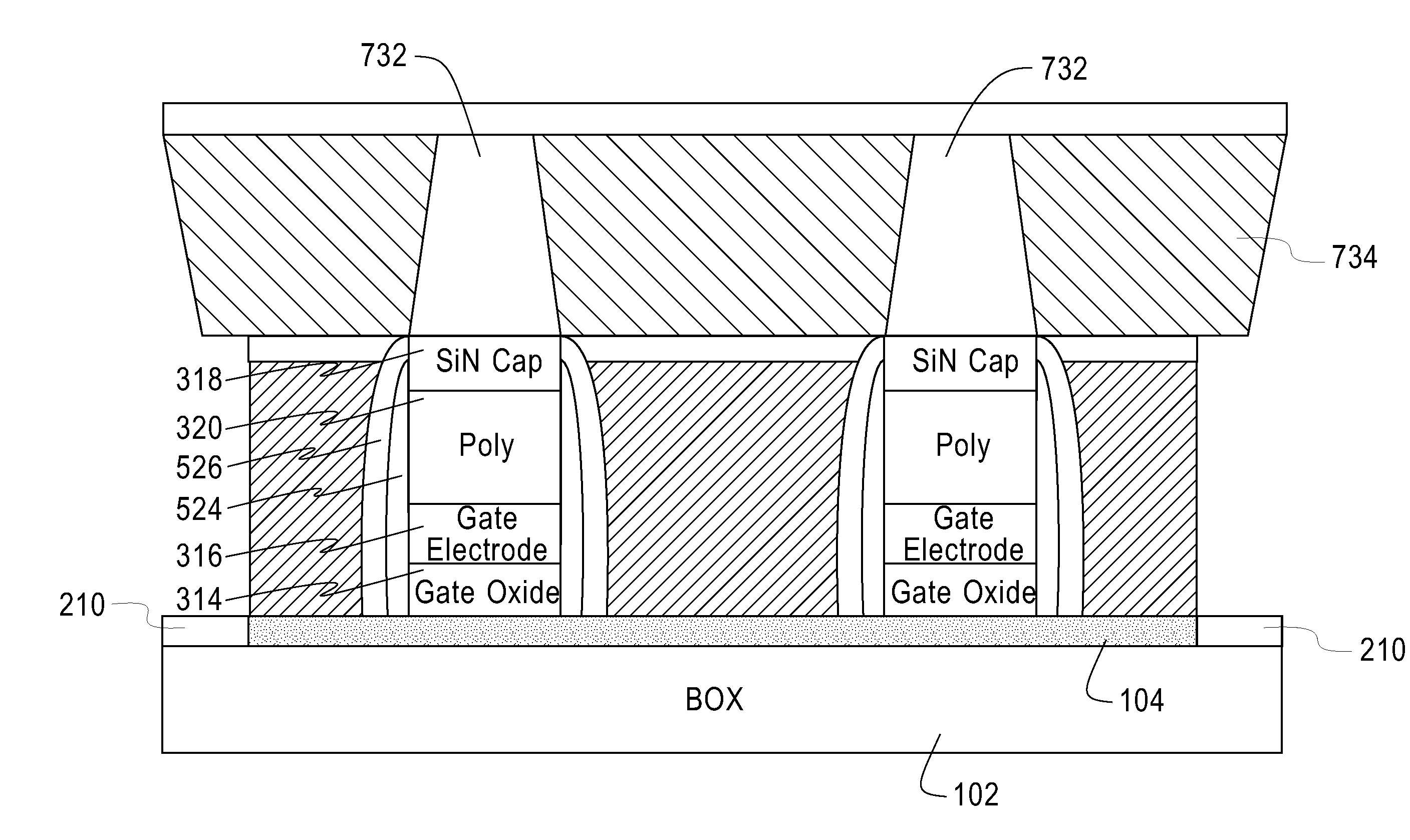

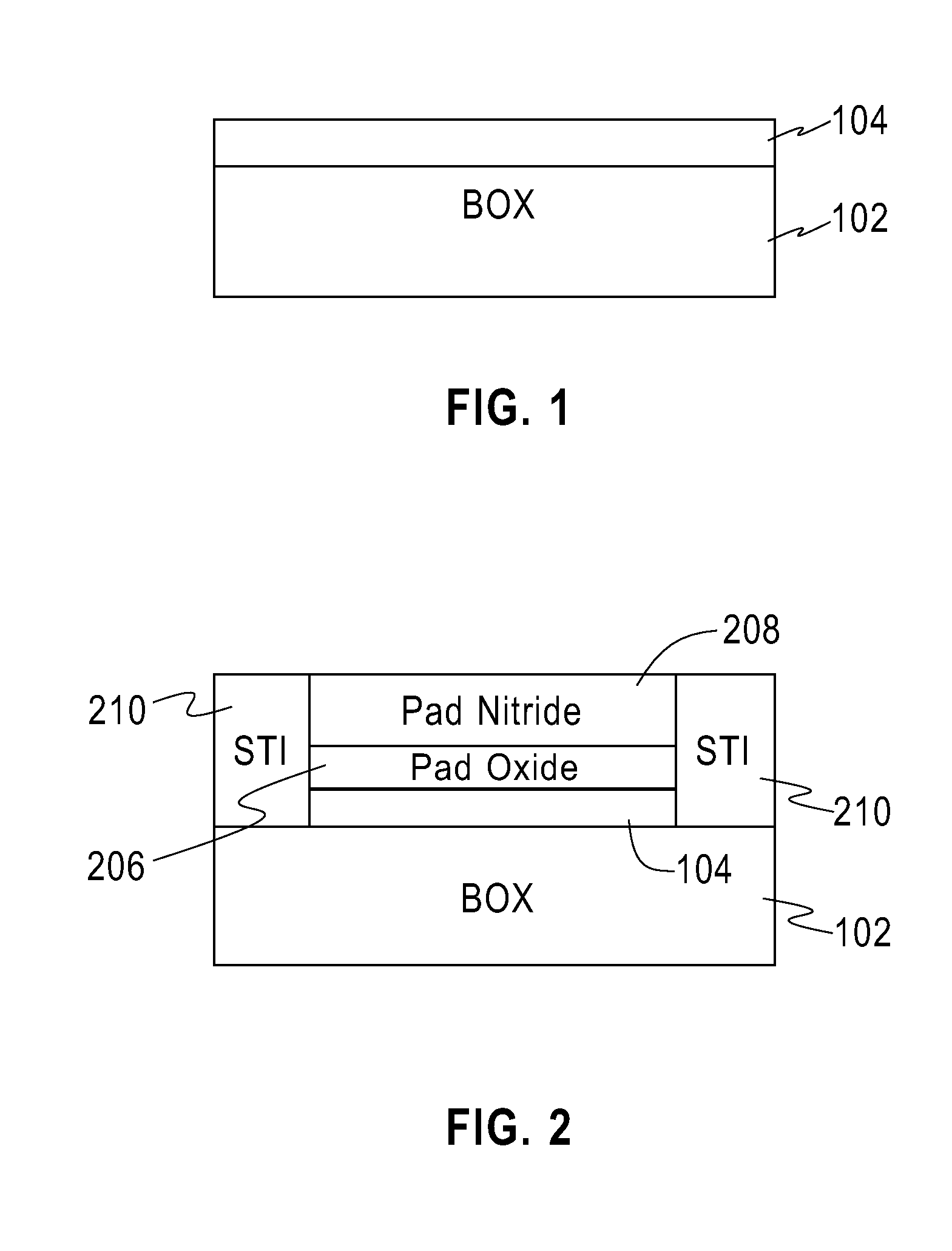

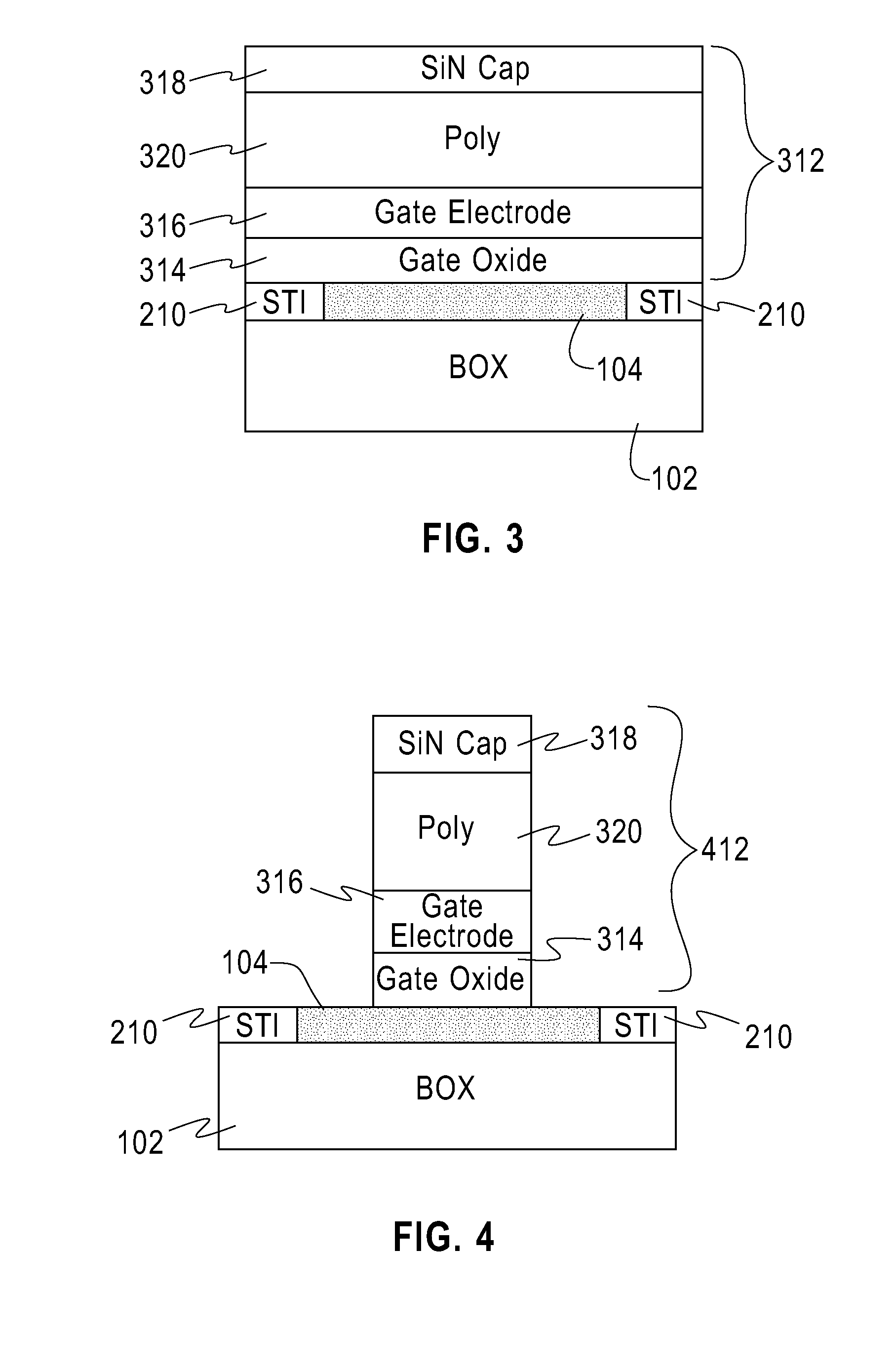

[0008]Embodiments of the present invention provide thin silicon-on-insulator field-effect transistors with borderless self-aligned electrical contacts. Contacts that are self aligned to the source and drain are highly desirable to overcome the misalignment problem discussed above. Generally, an epitaxial layer of Si is grown in the source and drain region of thin body devices, often referred to as a raised source drain (“RSD”). The RSD lowers the external resistance of the device by mitigating the so called “current crowding” effect. It simultaneously provides the requisite volume of Si to form a silicide without fully siliciding the source and drain. The RSD causes an increased capacitance from the source and drain to the gate. This capacitance is present regardless of the gate height.

[0009]However, various embodiments of the present invention provide an advantageous method for forming self-aligned borderless contacts to thin body FET devices. These contacts are formed by the epita...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More