High temperature bd development for memory applications

a memory application and high temperature technology, applied in the direction of coatings, chemical vapor deposition coatings, metallic material coating processes, etc., can solve the problems of dielectric films outgasping volatile species and shrinking, and achieve the effect of increasing the flow rate of one or more organosilicon compounds

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

examples

[0050]Organosilicate dielectric layers were deposited on a substrate in accordance with the embodiment described above with respect to FIG. 5. The films were deposited using a PECVD chamber (i.e., CVD chamber) on a PRODUCER system, available from Applied Materials, Inc. of Santa Clara, Calif. During deposition the chamber pressure was maintained at a pressure of about 4.5 Torr and the substrate was maintained at a temperature of about 350° C.

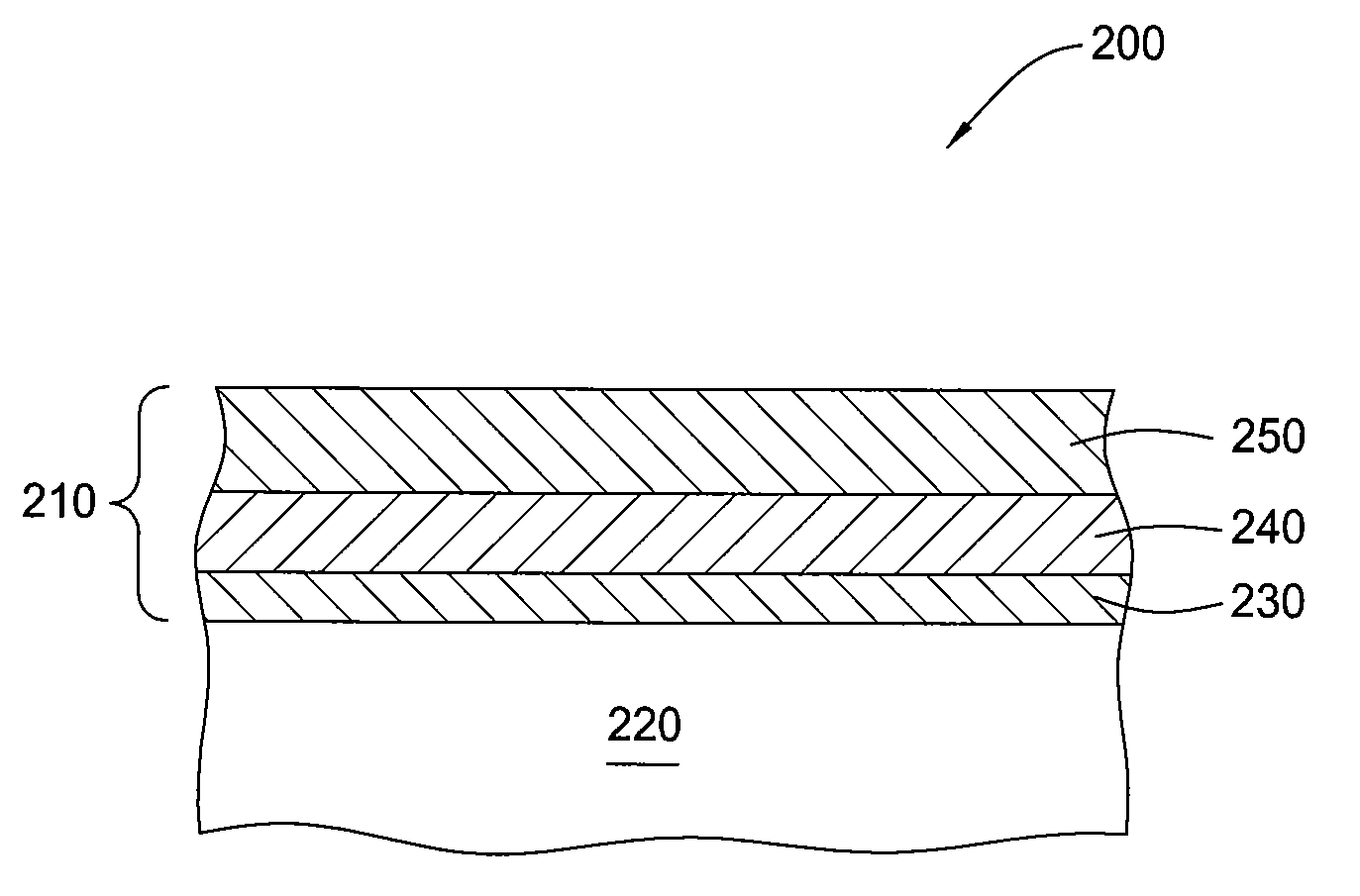

[0051]The substrate was positioned on a substrate support disposed within a process chamber. The process gas mixture having an initial gas composition of 1000 sccm helium and 700 sccm oxygen for the interface layer was introduced into the chamber and flow rates stabilized before initiation of the HFRF power. Subsequently, HFRF power of about 500 W was applied to the showerhead to form a plasma of the interface process gas mixture composition including a OMCTS flow rate of about 700 mg / min., and deposit a silicon oxide layer having a carbon conte...

PUM

| Property | Measurement | Unit |

|---|---|---|

| temperature | aaaaa | aaaaa |

| dielectric constant | aaaaa | aaaaa |

| temperature | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More