Virtual Memory Management System with Reduced Latency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

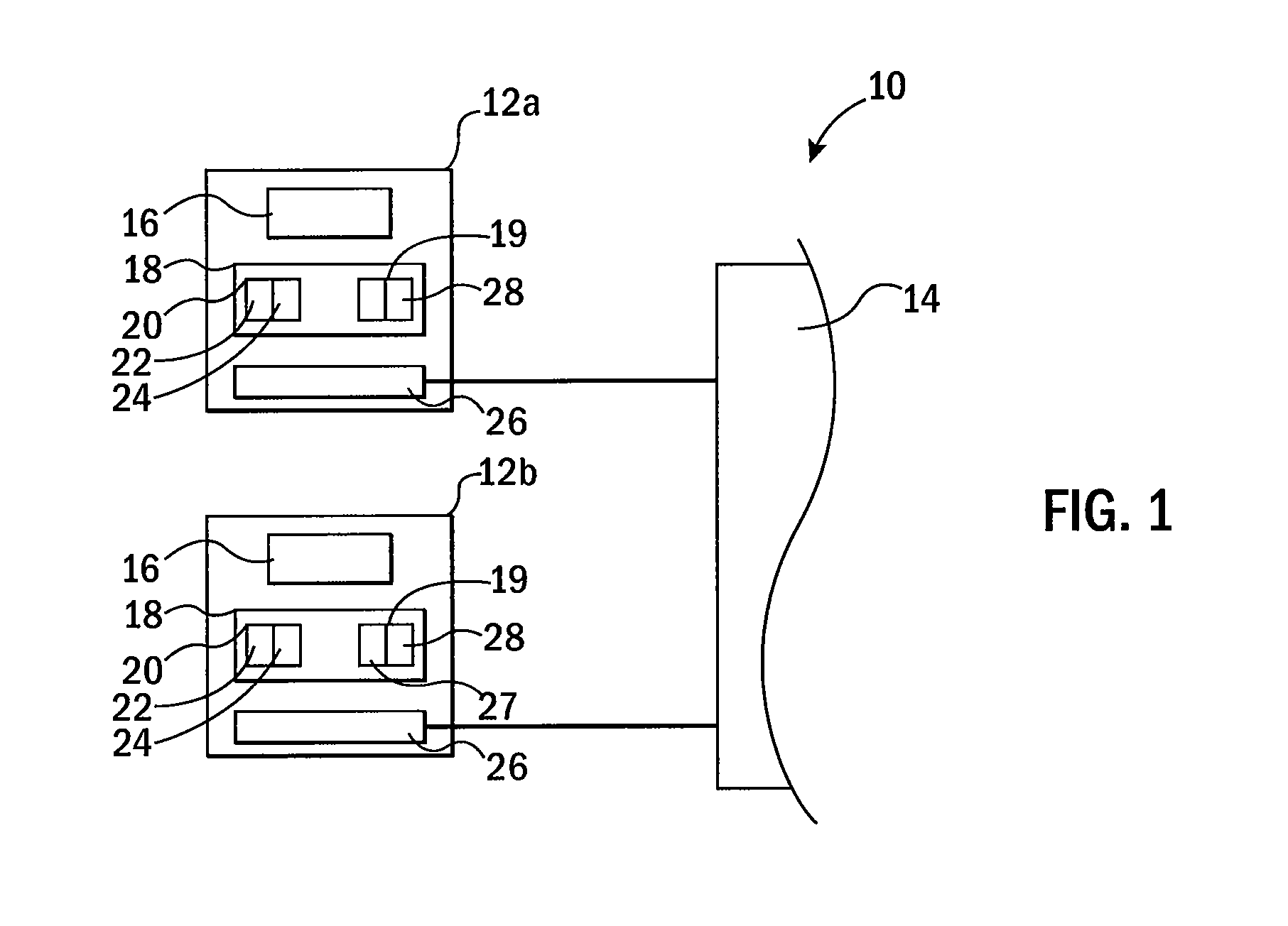

[0036]Referring now to FIG. 1, a multiprocessor computer system 10 suitable for practice of the present invention may include one or more processors 12a and 12b communicating with a memory system 14, the latter including, for example, physical memory and one or both of solid-state and disk storage devices.

[0037]Each processor 12 may include a processor unit 16 for executing instructions of programs (for example read from the memory system 14) to operate on data read from the memory system 14 which provides argument to instructions of programs. This execution of the instructions then produces data values which may be written to the memory system 14. The different processors 12a and 12b may execute the same or different programs and each program may include multiple processes, individual or multiple of which may be executed by a given processor 12.

[0038]Access to the memory system 14 by the processor unit 16 is mediated through a memory access circuit 18 in turn communicating with a c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More