Method and apparatus for data capture in DDR memory interface

a technology of ddr memory interface and data acquisition, applied in the direction of information storage, static storage, digital storage, etc., can solve the problems of difficult to capture the correct data signal, substantial jitters and/or on-chip variations, and undesirable effects, so as to reduce the circuit area and/or power

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035]The present disclosure relates to a unique technique of reading of data (DQ) bits in a memory system by an SDRAM controller from a memory, such as a DDR memory that avoids jitters and on-chip variations, which, in turn, reduces the timing margins. According to one or more embodiments described hereinafter, the DDR memory and the SDRAM controller, along with SDRAM PHY have been described as independent devices in the memory system; however, one of ordinary skill in the art would appreciate that they may be on a single chip or on a plurality of independent chips that are interfaced together to communicate with one another. Further, while the embodiments of the disclosure hereinafter are shown for DDR memory systems, the same is not limited to the described embodiments and could be equally applied to any other single or multi-chip memory systems.

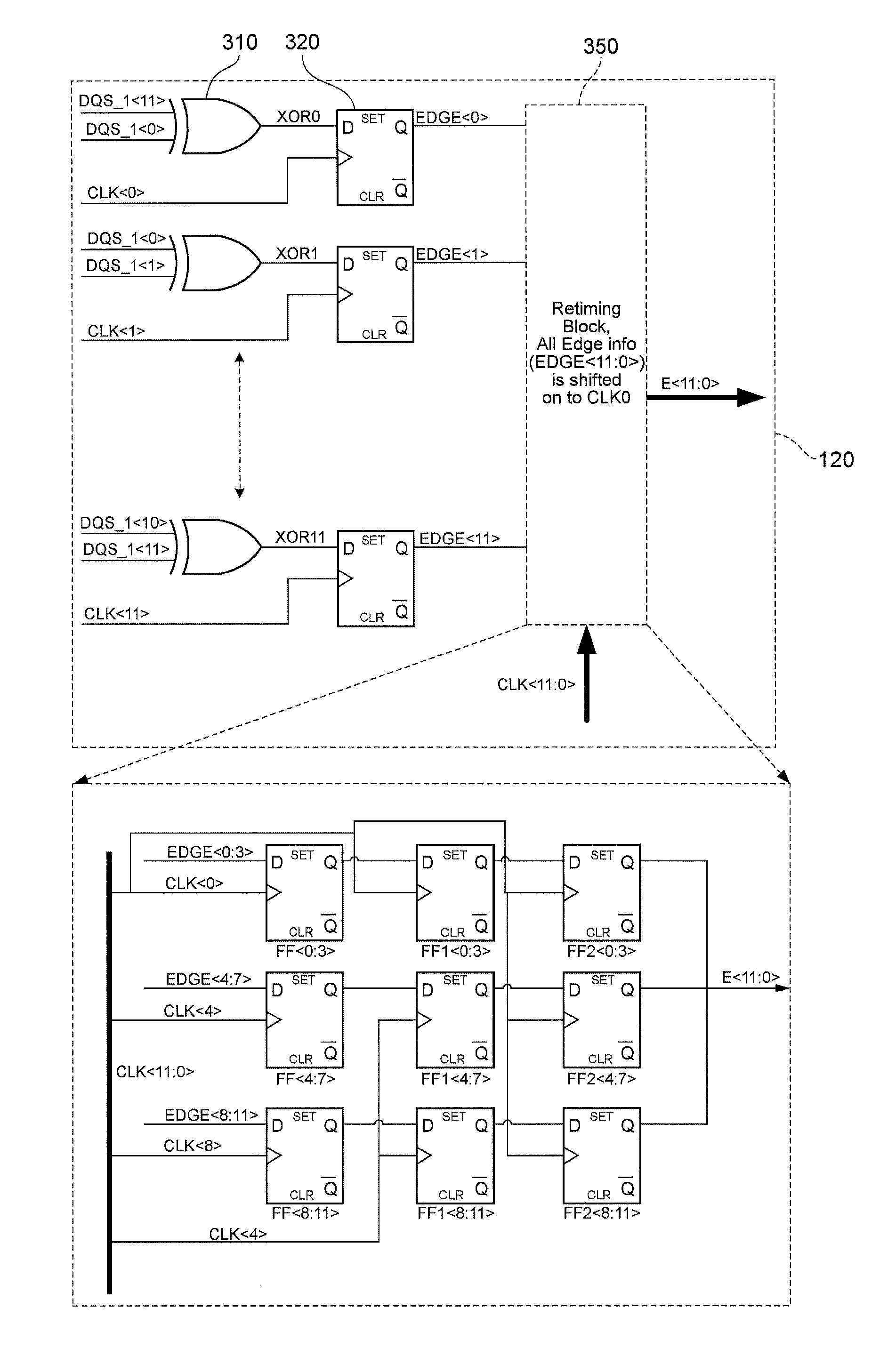

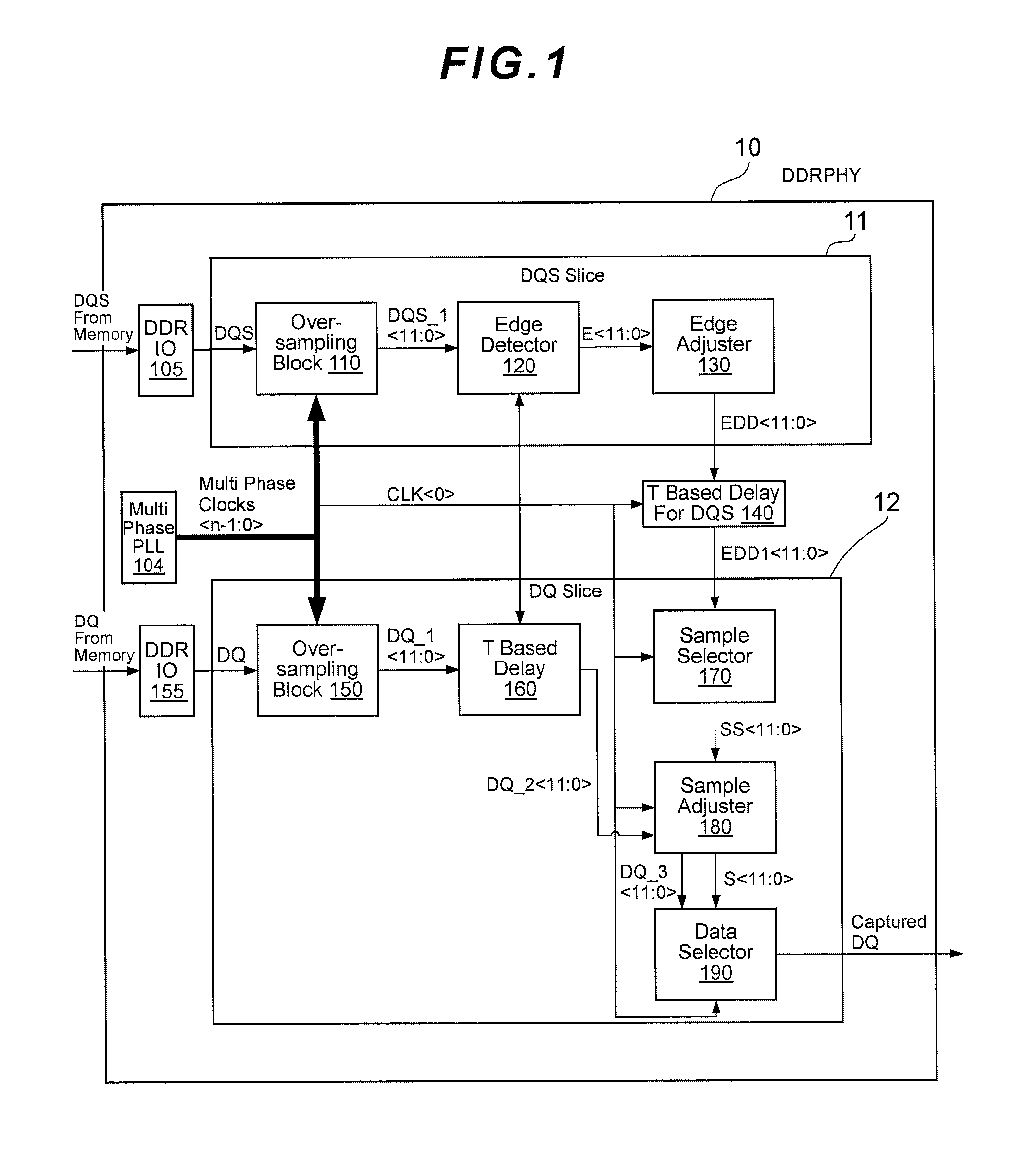

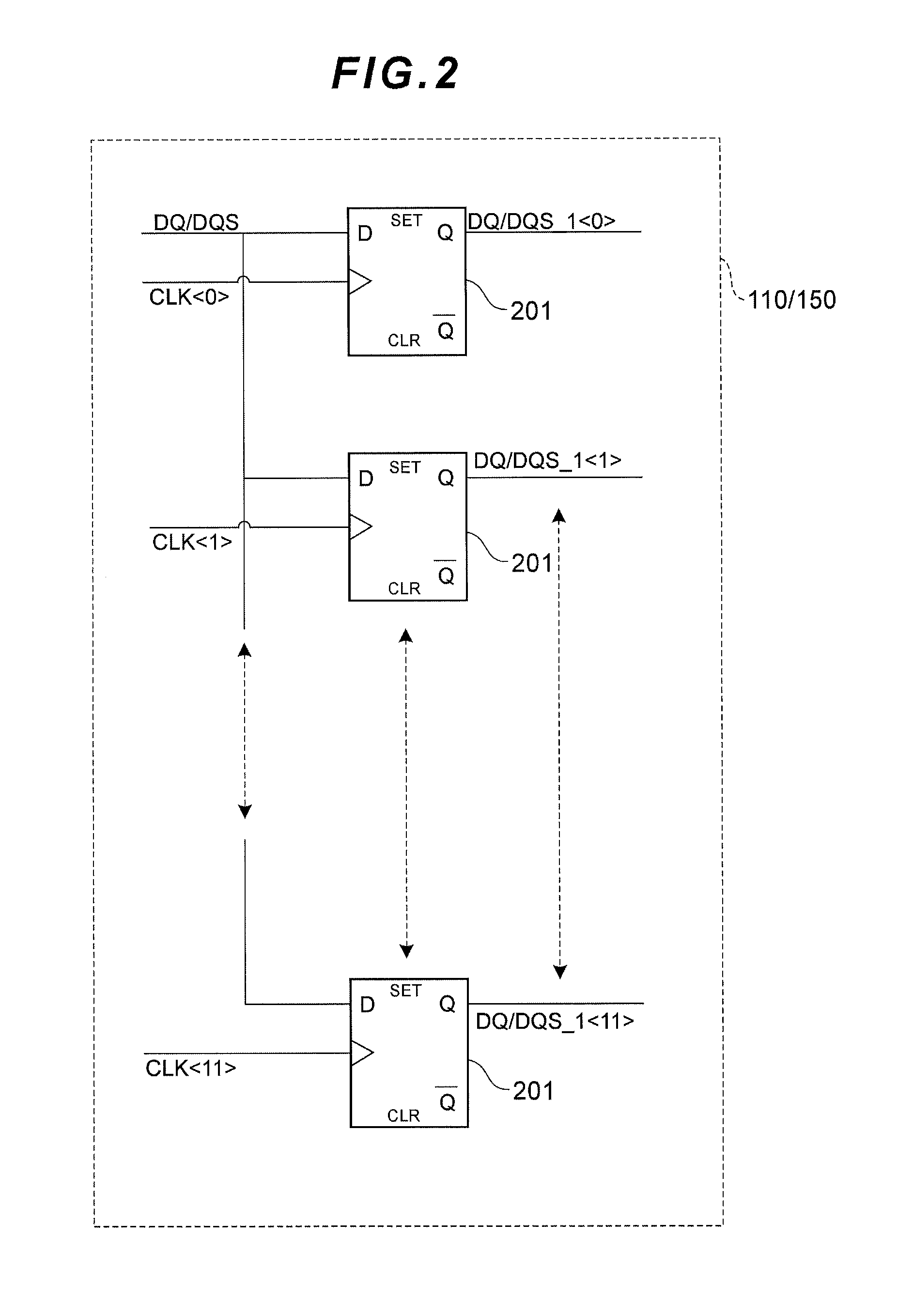

[0036]FIG. 1 is a functional block diagram of a DDR PHY 10 of the memory system (not shown in its entirety) according to one or more emb...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More