Super junction mos bipolar transistor and process of manufacture

a bipolar transistor and super junction technology, applied in the direction of superconductor devices, semiconductor devices, electrical devices, etc., can solve the problems of low switching loss, limited current density capability, and significant energy efficiency compromise in power switch device selection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

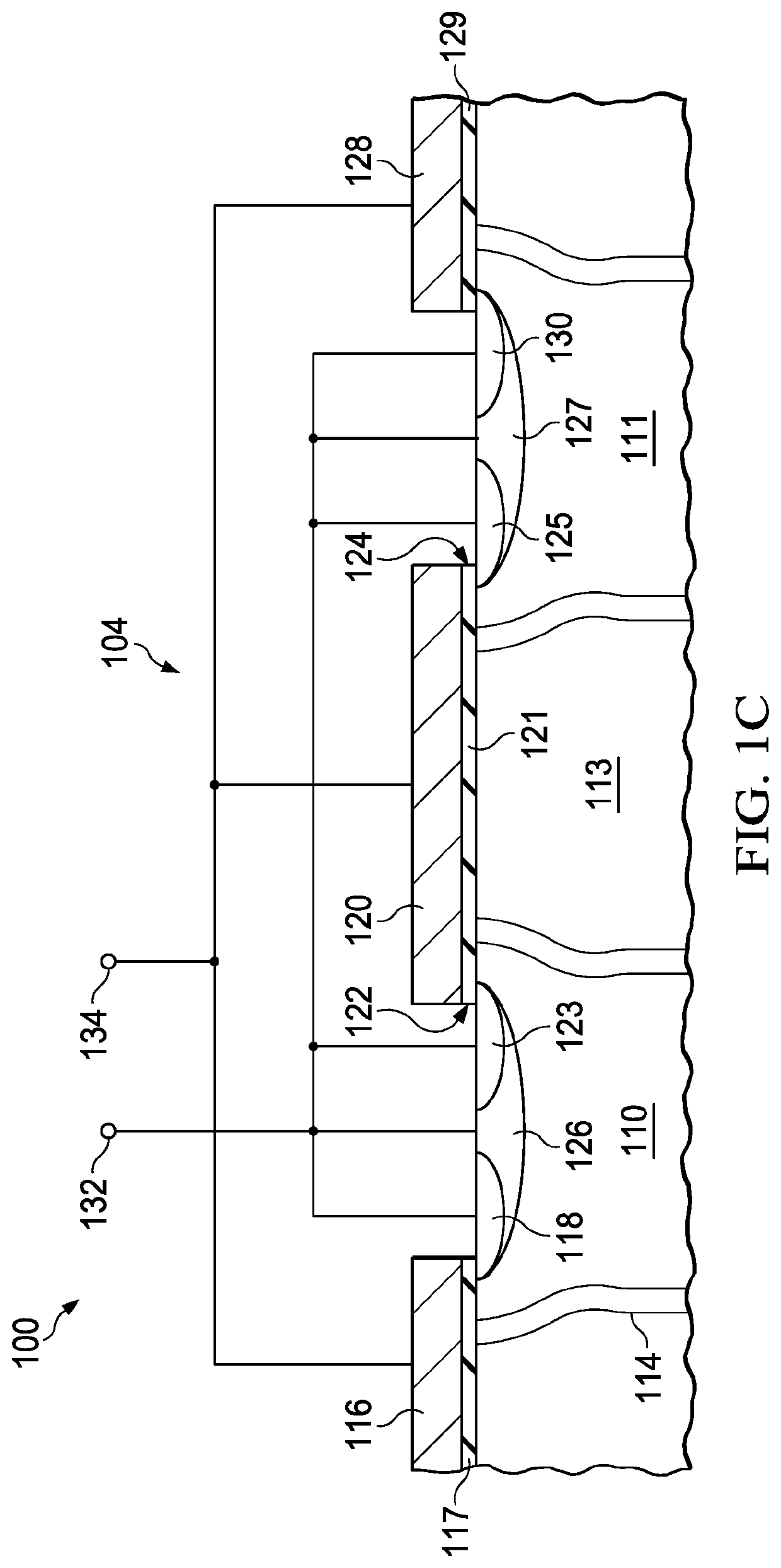

[0052]A preferred embodiment of the disclosed device is a vertically conducting FET-controlled power device with unipolar conduction at low current densities that transitions to bipolar conduction at high current densities. Bipolar conduction switches on after the unipolar conduction turns on. Unipolar conduction takes place in a highly-doped, charge-balanced drift region, thereby enabling faster switching due to the reduction in minority carrier tail current due to the enhanced recombination of minority carriers in the highly-doped charge-balance regions. Bipolar conduction switches off before the unipolar conduction switches off. These characteristics enable the device to switch faster because of a reduction in minority carrier tail current due to minority carriers starting recombination in the interval between bipolar conduction switch off and unipolar conduction switch off.

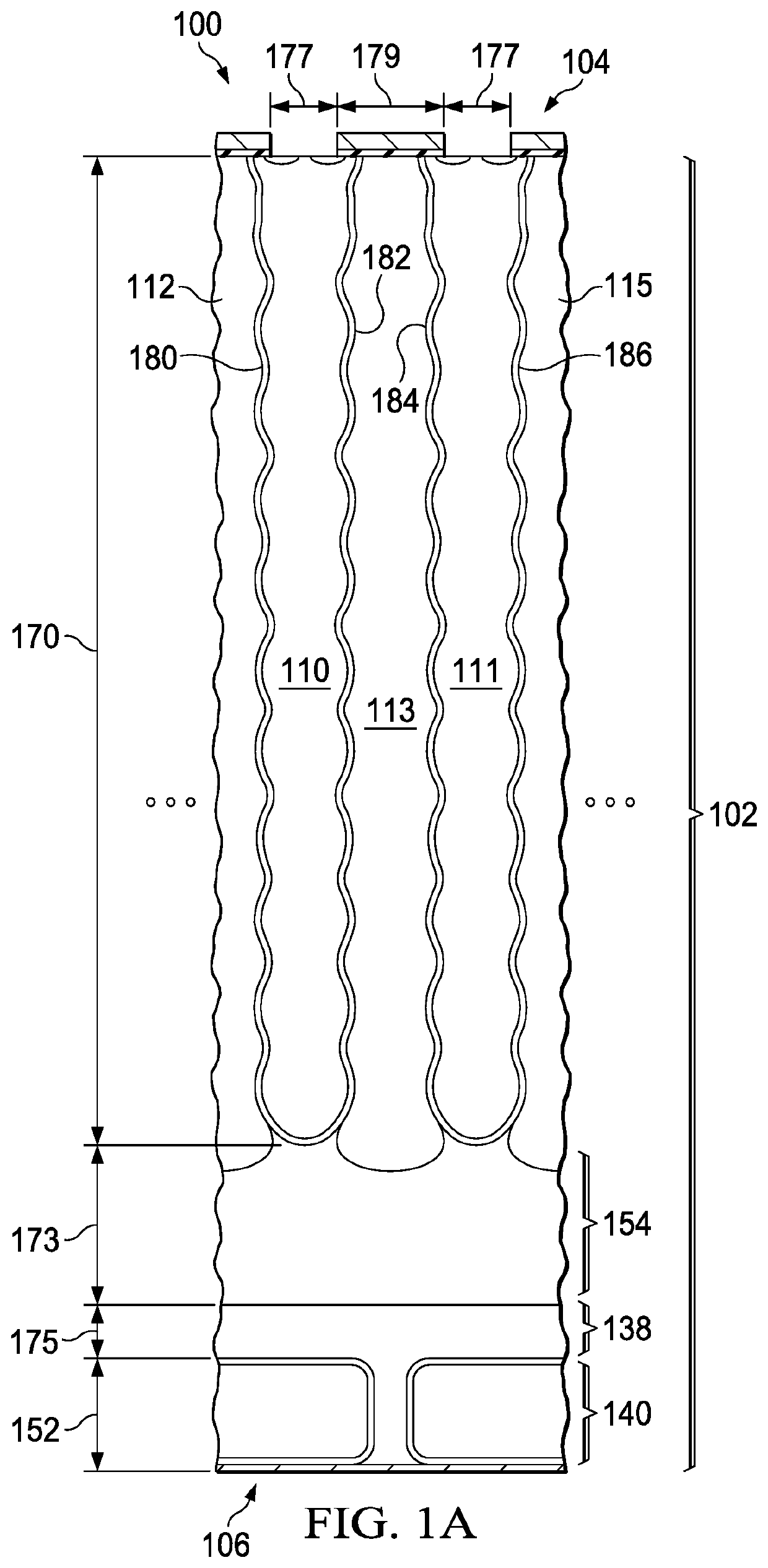

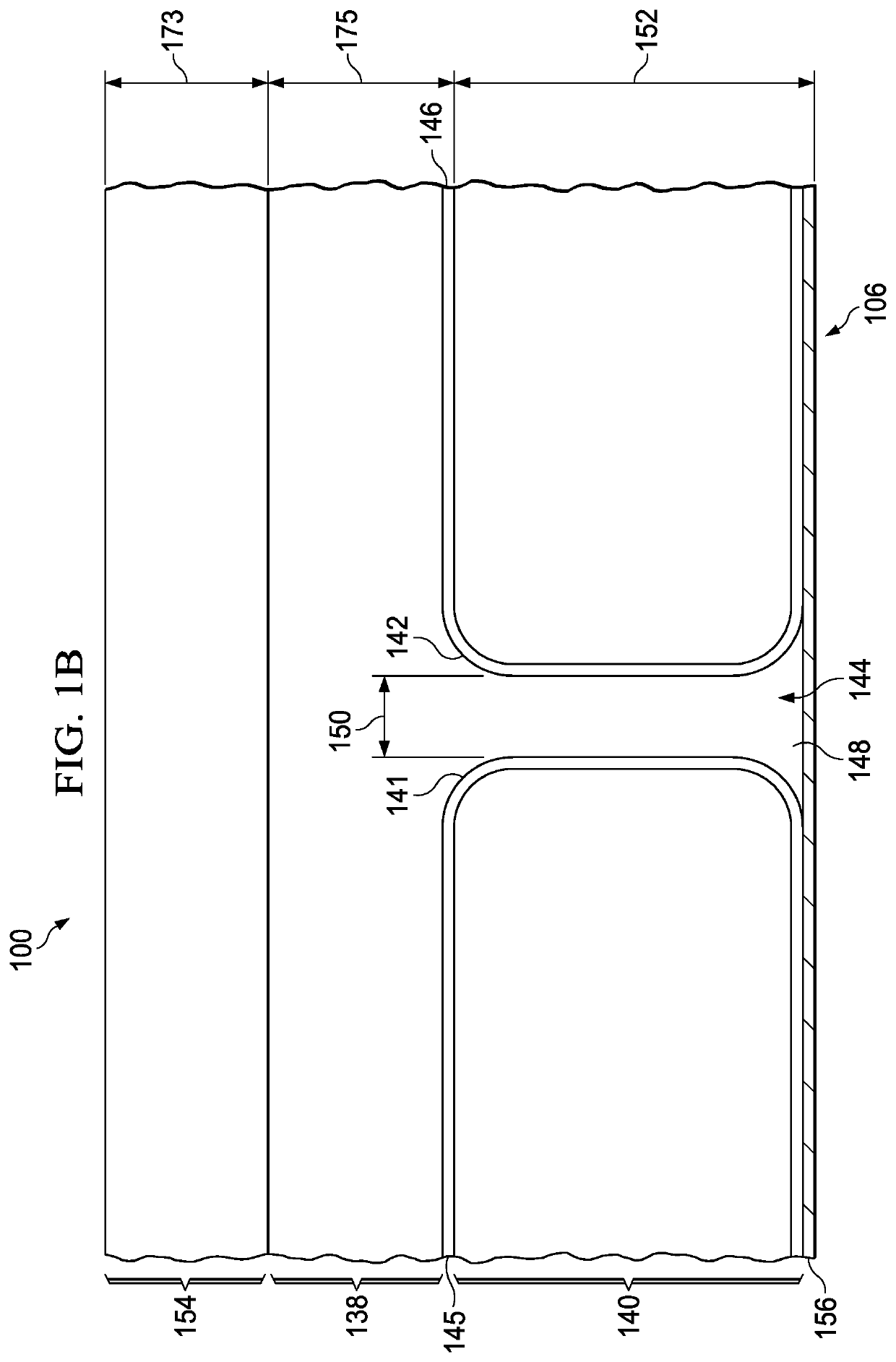

[0053]Referring to FIG. 1A, a partial cross-section of vertical semiconductor device 100 is shown. Vertical...

PUM

| Property | Measurement | Unit |

|---|---|---|

| depth | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More