Asynchronous serial analog-to-digital converter methodology having dynamic adjustment of the bandwidth

a technology dynamic adjustment, which is applied in the field of asynchronous serial analog-to-digital converter methodology having dynamic adjustment of the bandwidth, can solve the problems of increasing the cost of large number of conversion bits, and the need for analog subtraction, so as to achieve minimal circuit activity and minimal power dissipation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

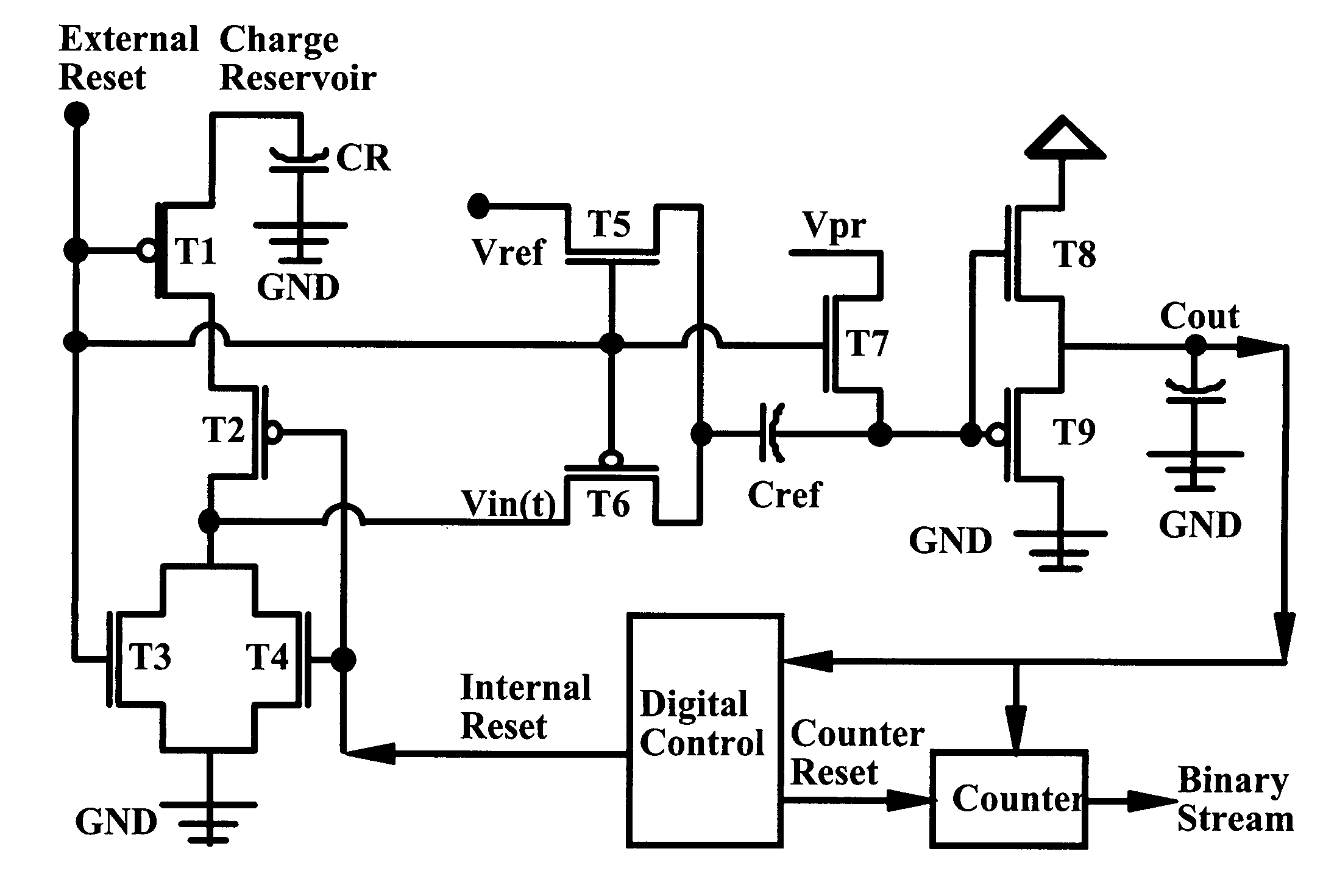

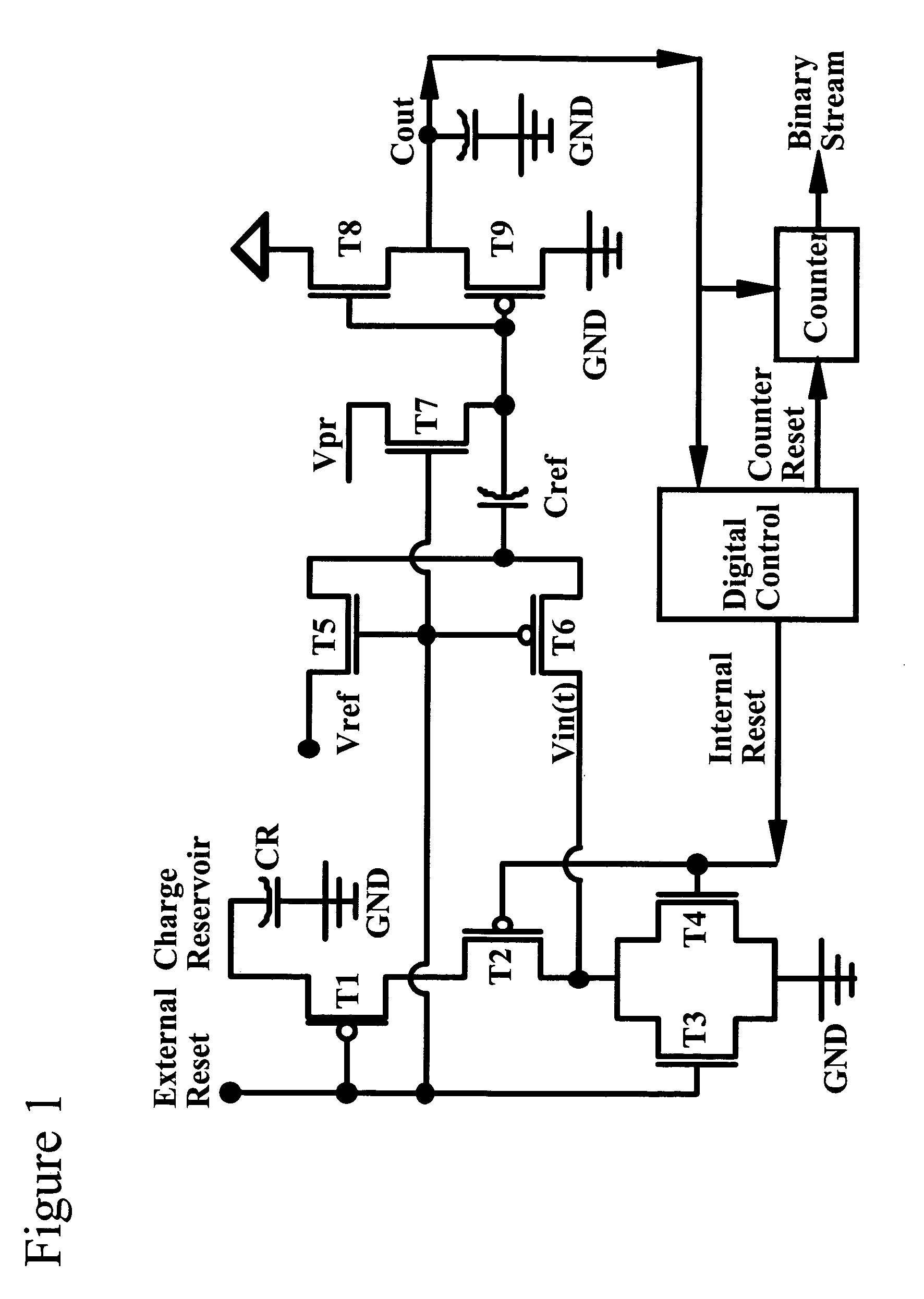

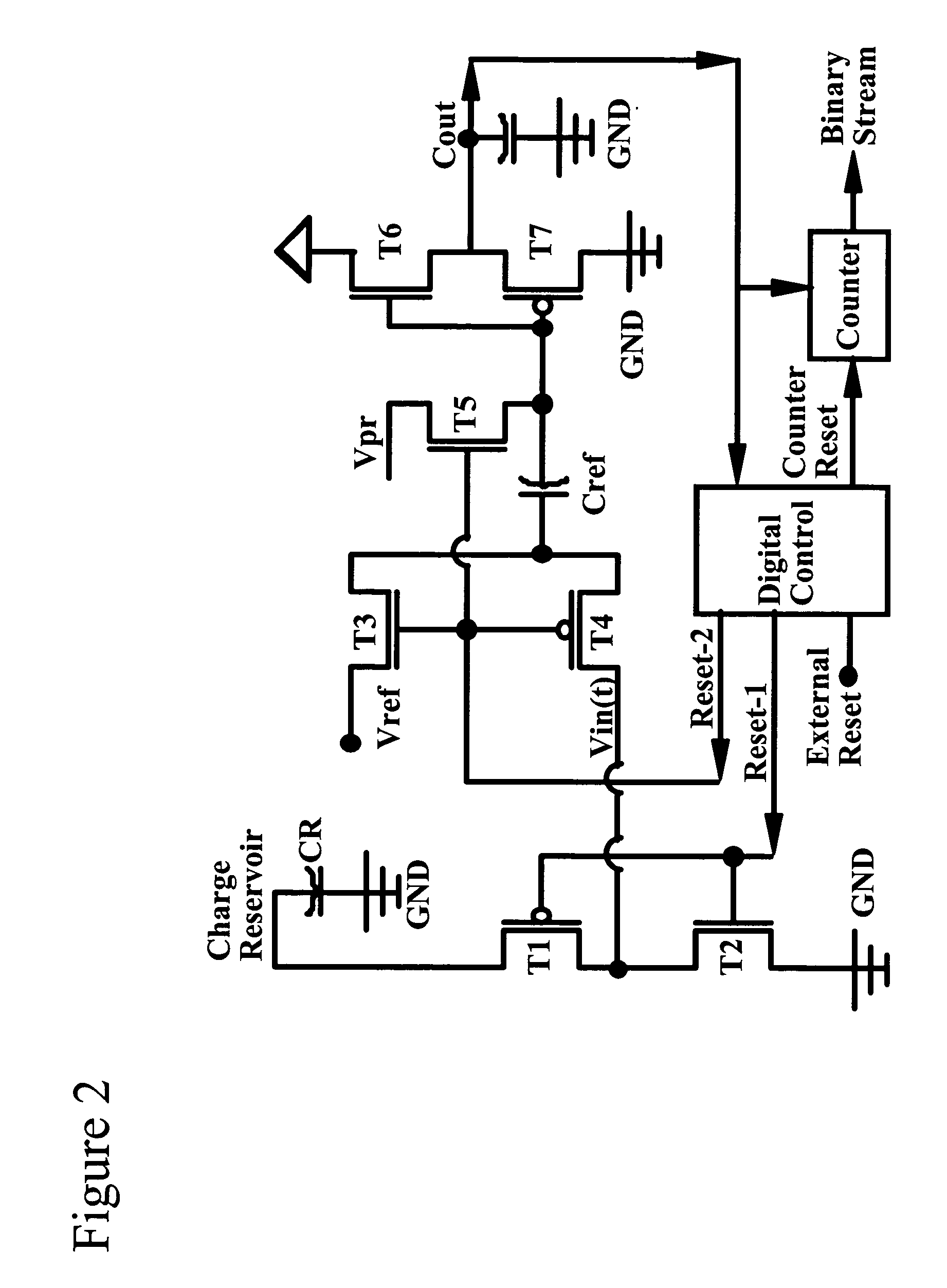

Analog-to-Digital Conversion Methodology for Charge Signals.

[0051]When applied to charge signals, the method of the present invention quantizes the amount of charge present in a “charge reservoir” by subtracting a pre-defined small amount (a “packet”) of charge from said reservoir. For as long as the amount of charge in the reservoir is larger than a “packet of charge”, one more “packet of charge” can be subtracted from the reservoir. The quantization process consists in counting the total amount of packets that are removed from the reservoir.

[0052]Even though the amount of charge in the “reservoir” is an analog quantity, because the “packet of charge” is a known, precisely defined quantity, the charge-subtraction is itself a “digital process”. In other words, the conversion process works by subtracting a small “digital amount” of charge from an analog charge reservoir.

[0053]A packet of charge is defined through the pre-charging of the input capacitor (Cref) of the comparator. The v...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More