Differential bang-bang phase detector (BBPD) with latency reduction

a technology of phase detector and bang-bang, which is applied in the direction of oscillation comparator circuit, automatic control, instruments, etc., can solve the problems of limiting the operating frequency and data-rate of the communication circuit of the cdr circuitry used in the application, and achieve the effect of improving the performance of the bang-bang phase detection circui

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

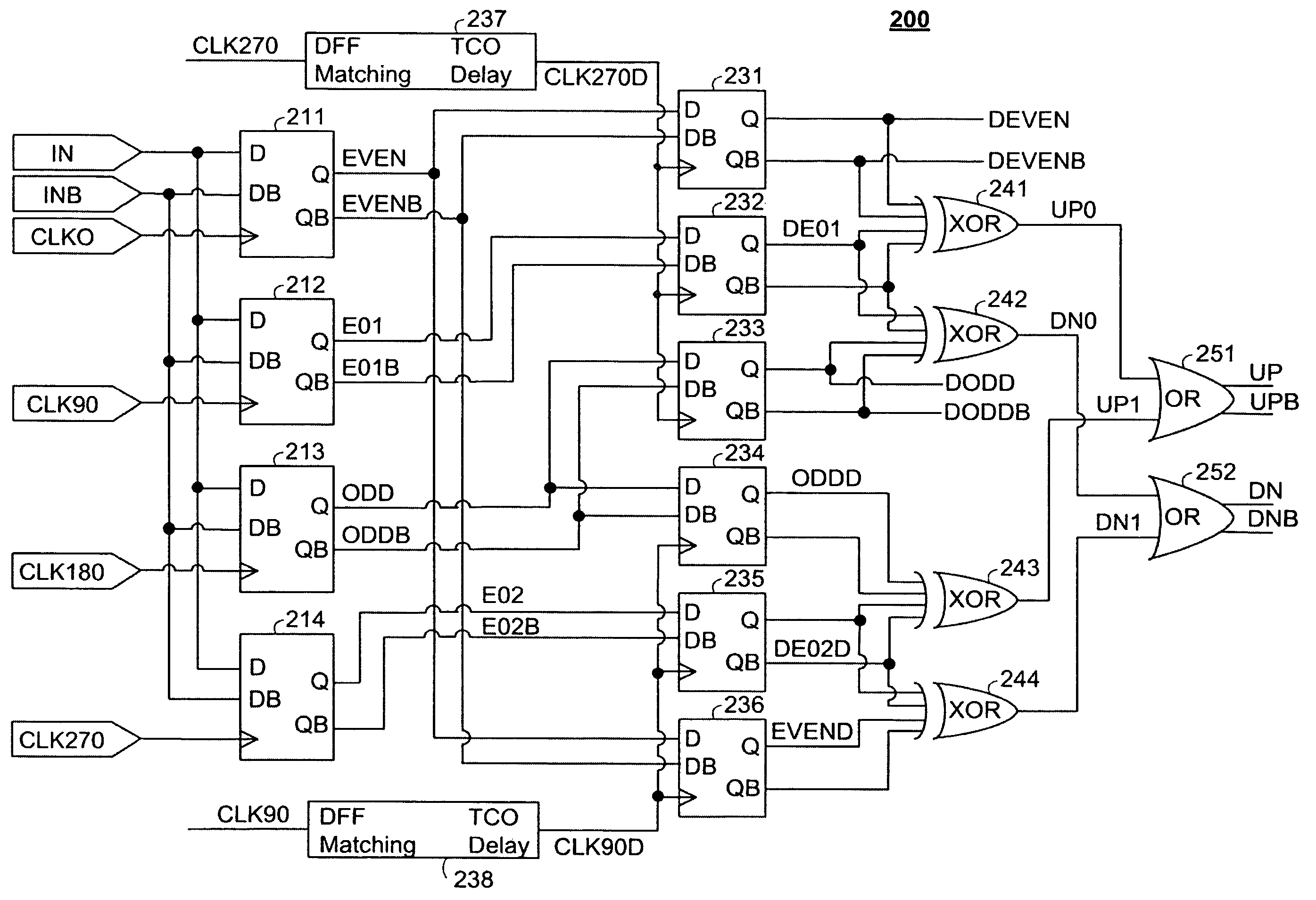

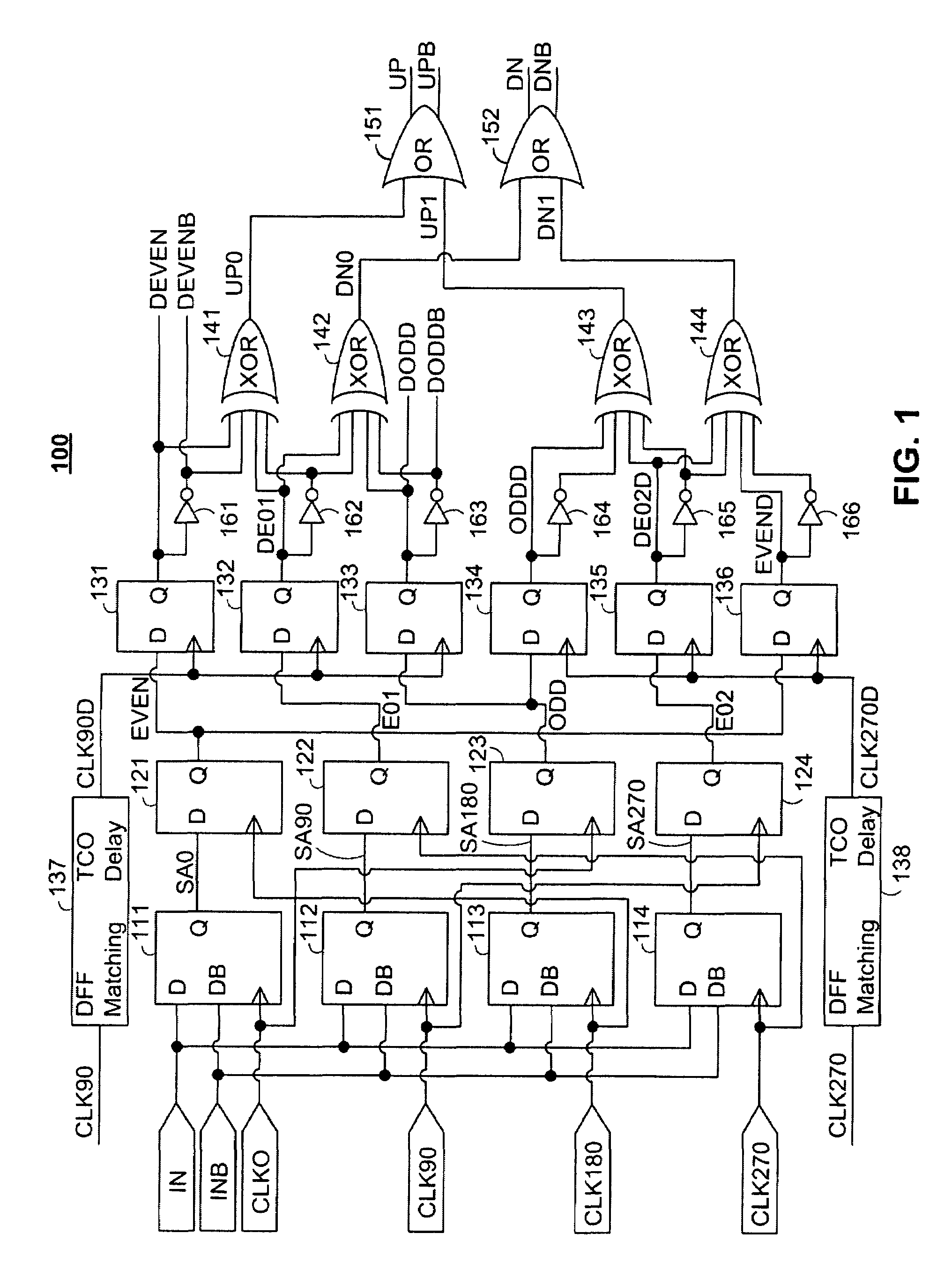

[0014]FIG. 1 shows a schematic diagram of a bang-bang phase detector (BBPD) circuit 100 including first, second and third stages of timing circuitry and first and second stages of combinational logic circuitry. BBPD circuit 100 produces from differential input signals IN / INB received at differential input nodes two sets, UP / UPB and DN / DNB, of differential output signals used to detect the phase of the input signals. BBPD circuit 100 receives four clock signals CLK0, CLK90, CLK180, and CLK270 for timing, and produces two additional delayed clock signals CLK90D and CLK270D.

[0015]BBPD circuit 100 also functions as a differential input sampler that produces two sets, DEVEN / DEVENB and DODD / DODDB, of retimed differential output signals. The first retimed differential output signal, DEVEN / DEVENB, includes the even samples of the input signal (samples 2, 4, . . . ), and the second differential output signal, DODD / DOODB, includes the odd samples of the input signal (samples 1, 3, . . . ). Bo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More