Recording and displaying logic circuit simulation waveforms

a logic circuit and simulation waveform technology, applied in the field of simulation of electronic logic circuits, can solve the problems of waveform display tools that crash in use, the size of vcd format files is often prohibitively large to be handled by waveform display tools, and the large amount of recorded data, so as to reduce graphics generation overhead, reduce the size of recorded files, and speed up the generation of displays

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

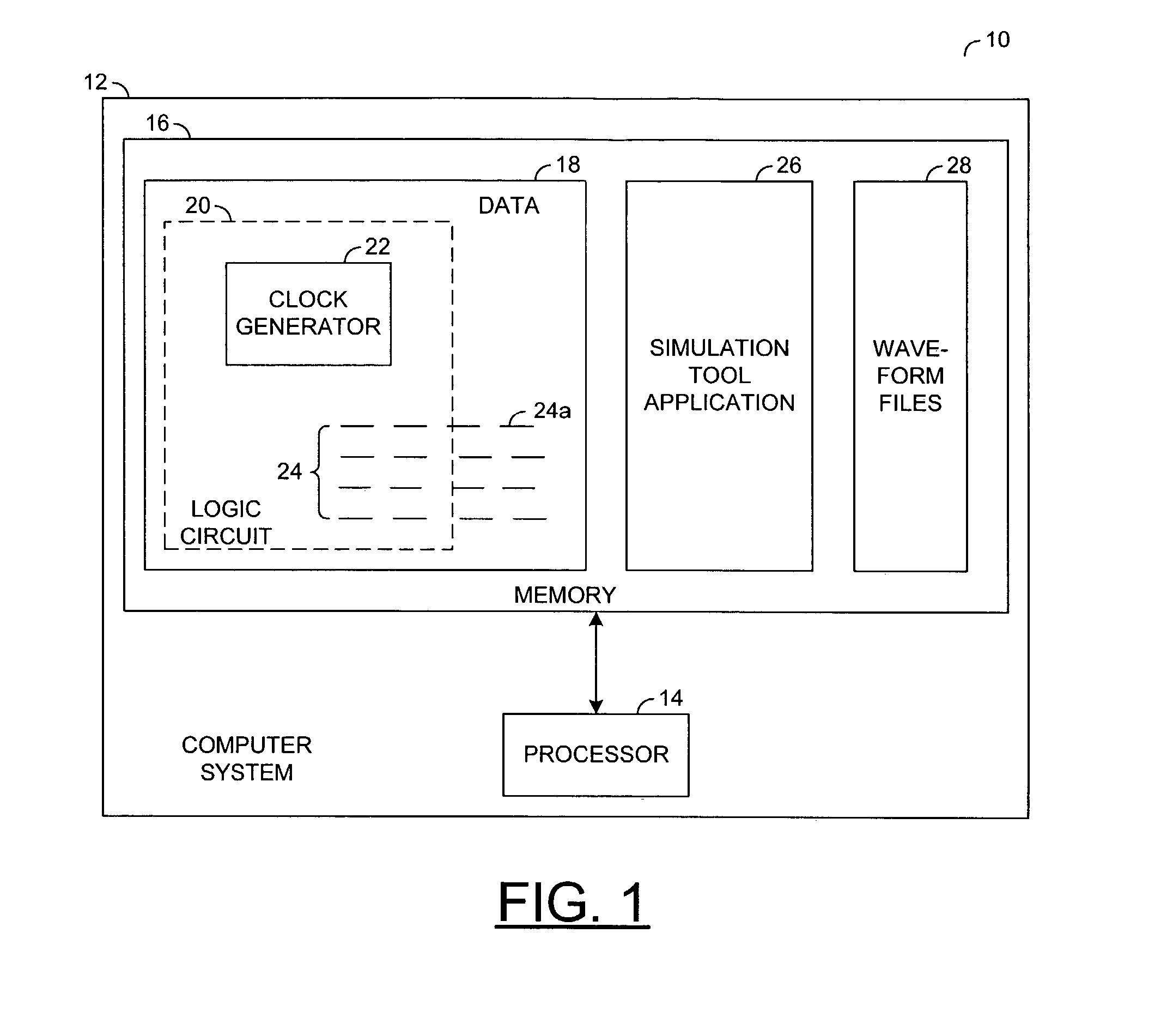

[0020]Referring to FIG. 1 a computerized simulation tool 10 may comprise a first computer system 12 including a processor 14 communicating with one or more regions of storage 16. The computer system 12 may comprise a workstation (not shown) coupled to a network (not shown). At least a portion of the storage 16 may be on the network (not shown). The storage 16 may include regions of one or more of magnetic media (e.g., a hard disc), optical media, and semiconductor media (e.g., memory circuitry). Stored in the storage 16 may be data 18 representing a model 20 of a logic circuit whose operation may be simulated. The logic circuit model 20 may include one or more clock signal generator blocks 22 for generating one or more clock signals for the logic circuit model 20. The logic circuit model 20 may include one of more interface nodes 24 for inputting and / or outputting signals to / from the logic circuit model 20. One or more of the nodes 24 may be a clock input node 24a for accepting a cl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More