Embedded semiconductor device package and method of manufacturing thereof

a semiconductor device and embedded technology, applied in the direction of inspection/indentification of circuits, printed circuit aspects, printed circuit non-printed electric components association, etc., can solve the problems of high cost slow and time-consuming application, and limited reliability of encapsulant/embedding compound typically used

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

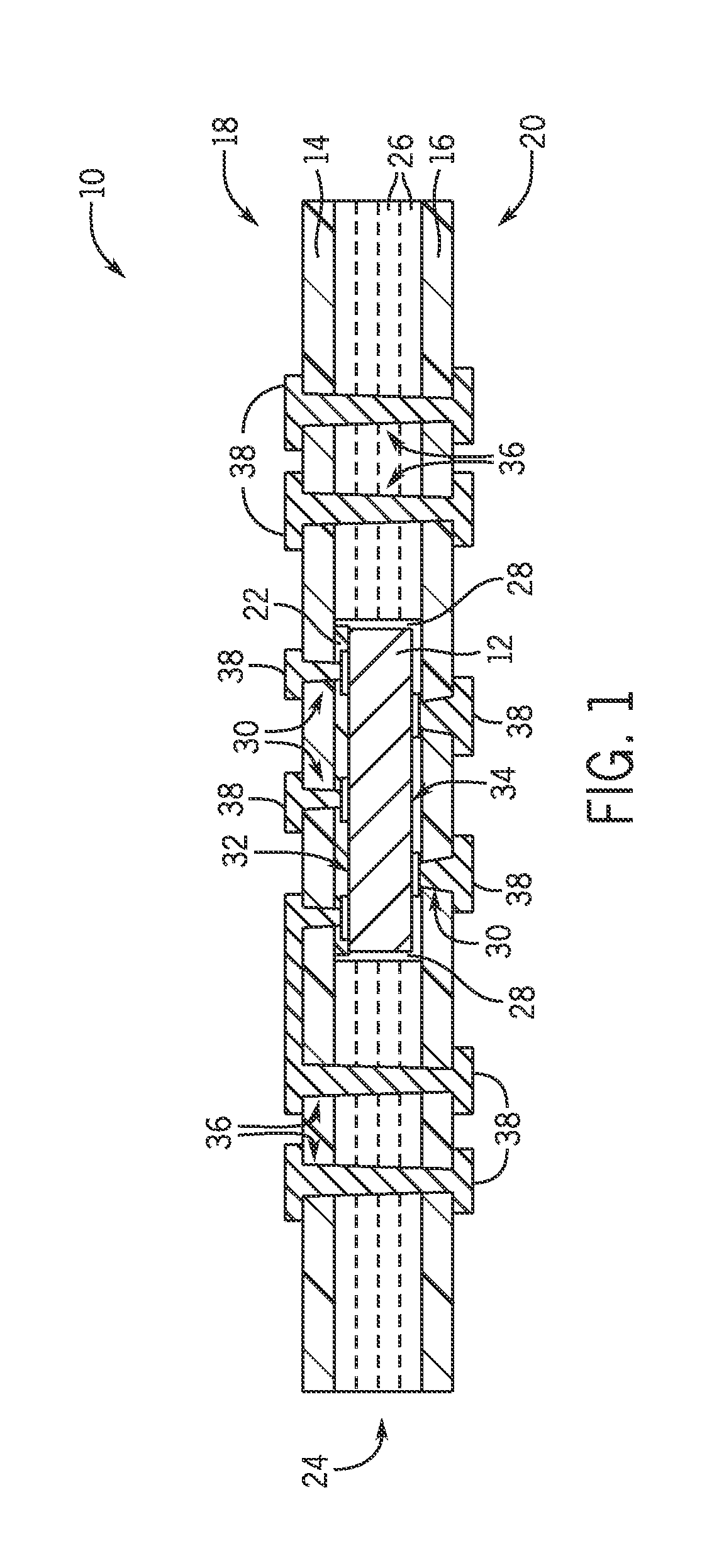

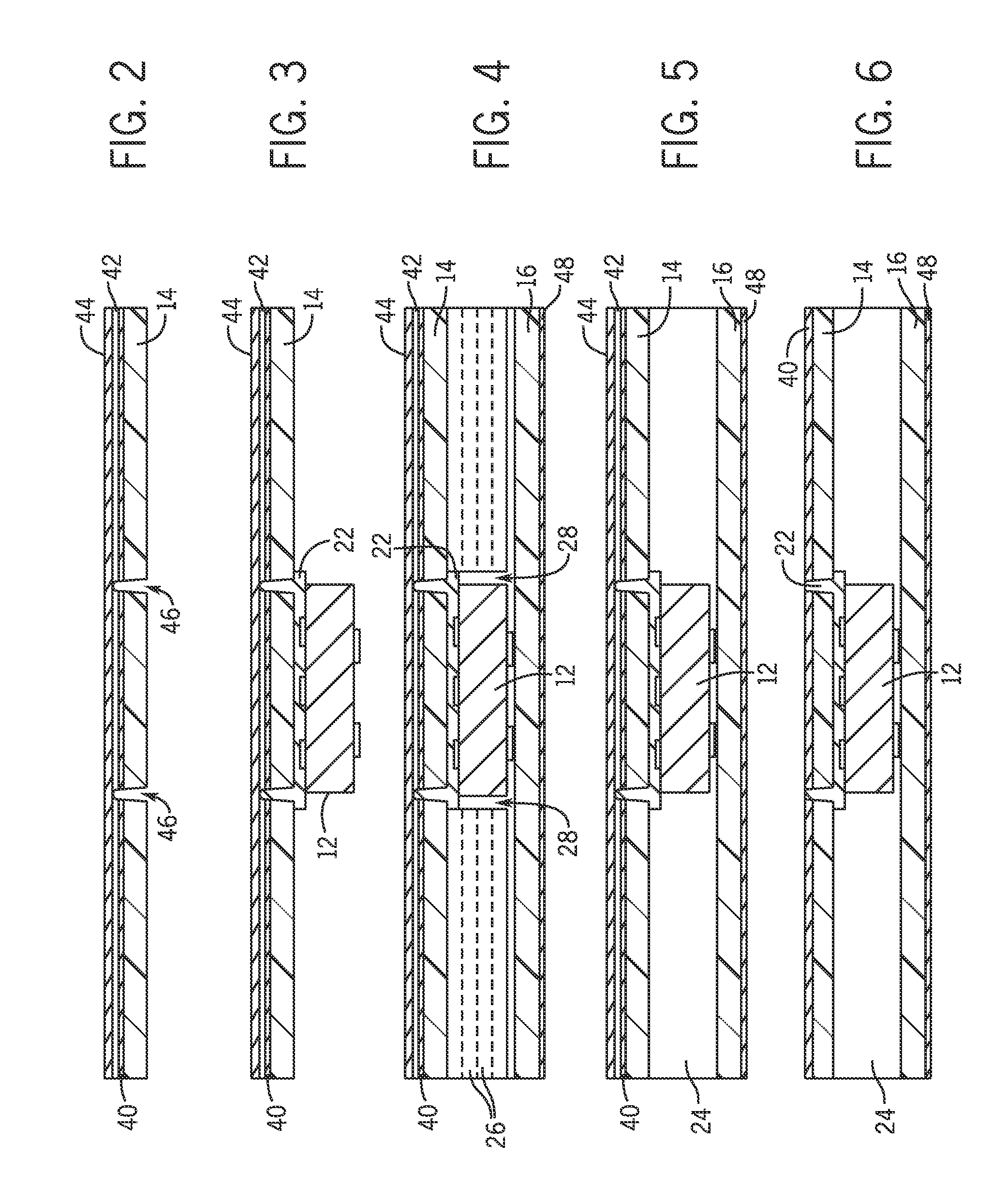

[0025]Embodiments of the present invention provide for an embedded power module package structure having power overlay (POL) interconnects that form all electrical and thermal interconnections to the semiconductor devices in the power module, as well as a method of forming such a package structure.

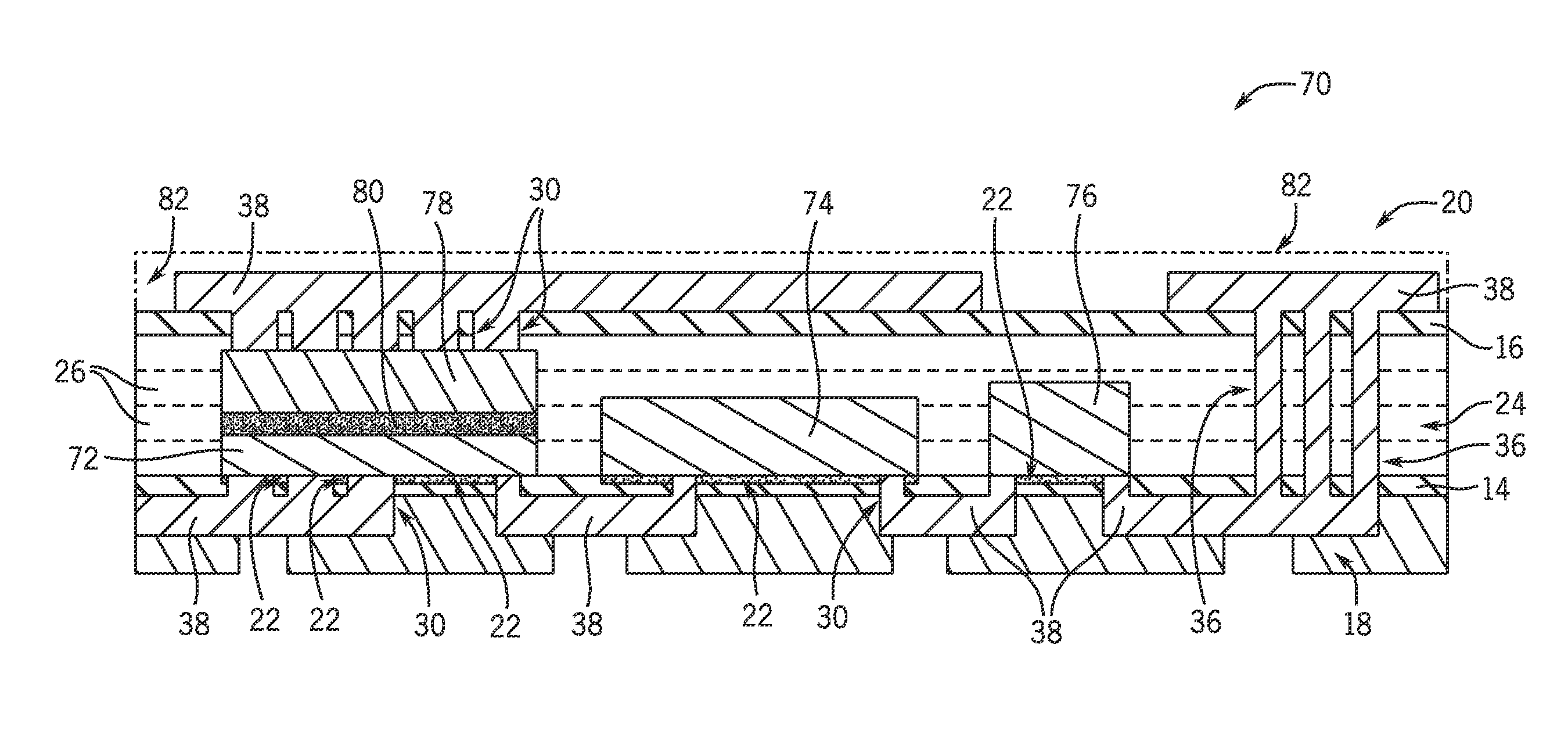

[0026]Referring to FIG. 1, a POL packaging and interconnect structure 10 is shown according to an embodiment of the invention. The package structure 10 includes a semiconductor device 12 that can be in the form of either what can generally be described as a “power device” or a “non-power device”, and thus can be in the form of a die, diode, MOSFET, application specific integrated circuit (ASIC), or processor, for example. While a single semiconductor device 12 is shown in FIG. 1, it is recognized that additional semiconductor devices or electronic components could be included in the POL structure 10, as will be described below regarding another embodiment of the invention. The semiconducto...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com