Sealed stacked arrangement of semiconductor devices

a semiconductor device and stacking technology, applied in semiconductor devices, semiconductor/solid-state device details, instruments, etc., can solve the problems of deteriorating product yield, complicated manufacturing process, and inability to constitute a package using the same size of sub-chips formed in the same manufacturing process, and achieves effective chip mounting, large memory capacity, and the effect of avoiding the loss of heat radiation characteristic of the package and product yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

1. 128M DRAM Package according to Double Chip Packaging Method

1.1. Outline of DRAM Package

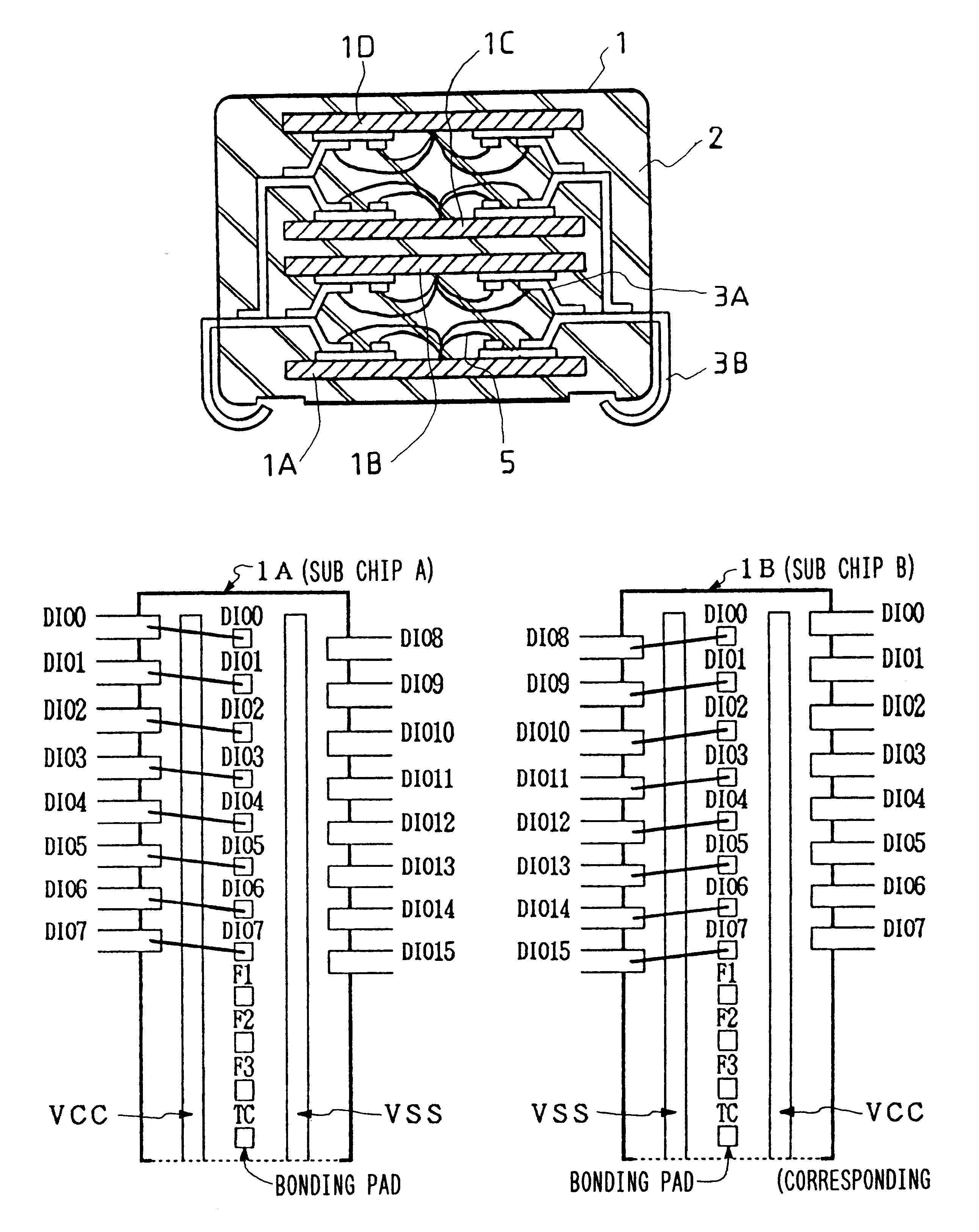

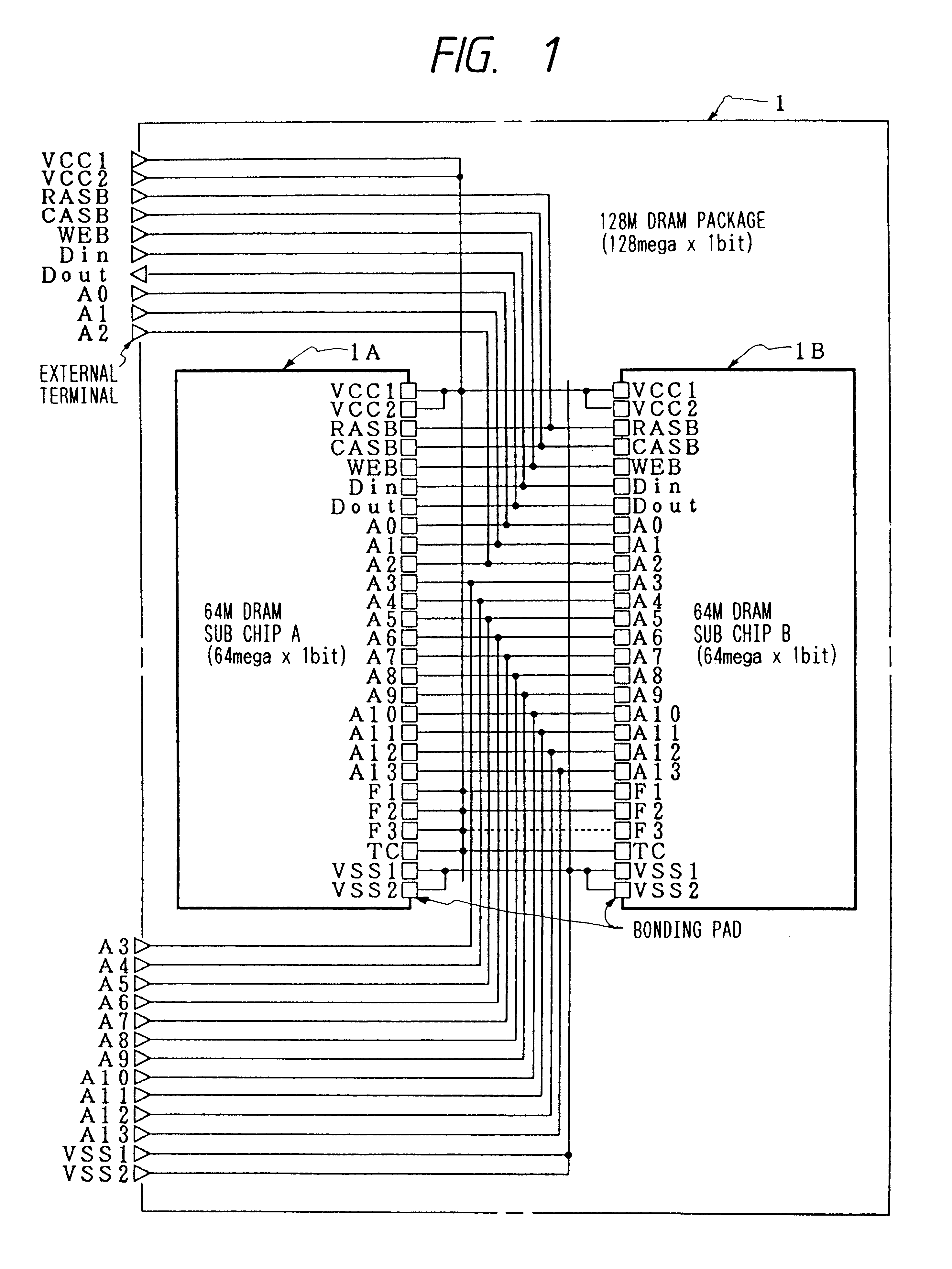

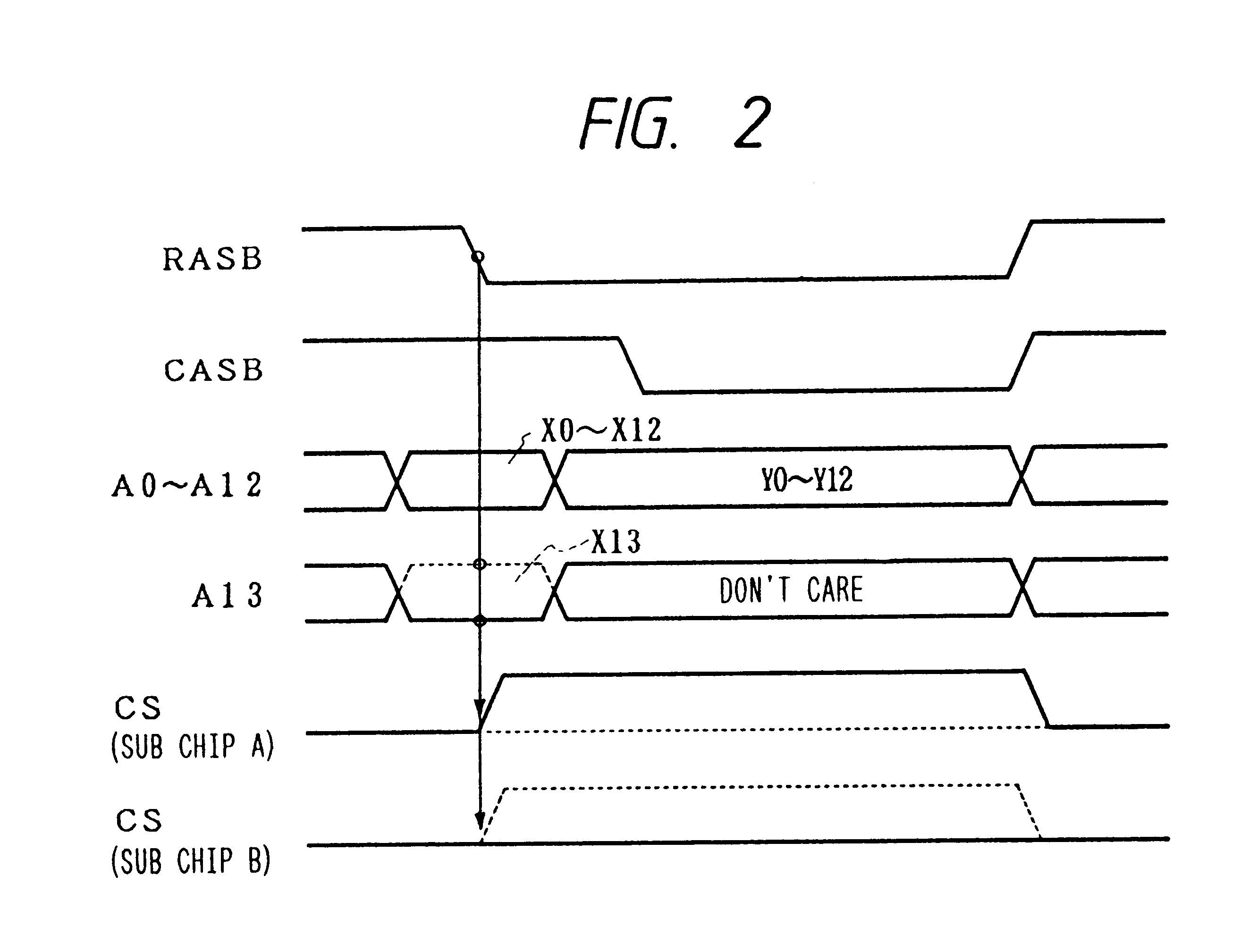

FIG. 1 is a block diagram showing an example of a 128M ("M" or "mega" is assumed equal to the twentieth power of 2 herein) DRAM package according to the present invention, and FIG. 2 is a timing chart in the said DRAM package. With reference to these figures, an outline of this DRAM package and an explanation of a chip selecting method will first be given below. The chip mounting method according to the present invention will herein be designated a double chip packaging method. For a specific description of the double chip packaging method and features thereof, see "1.4. Package Form of DRAM Package."

1.1.1. Block Configuration

A DRAM package 1 according to this embodiment includes two DRAM sub chips 1A and 1B. These sub chips each have a memory capacity of 64 mega. Write data and read data are inputted or outputted each in the unit of one bit through a data input terminal Din or a data output te...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More