Systems and methods for implementing a sample rate converter using hardware and software to maximize speed and flexibility

a sample rate converter and hardware technology, applied in the field of audio amplification systems, can solve the problems of low performance applications, low system performance, and high implementation cost of applications, and achieve the effects of reducing system cost and complexity, maximizing system performance, and retaining system speed and flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022]One or more embodiments of the invention are described below. It should be noted that these and any other embodiments described below are exemplary and are intended to be illustrative of the invention rather than limiting.

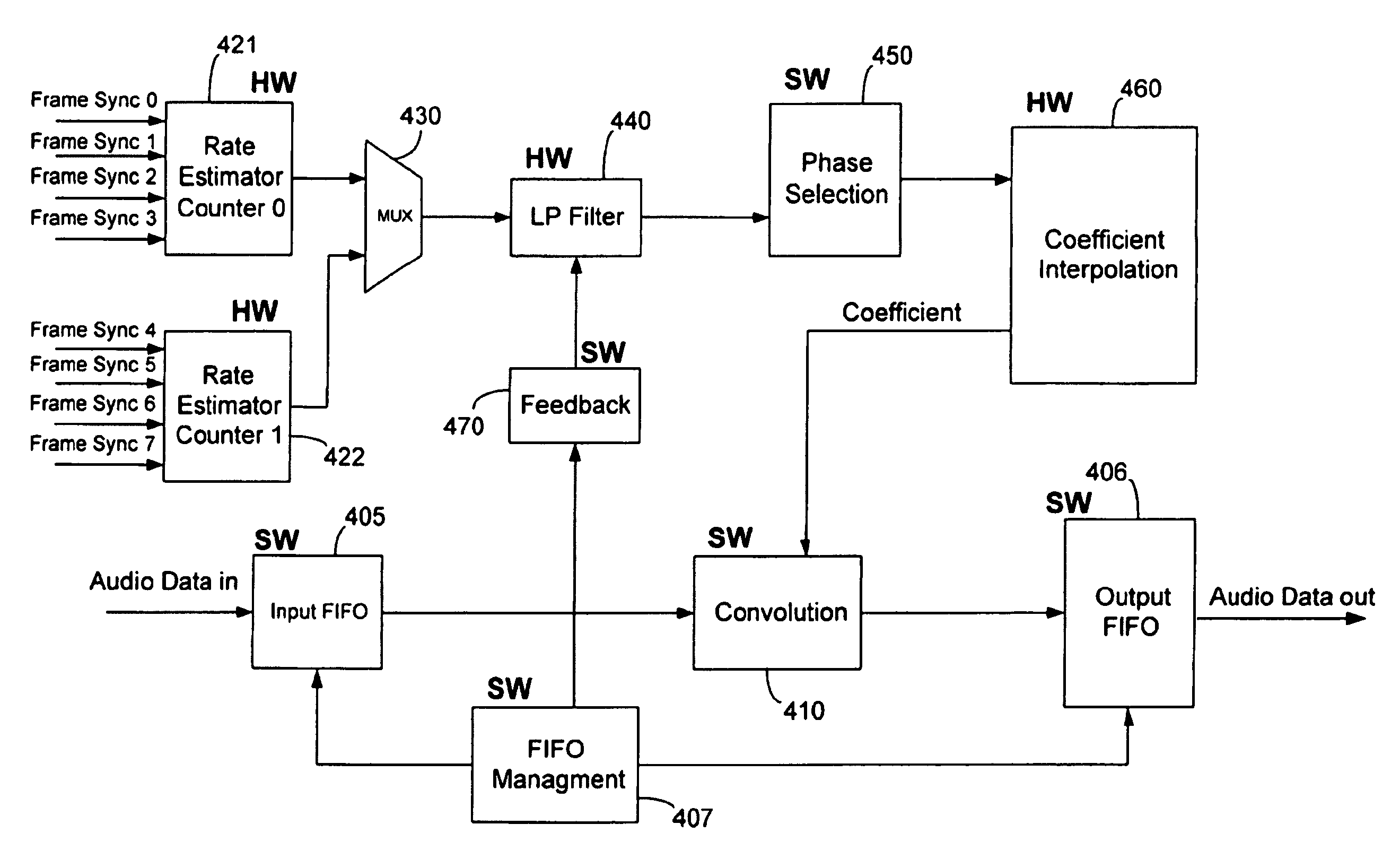

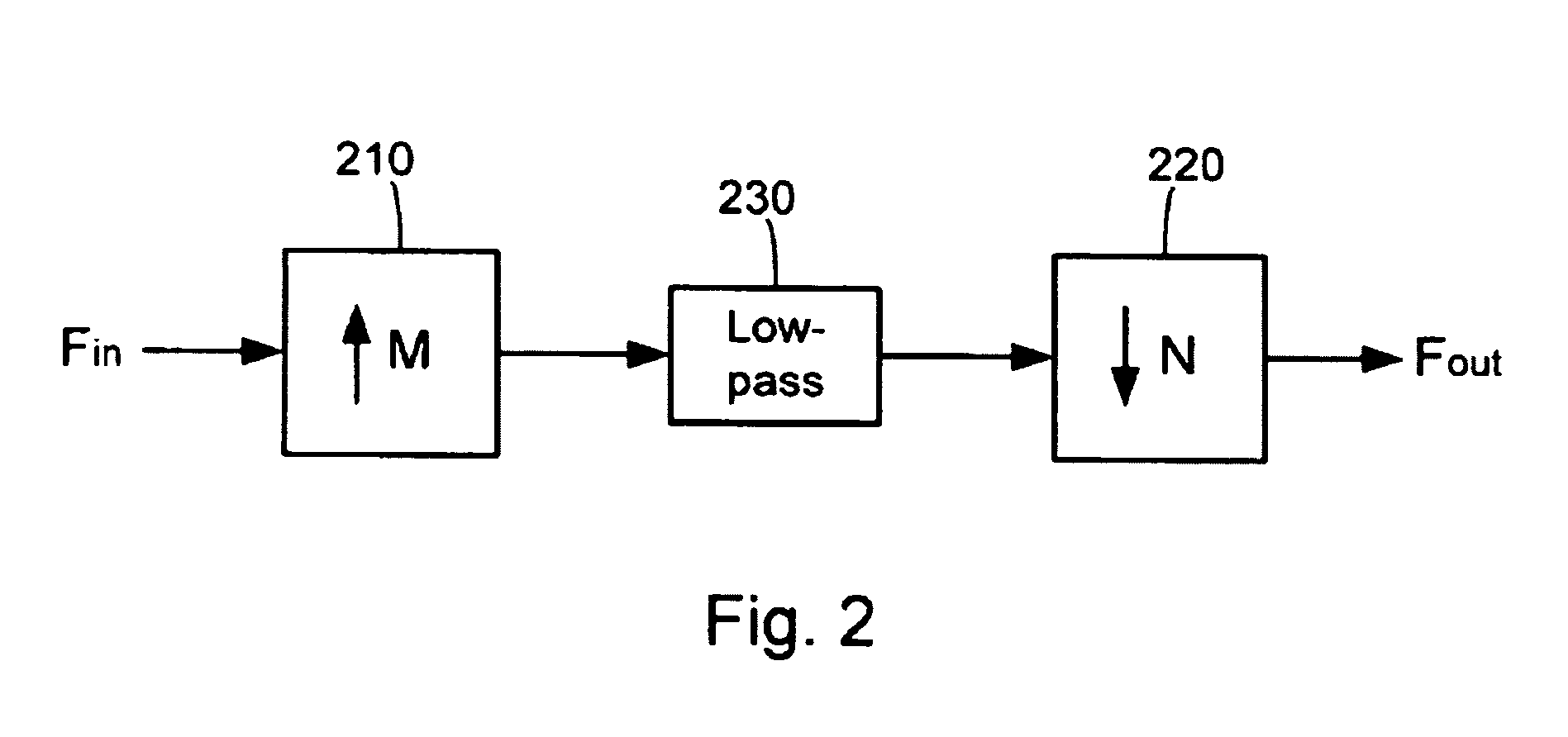

[0023]As described herein, various embodiments of the invention comprise systems and methods for converting a digital input data stream from a first sample rate to a second sample rate using a combination of hardware and software components. As used herein, “hardware” refers to dedicated, fixed-function logic. “Software,” on the other hand, is used to refer to programmable logic that is controlled by an algorithm defined by a programmer, or utilizing generic programmable blocks under software, as in a digital signal processor (DSP) arithmetic logic unit (ALU) or memory.

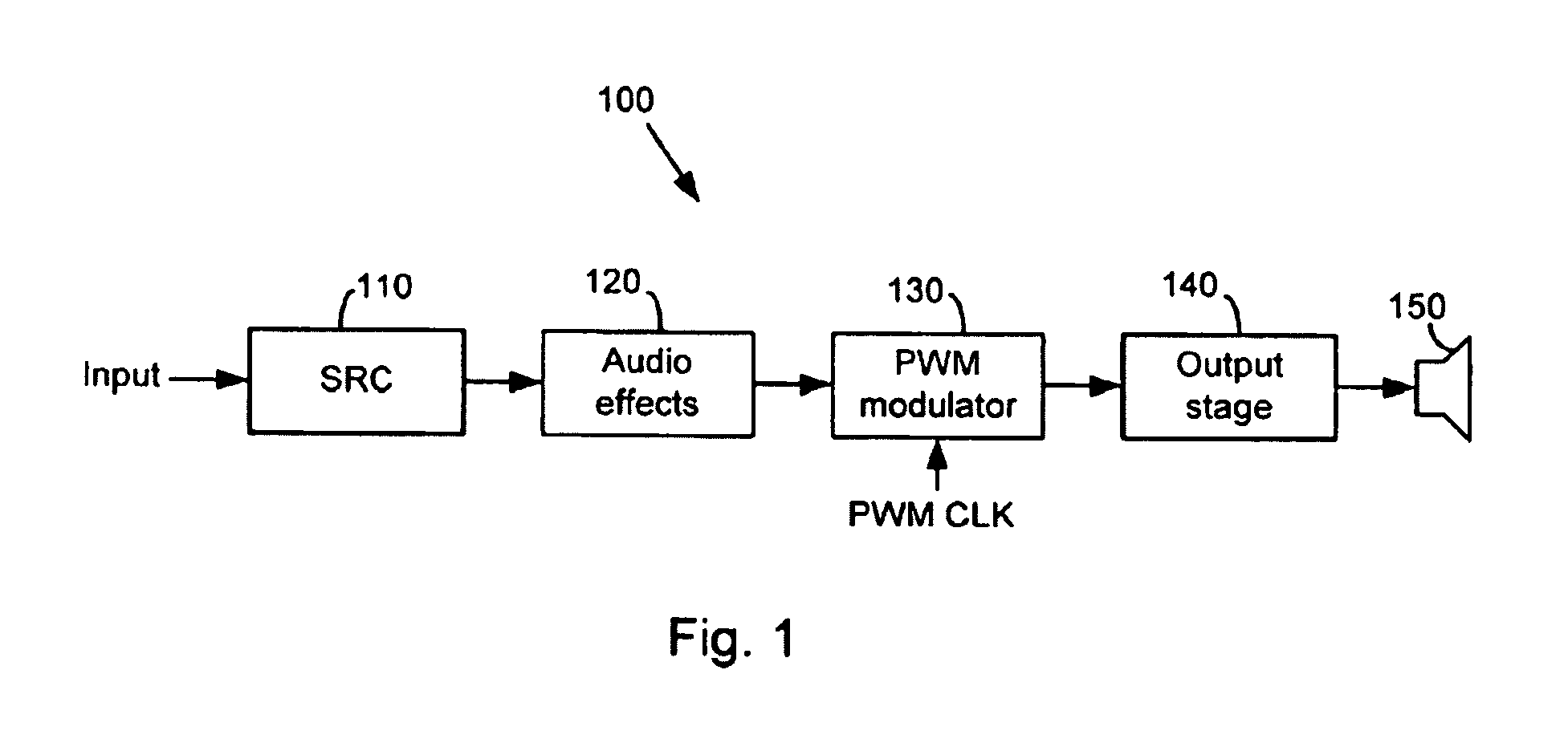

[0024]In one embodiment, the conversion from the first sample rate to the second sample rate is performed in a sample rate converter for a digital audio system. The sample rate converter has mu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More