Patents

Literature

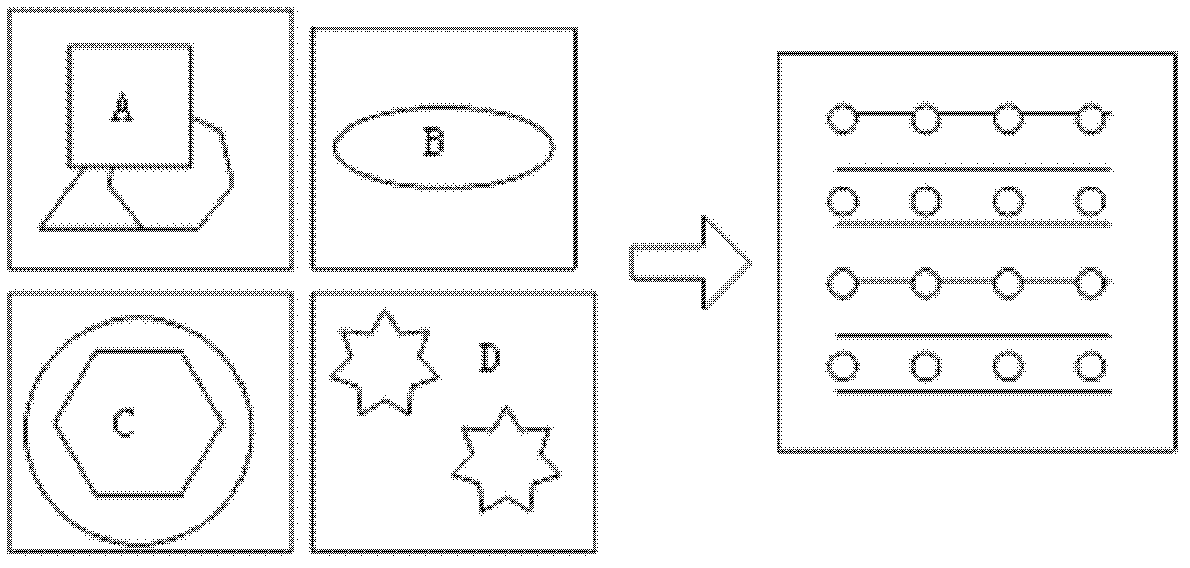

246results about How to "Retain flexibility" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

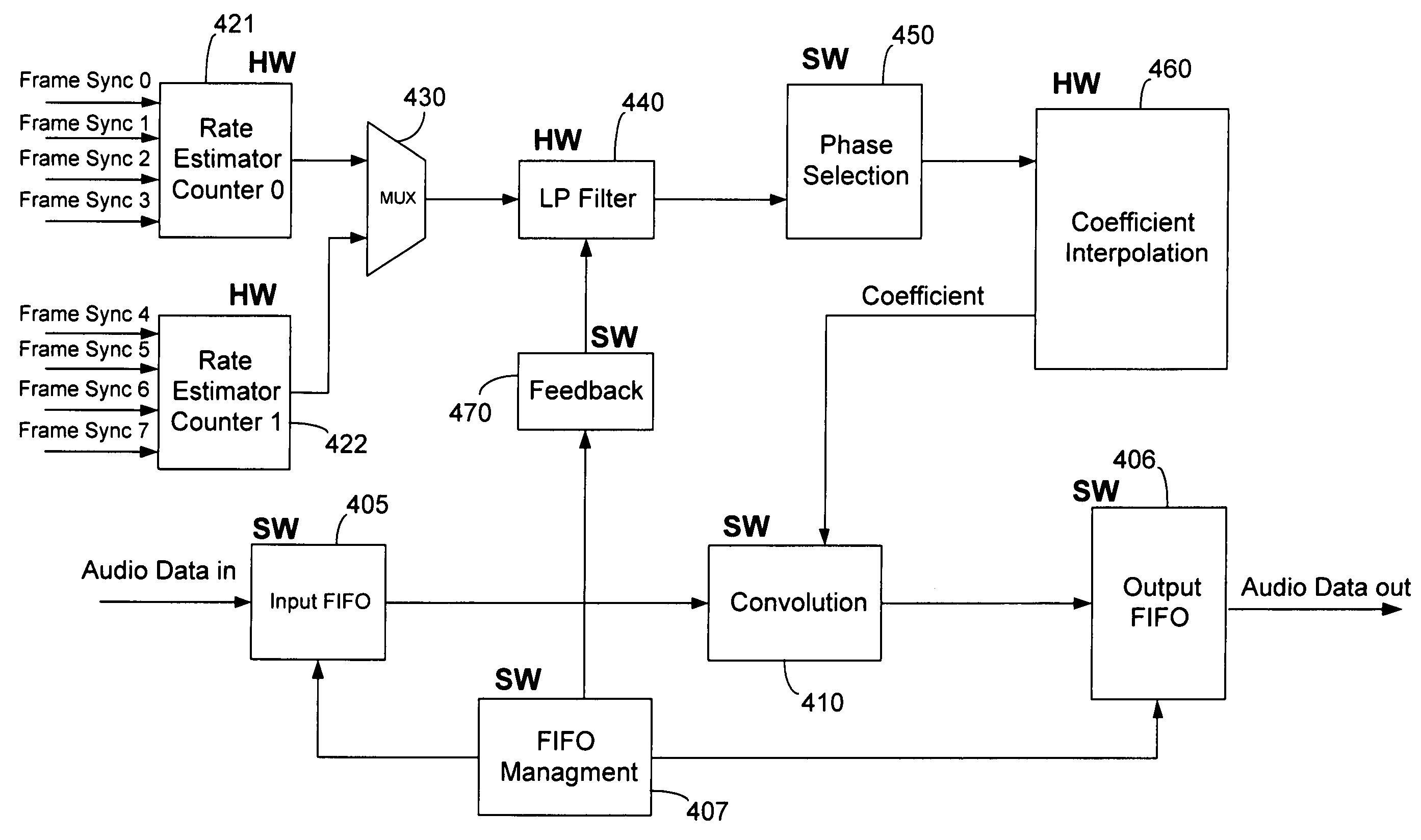

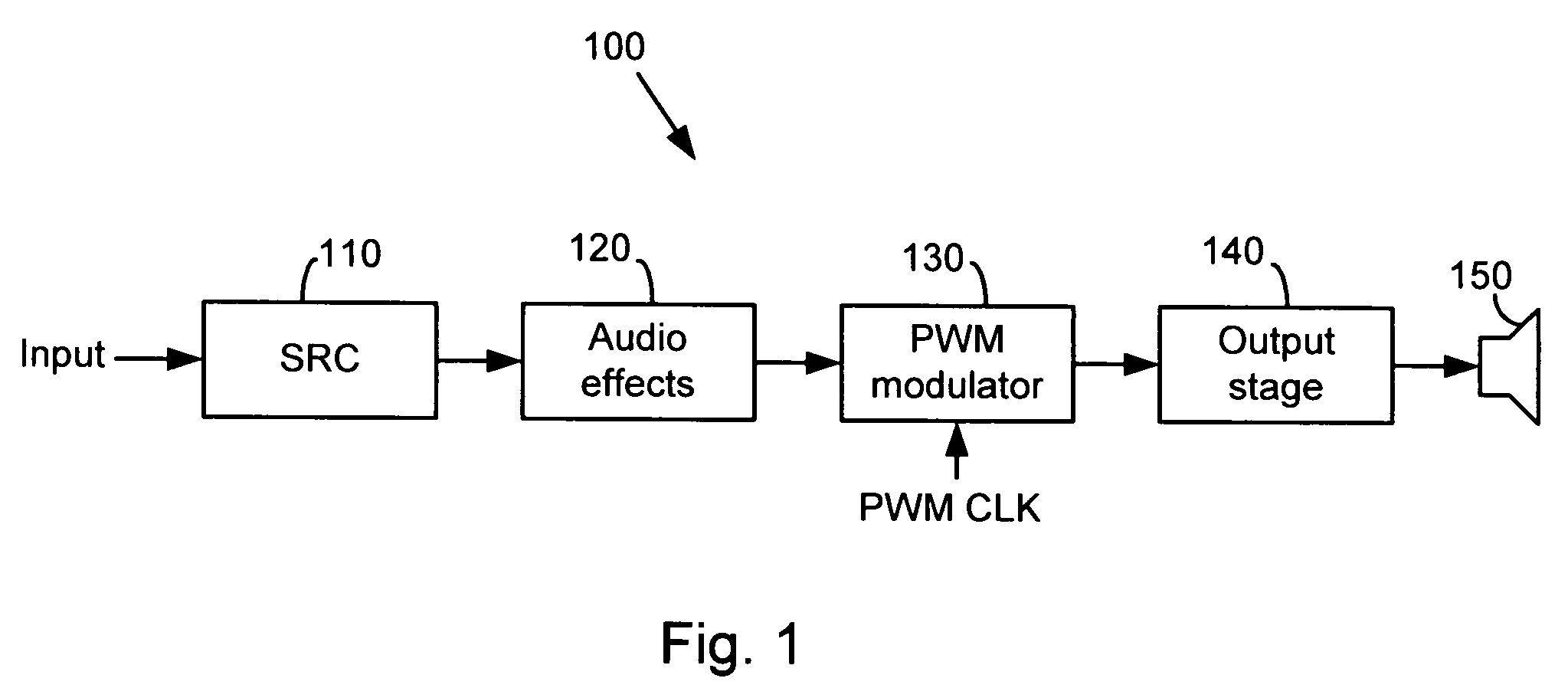

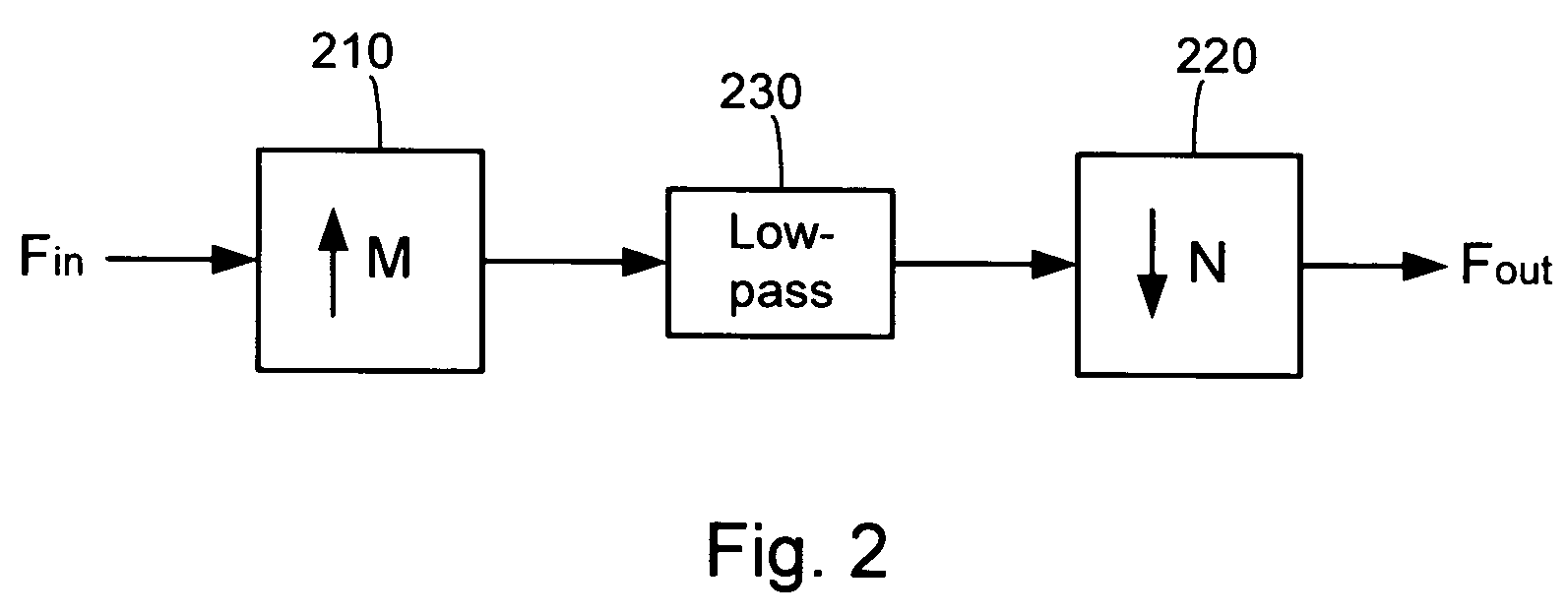

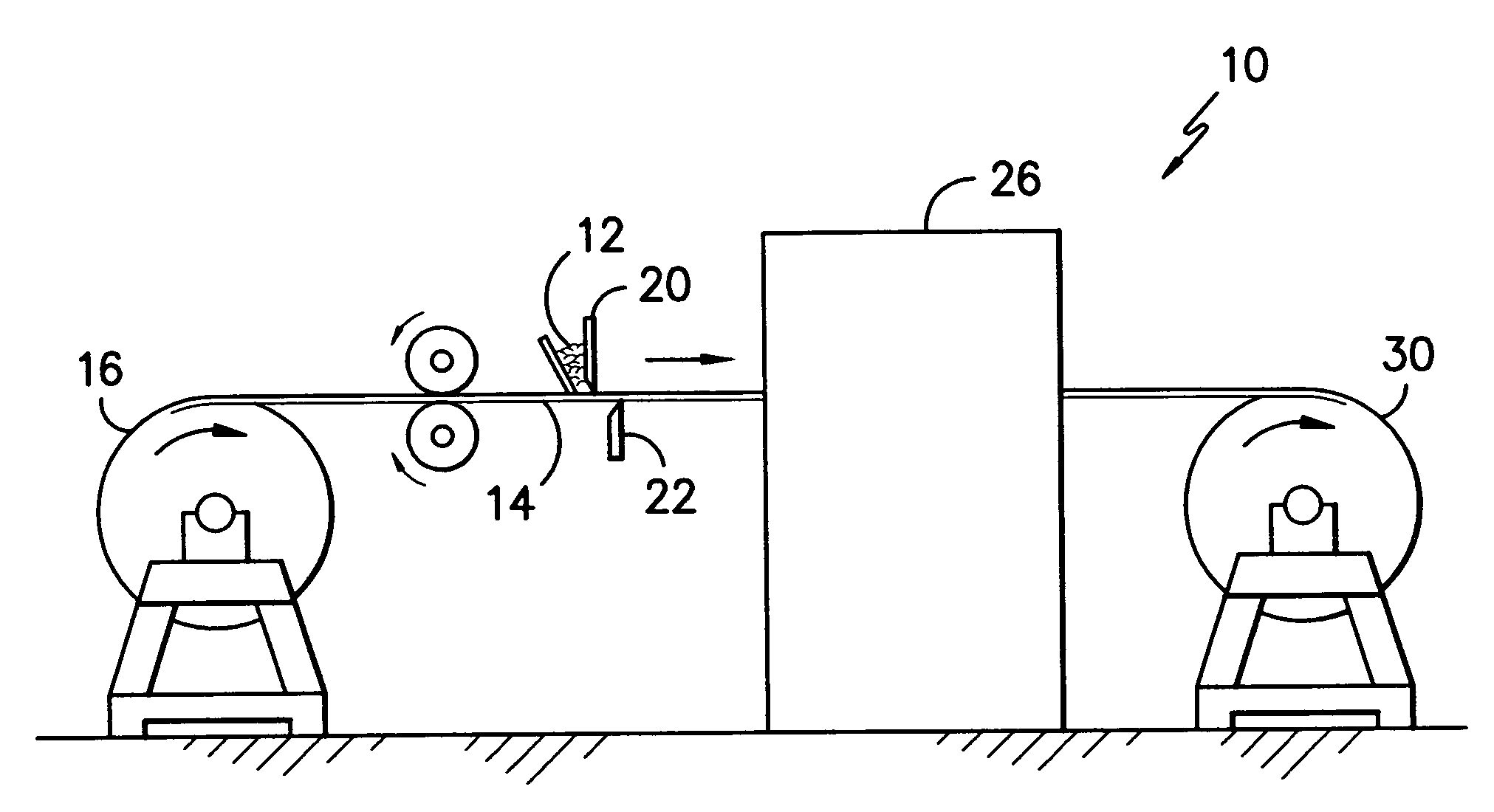

Systems and methods for implementing a sample rate converter using hardware and software to maximize speed and flexibility

ActiveUS7167112B2Maximize performanceReduce cost and complexityDigital technique networkCode conversionSample rate conversionPhase selection

Systems and methods for converting a digital input data stream from a first sample rate to a second, fixed sample rate using a combination of hardware and software components. In one embodiment, a system includes a rate estimator configured to estimate the sample rate of an input data stream, a phase selection unit configured to select a phase for interpolation of a set of polyphase filter coefficients based on the estimated sample rate, a coefficient interpolator configured to interpolate the filter coefficients based on the selected phase, and a convolution unit configured to convolve the interpolated filter coefficients with samples of the input data stream to produce samples of a re-sampled output data stream. One or more hardware or software components are shared between multiple channels that can process data streams having independently variable sample rates.

Owner:INTERSIL INC

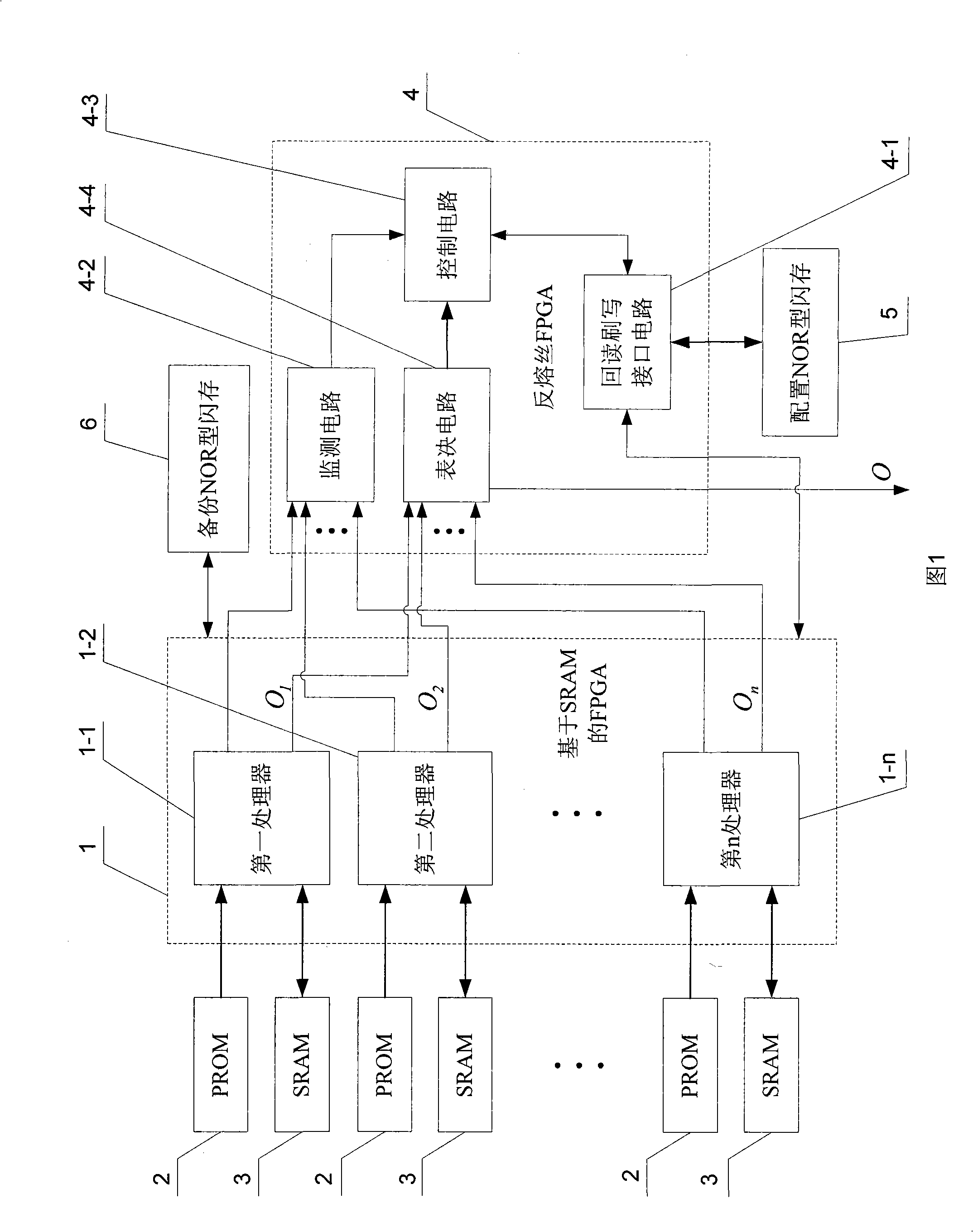

Multi-core onboard spacecraft computer based on FPGA

InactiveCN101493809AImprove performanceRetain flexibilityArchitecture with multiple processing unitsComputer basedSatellite

The invention relates to a multi-core satellite-bone computer, belonging to the data processing technical field of aerospace and aiming at solving the problem of slow processing speed of the satellite-bone computer by adopting an ASIC software realization mode. The satellite-bone computer comprises an FPGA based on an SRAM, n PROMS, n SRAMS, an anti-fuse FPGA and a configuration NOR type flash memory, wherein the FPGA based on the SRAM forms a multi-core structure with n processors, the anti-fuse FPGA comprises a read-back brush write interface circuit, a monitoring circuit and a control circuit, the monitoring circuit monitors the health state of the n processors, if an abnormal part needs reconstruction, the read-back brush write interface circuit reads the configuration file of the FPGA based on the SRAM at set speed, compares the configuration file of the FPGA with an original configuration file, and reconstructs the error parts if different. The multi-core satellite-bone computer can realize automatic switching system function by FPGA hardware programming according to satellite missions.

Owner:HARBIN INST OF TECH

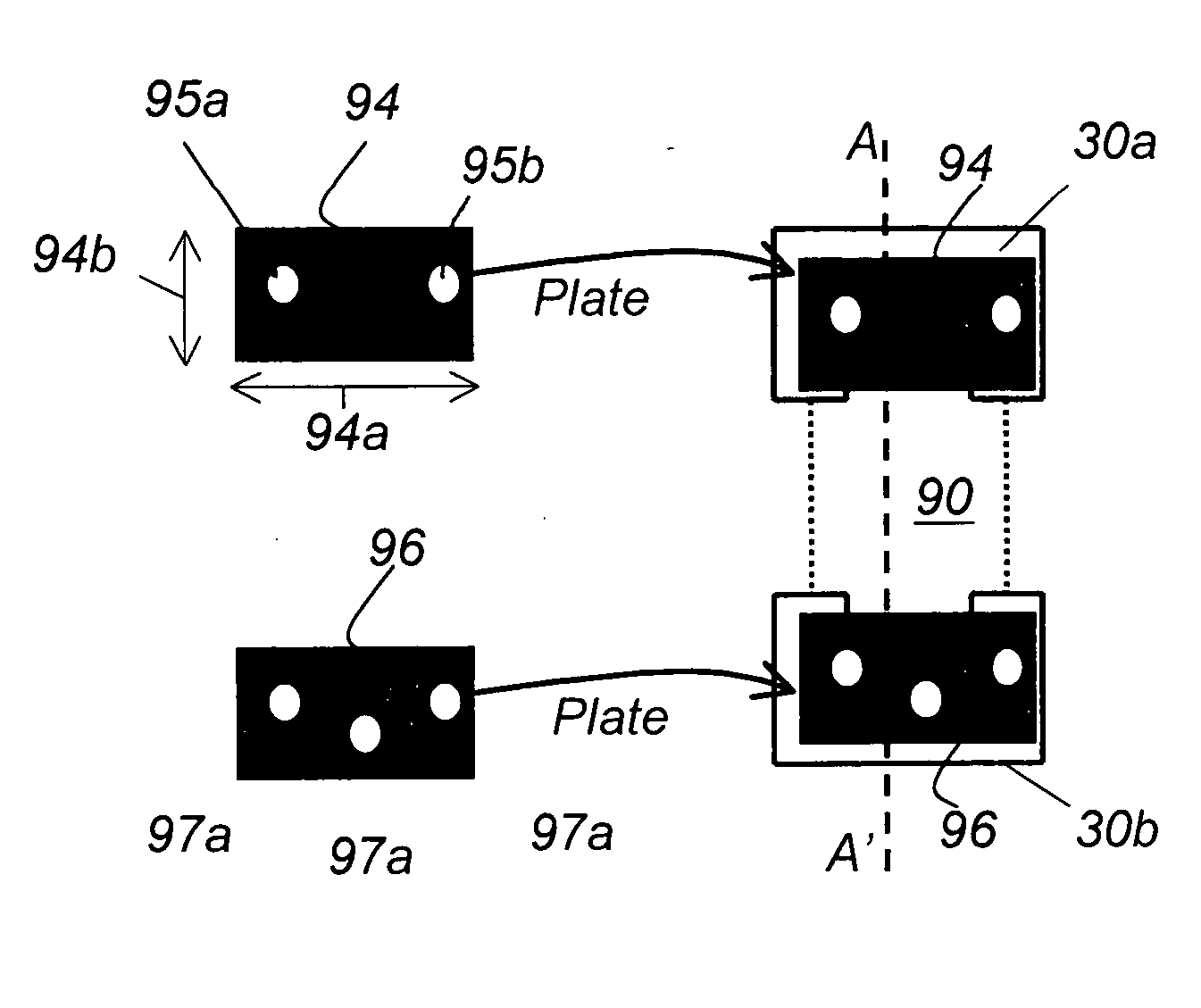

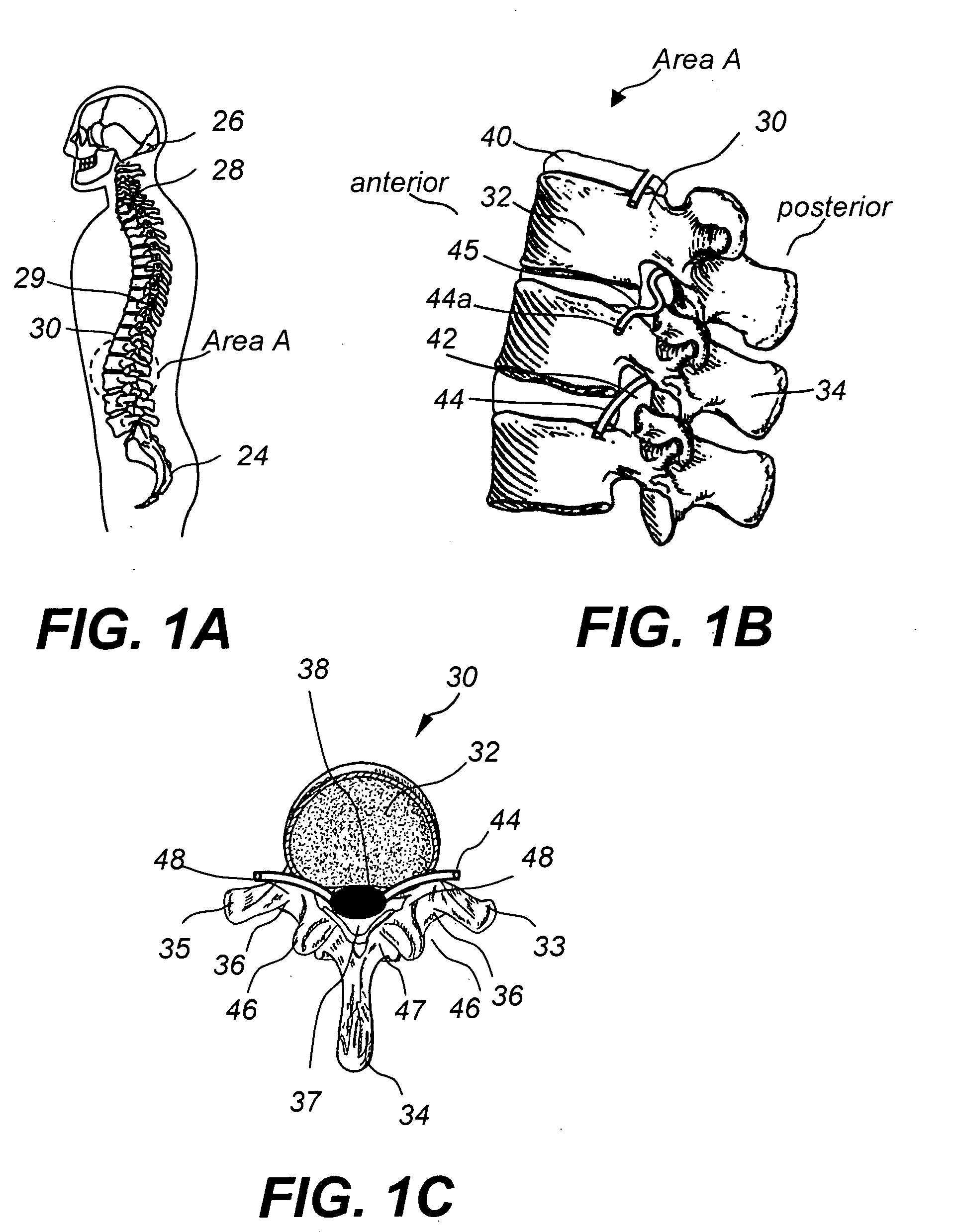

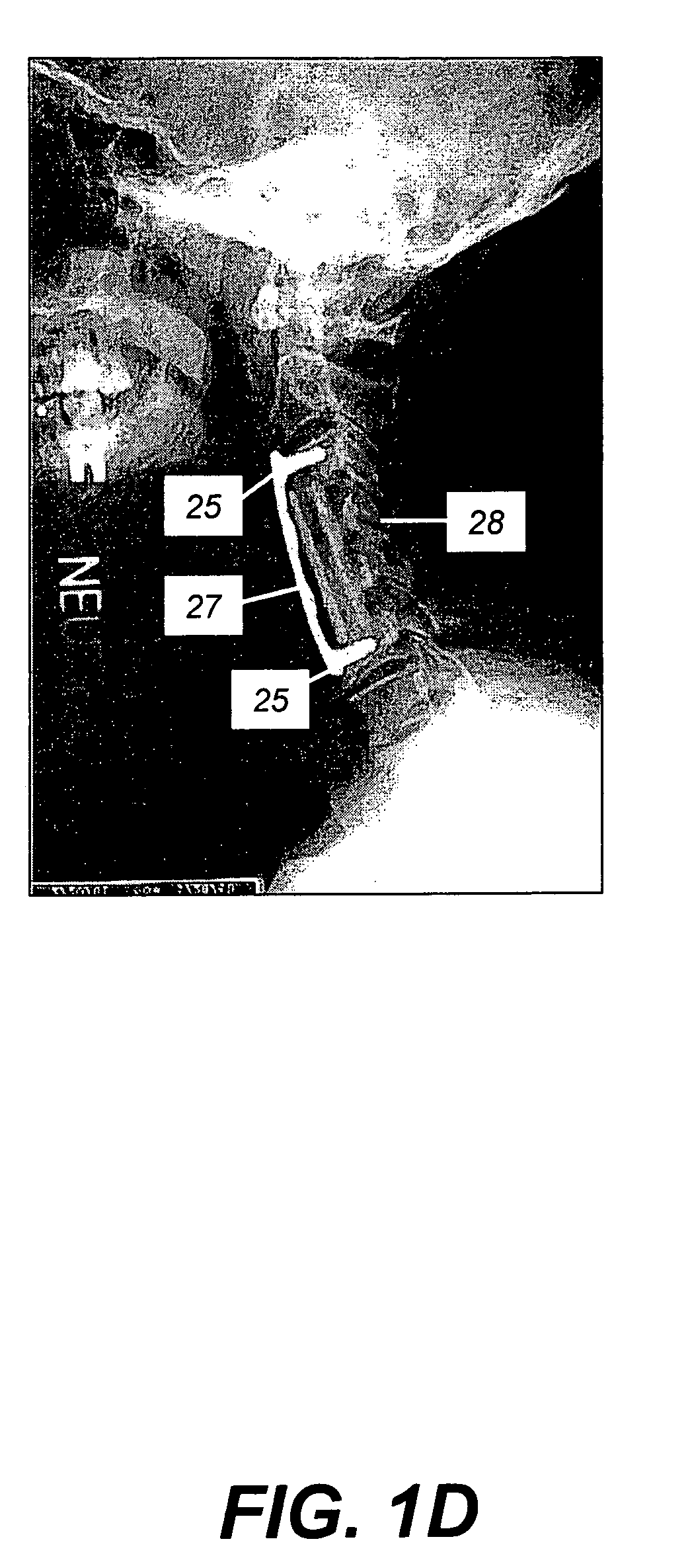

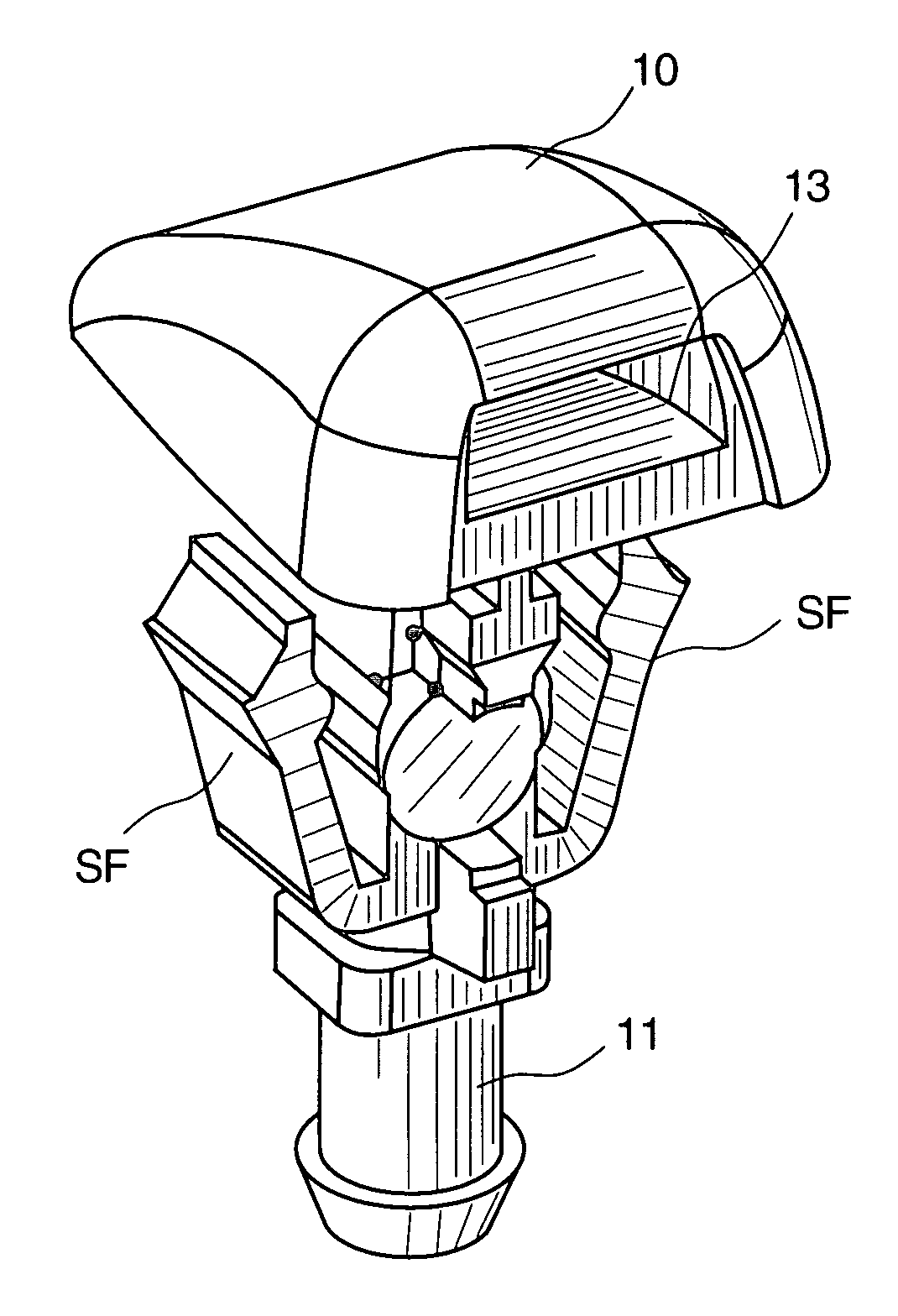

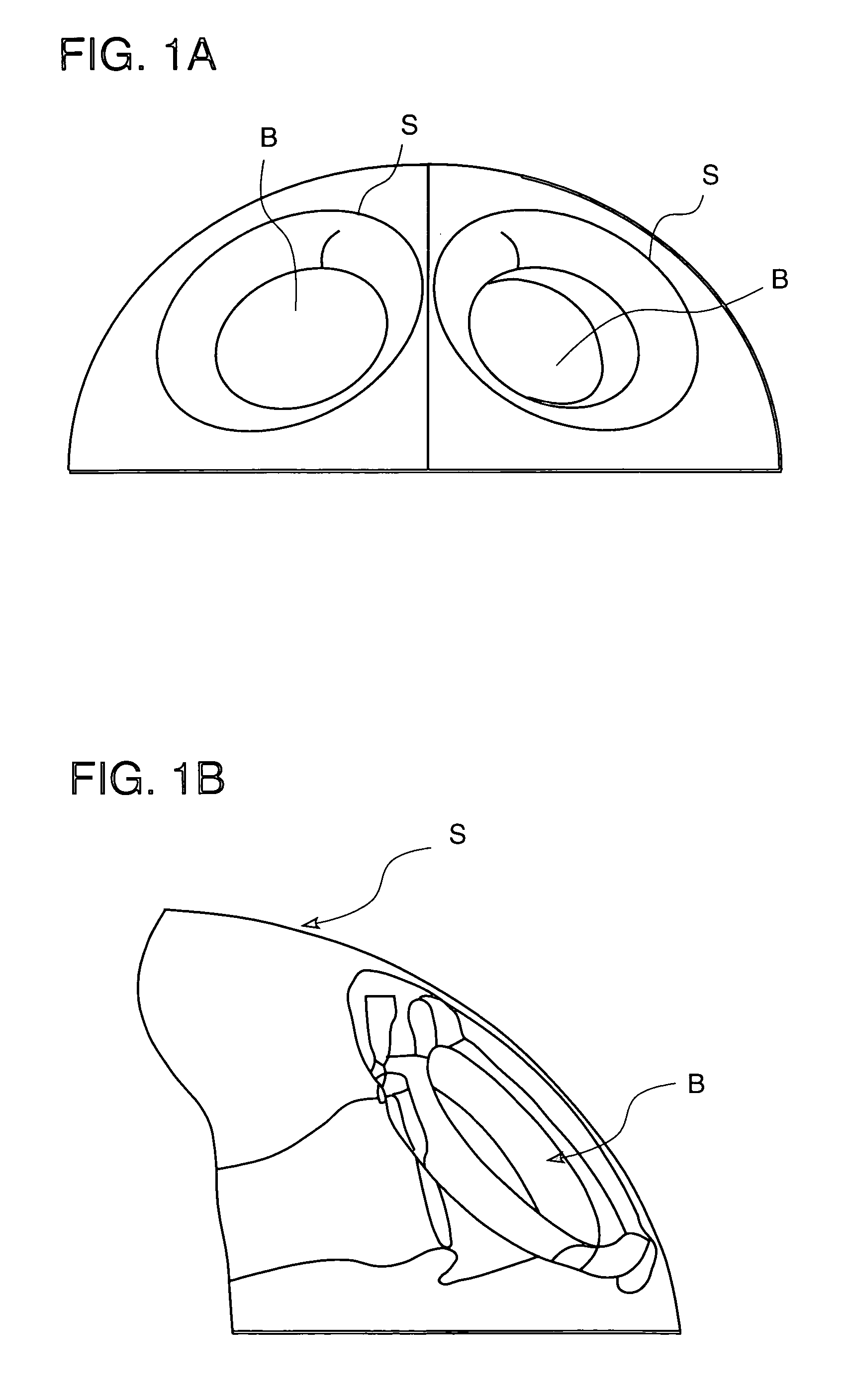

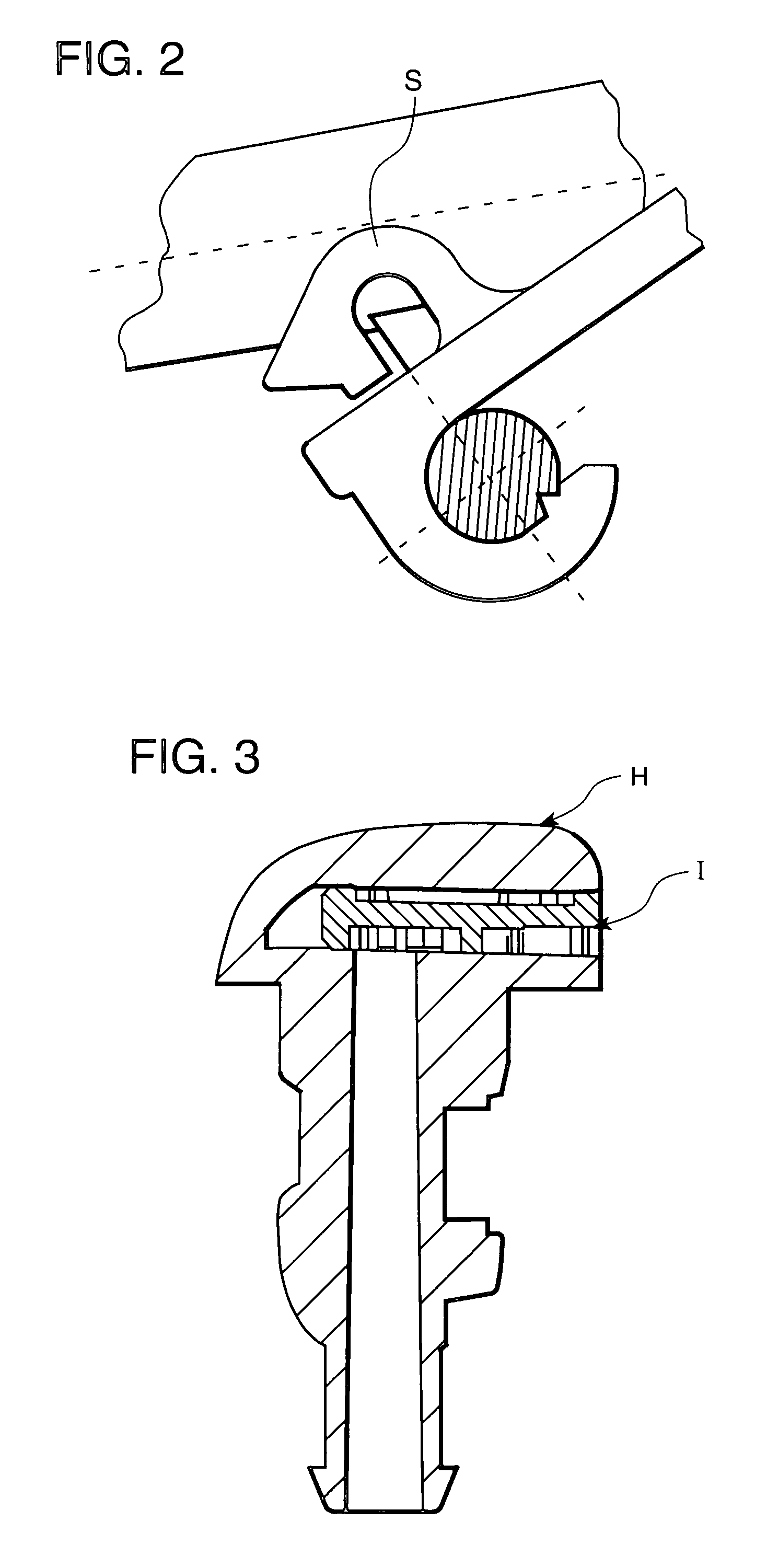

Method and device for kinematic retaining cervical plating

InactiveUS20060009845A1Retain flexibilityEasily placeInternal osteosythesisBone implantSpinal implantVertebra

A spinal implant assembly for replacing intervertebral elements between a first spinal vertebra and an adjacent second spinal vertebra includes an intervertebral implant for inserting between the first and second spinal vertebrae and a first kinematic retaining plate. The intervertebral implant comprises a body having a top surface, a bottom surface, and a first appendage extending from the top surface of the intervertebral implant. The first appendage is adapted to fit within and form a tongue and groove attachment with a first opening formed in the first spinal vertebra. The first kinematic retaining plate is attached to the first spinal vertebra so that it secures the first appendage in the first opening. The intervertebral implant further comprises a second appendage extending from the bottom surface and the second appendage is adapted to fit within and form a tongue and groove attachment with a second opening formed in the second spinal vertebra. A second kinematic retaining plate is attached to the second spinal vertebra so that it secures the second appendage in the second opening.

Owner:SPINEFRONTIER LLS

Intumescent flame retardent compositions

InactiveUS20060030227A1Enhanced level of flame resistanceSuitable for applicationStuffed mattressesSynthetic resin layered productsMedicinePliability

Intumescent compositions which provide enhanced levels of flame resistance and which are suitable for topical and / or infused application to articles to be protected. The intumescent compositions are characterized by substantial pliability upon topical application to and / or infusion or blending within a material to be protected.

Owner:SYNALLOY CORP +1

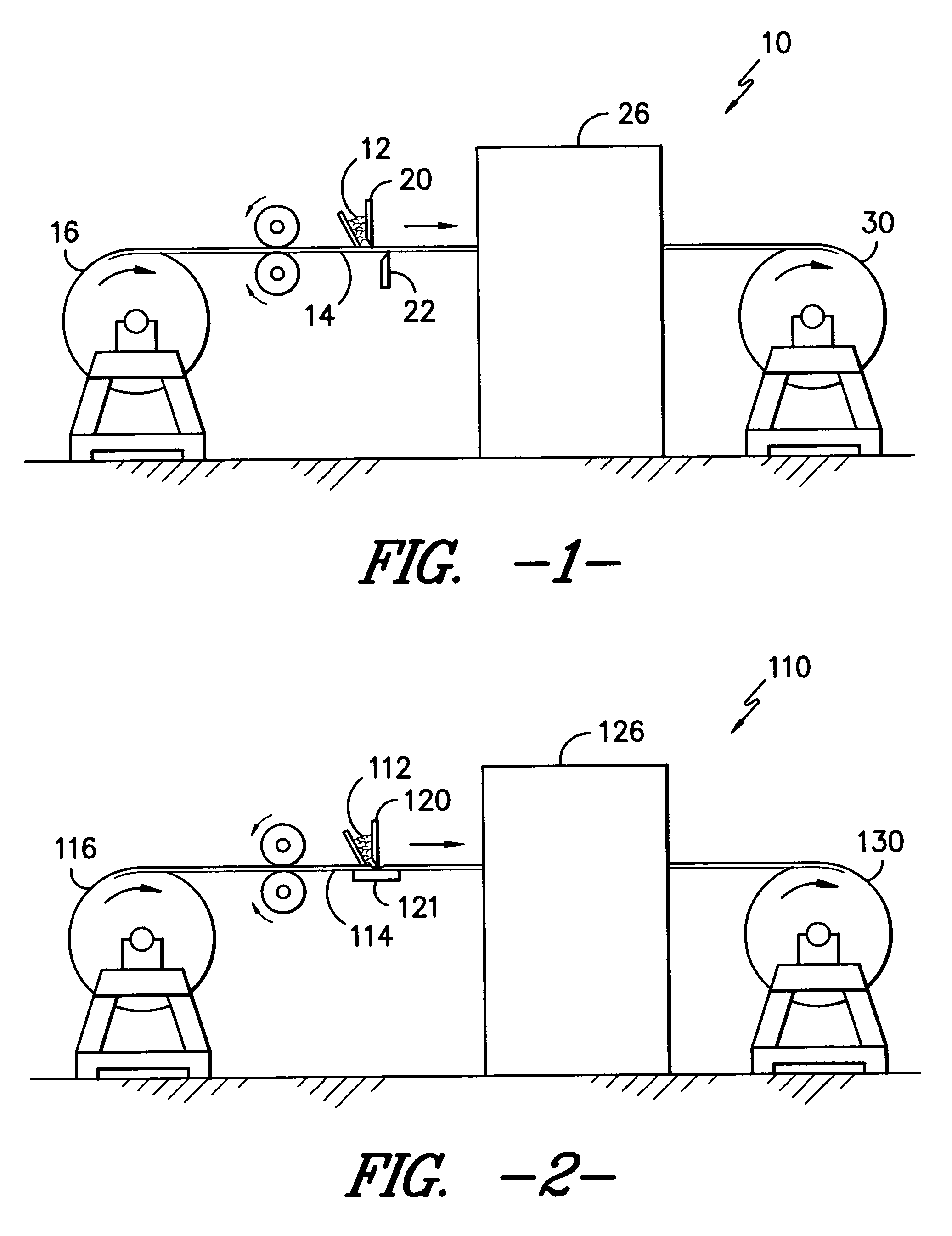

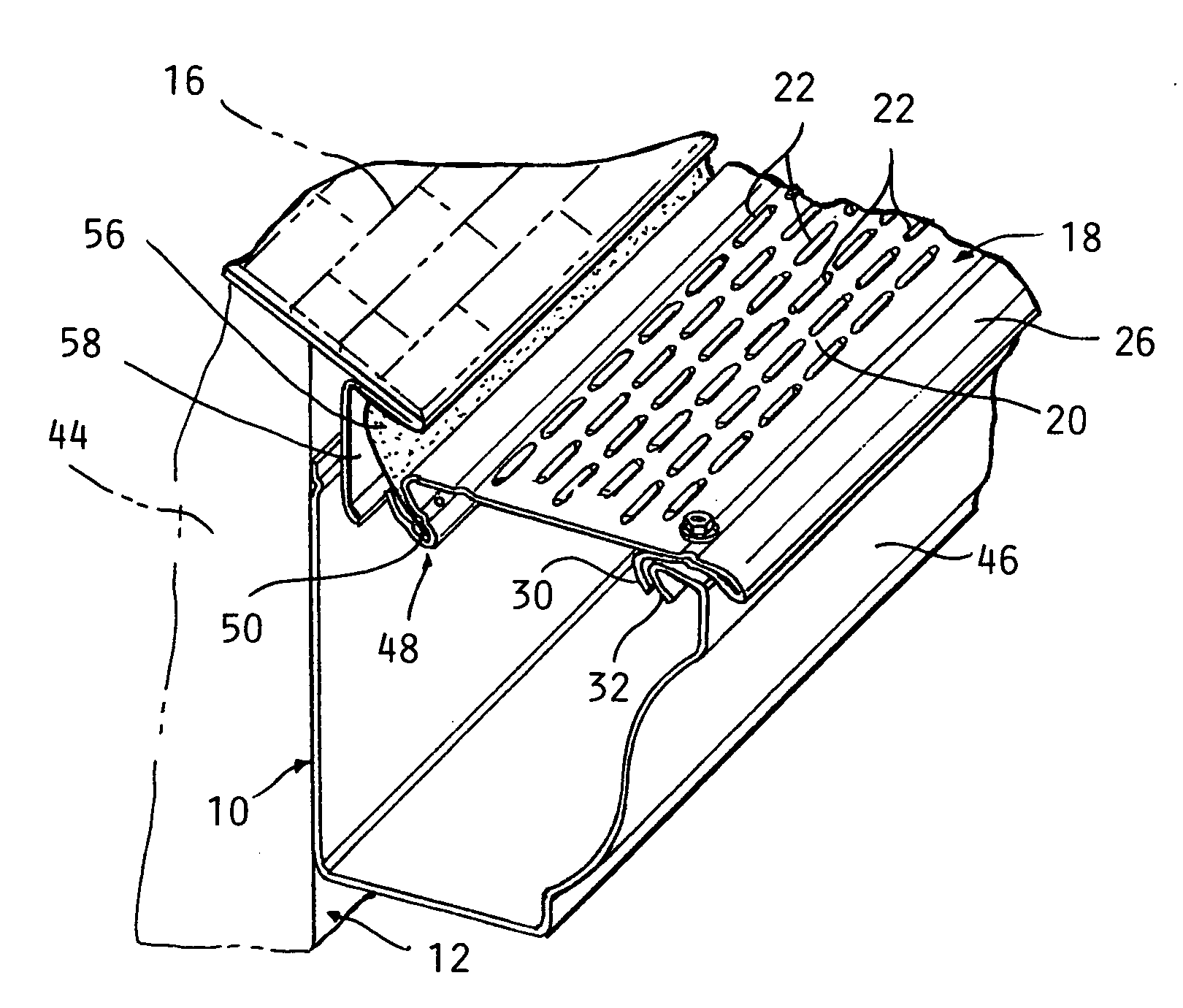

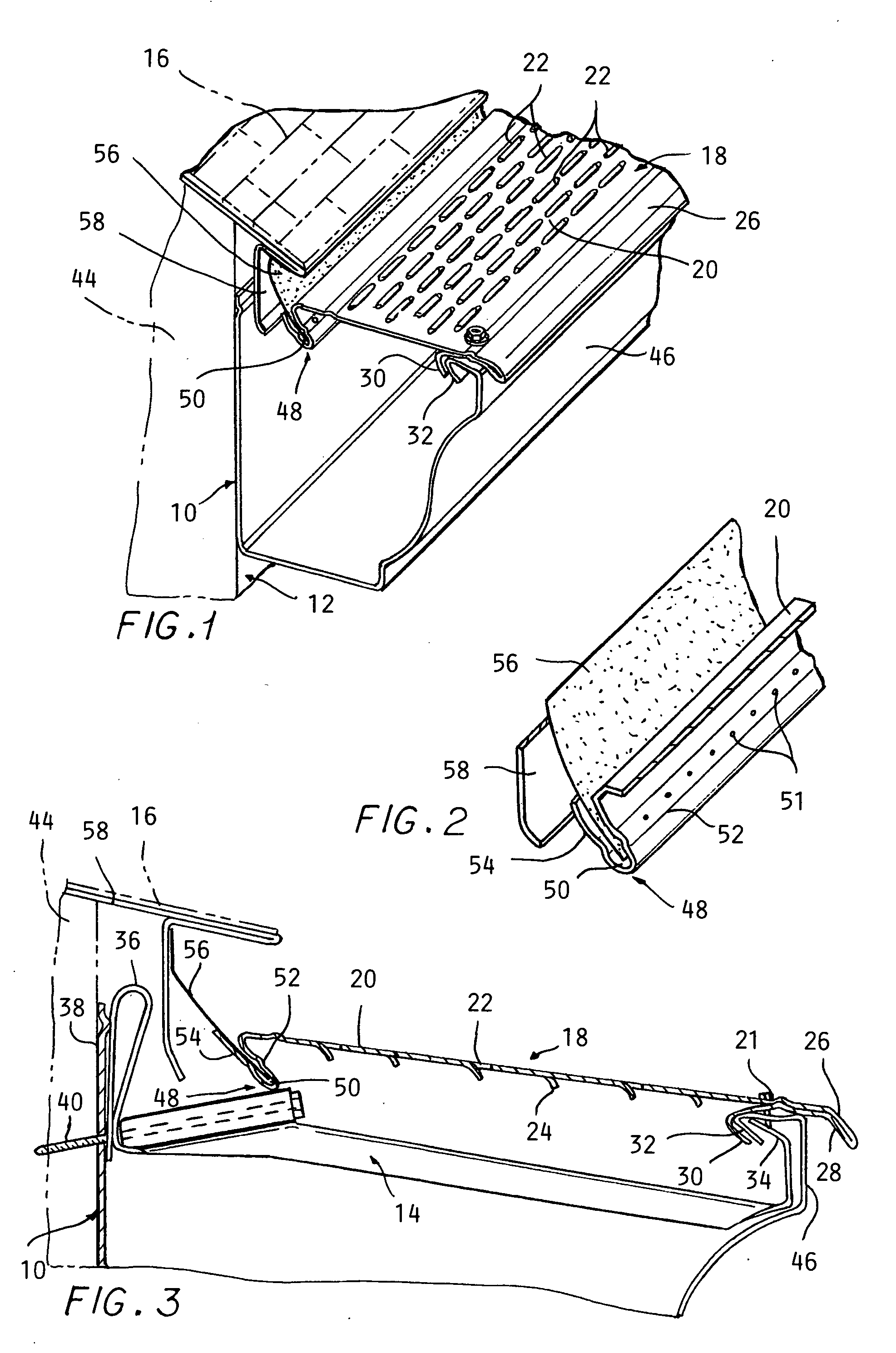

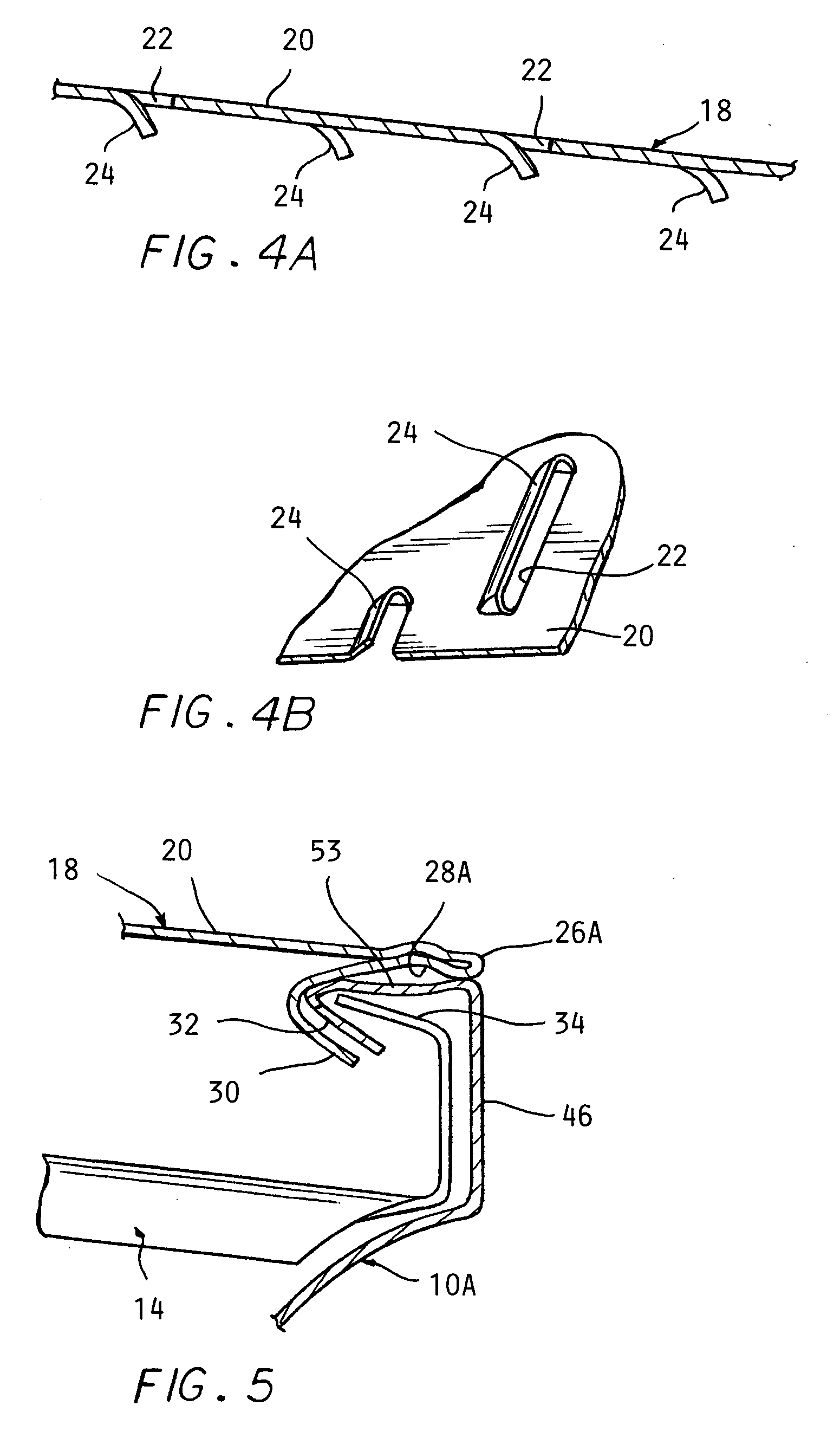

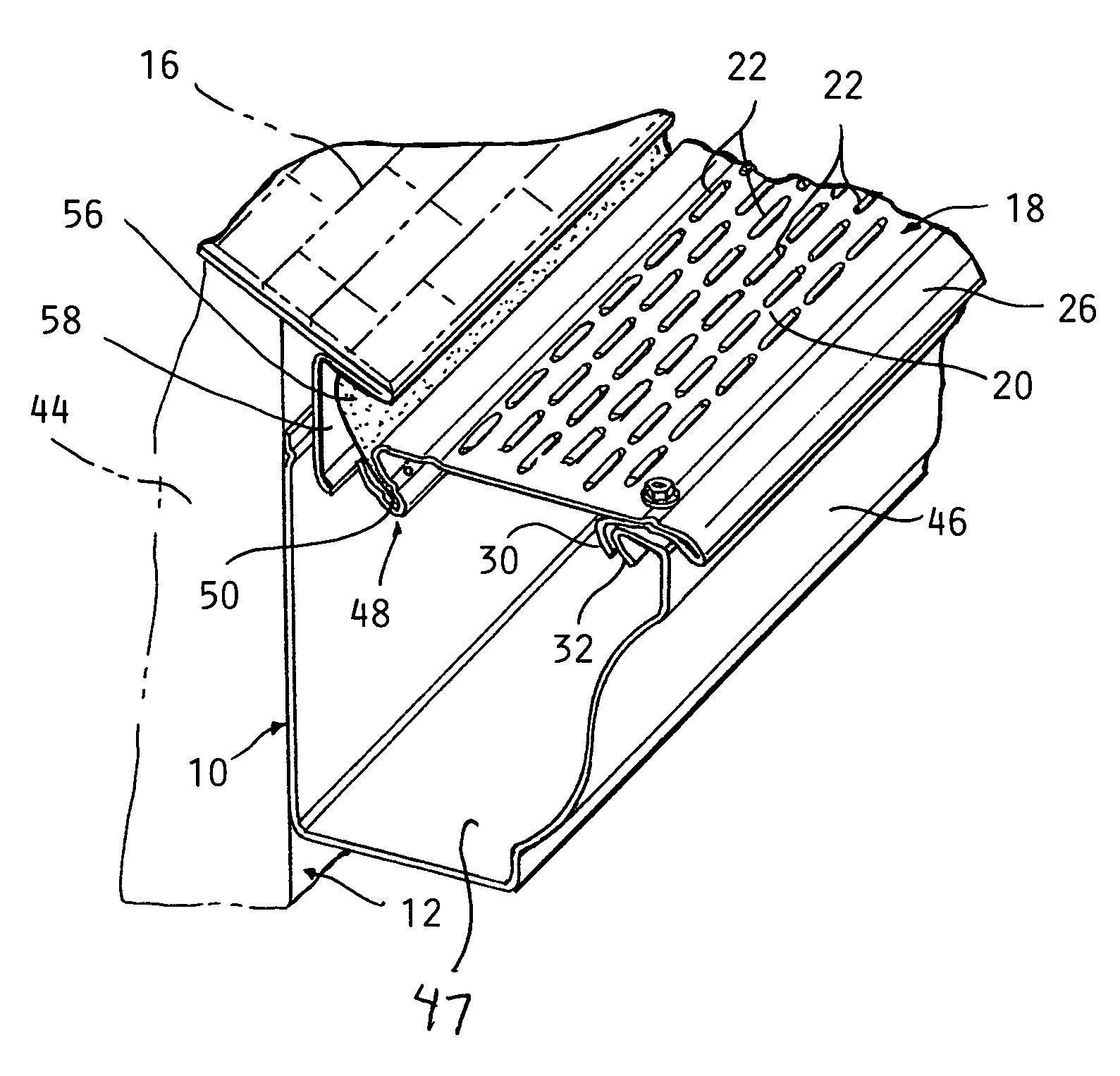

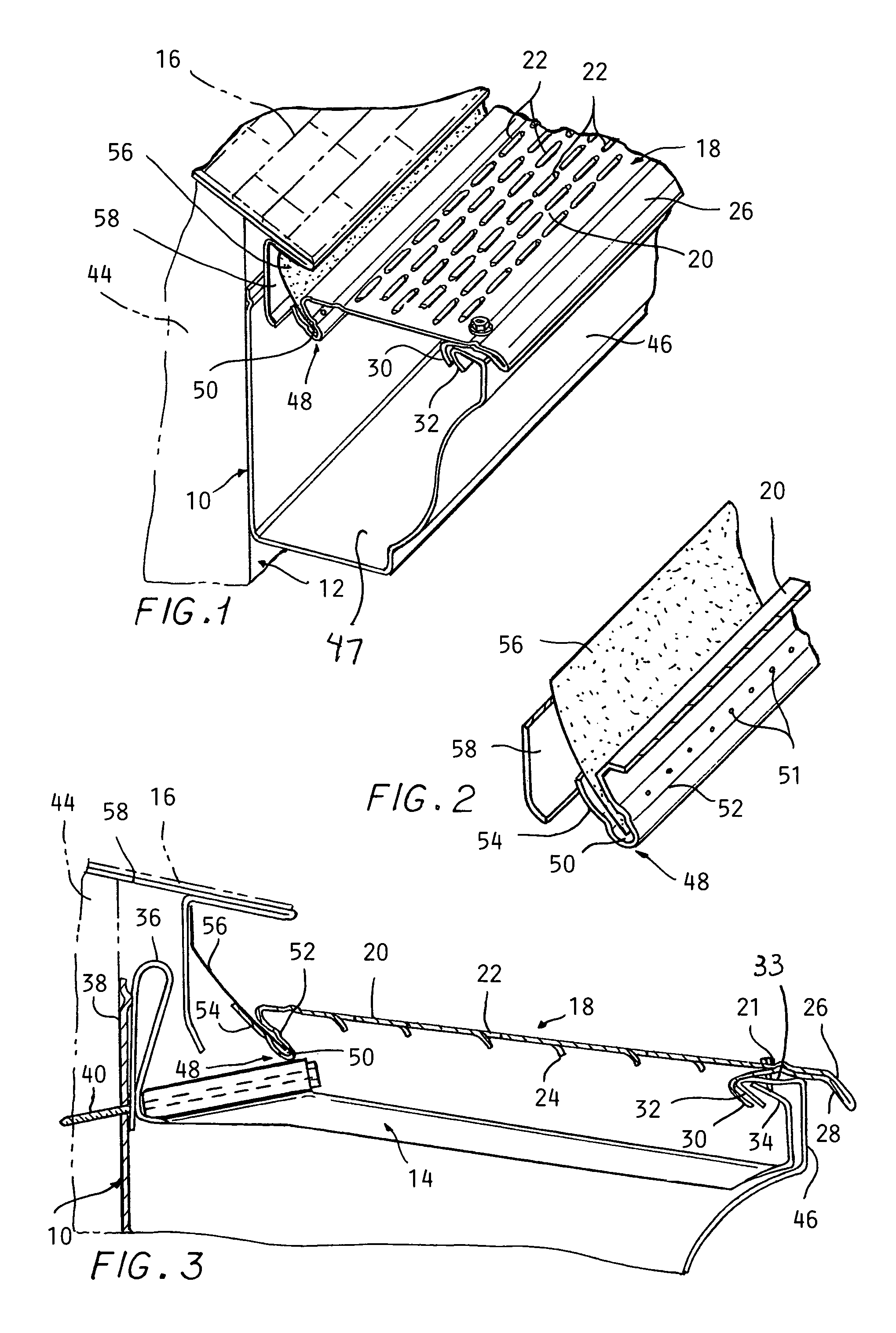

Cutter cover installation

A gutter cover installation for covering a roof eave gutter to prevent debris from entering the gutter includes a main portion of the gutter cover formed with a pattern of openings and an outer edge of the outer side of the gutter cover projecting out and down past an outer wall of the gutter to form a diverter preventing overflow from flowing over the outer surface of the gutter outer wall and thereby avoid staining the same. The gutter cover inner side is held up by segments formed on the inner side of the cover forming a channel which projects down below the main portion and is engaged with a mounting bracket installed within the gutter to be supported thereby. An elastomeric sealing strip is inserted into the channel and projects up and back into engagement with a drip edge or fascia installed at the roof eave.

Owner:JOLY JR ROBERT E +1

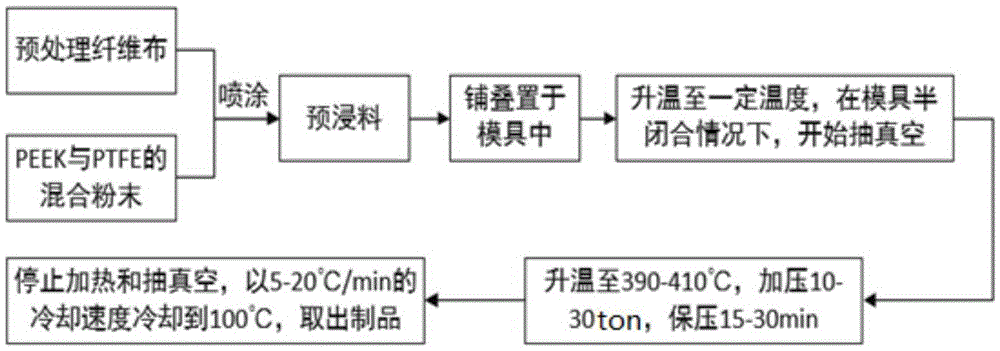

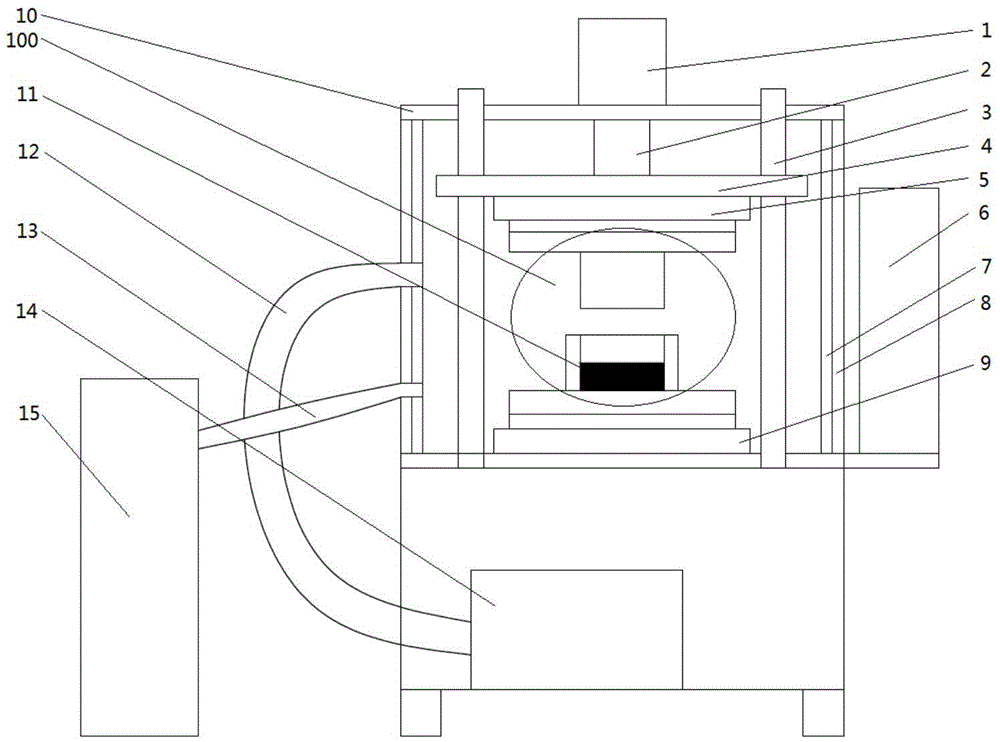

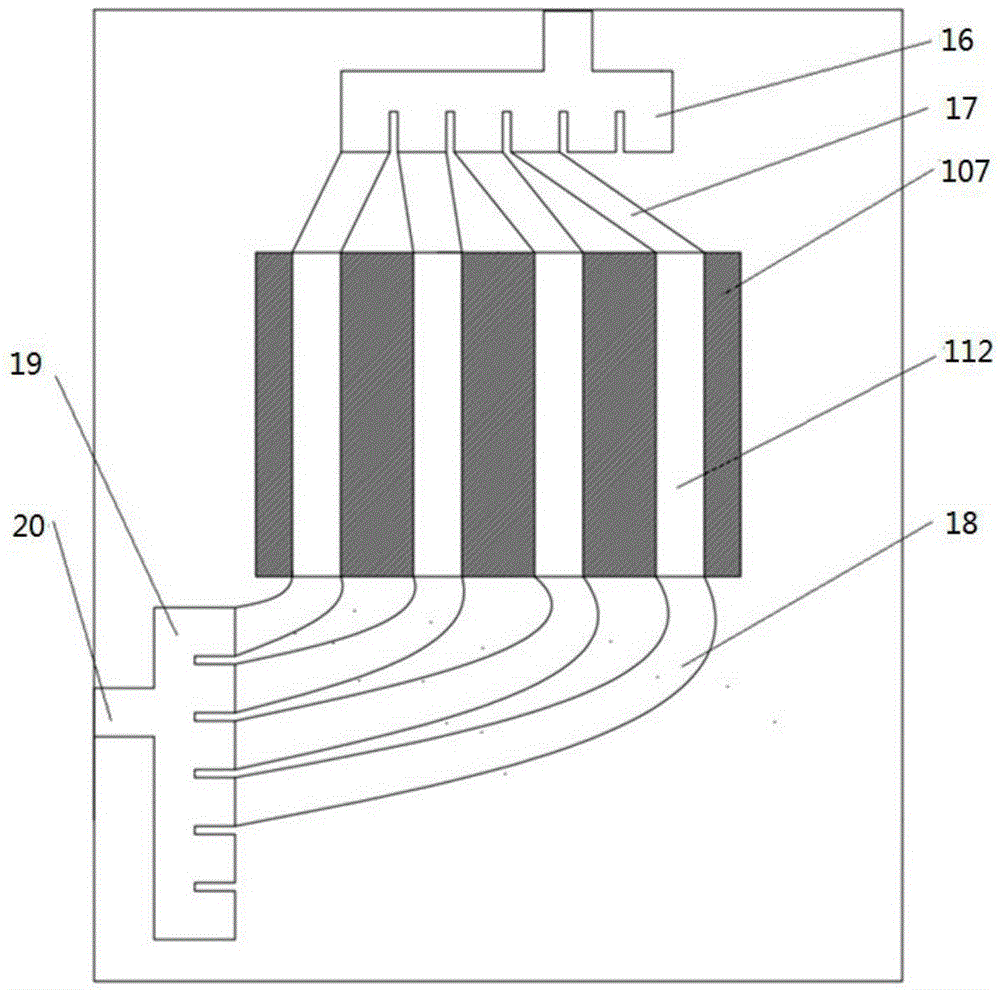

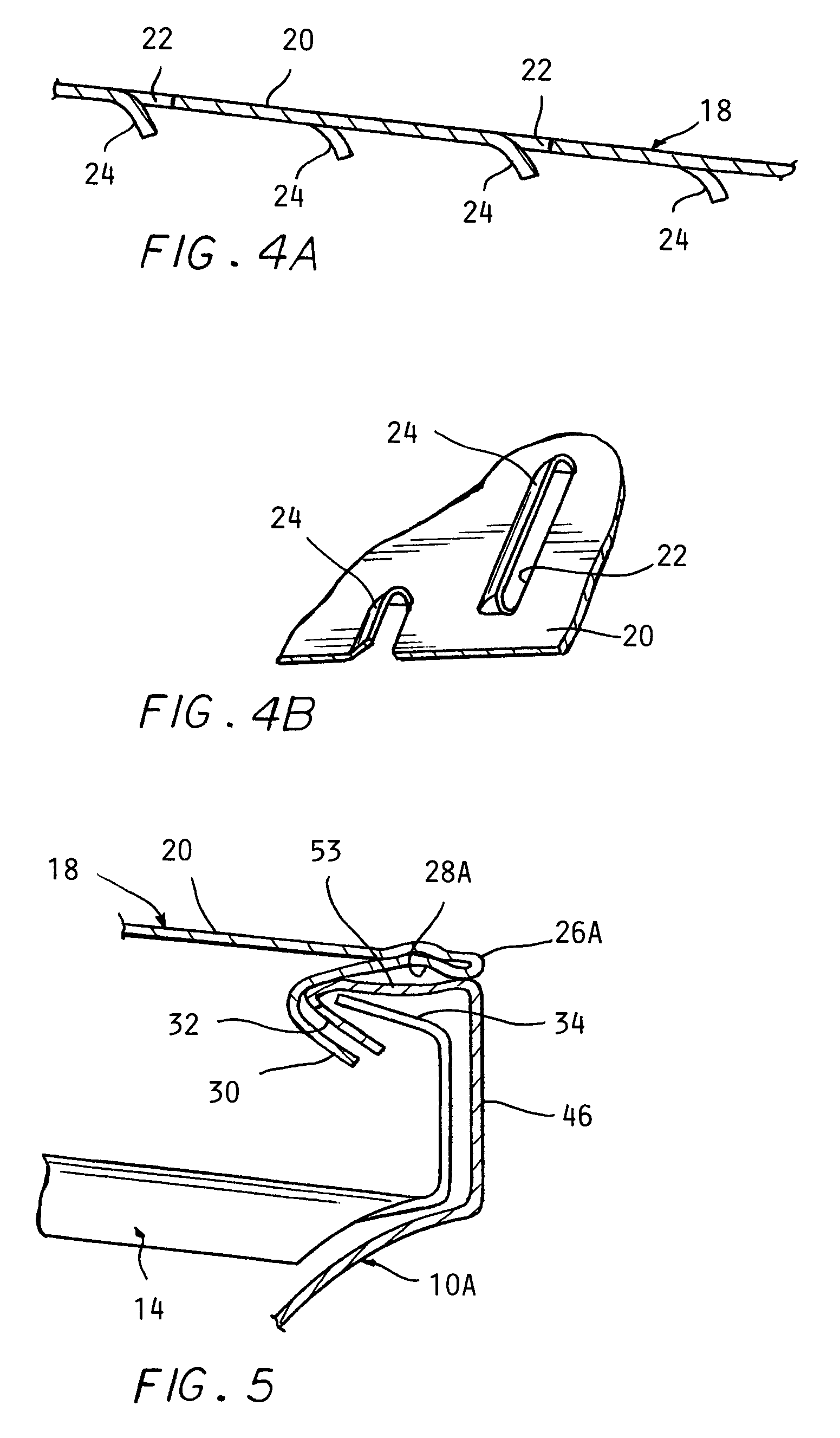

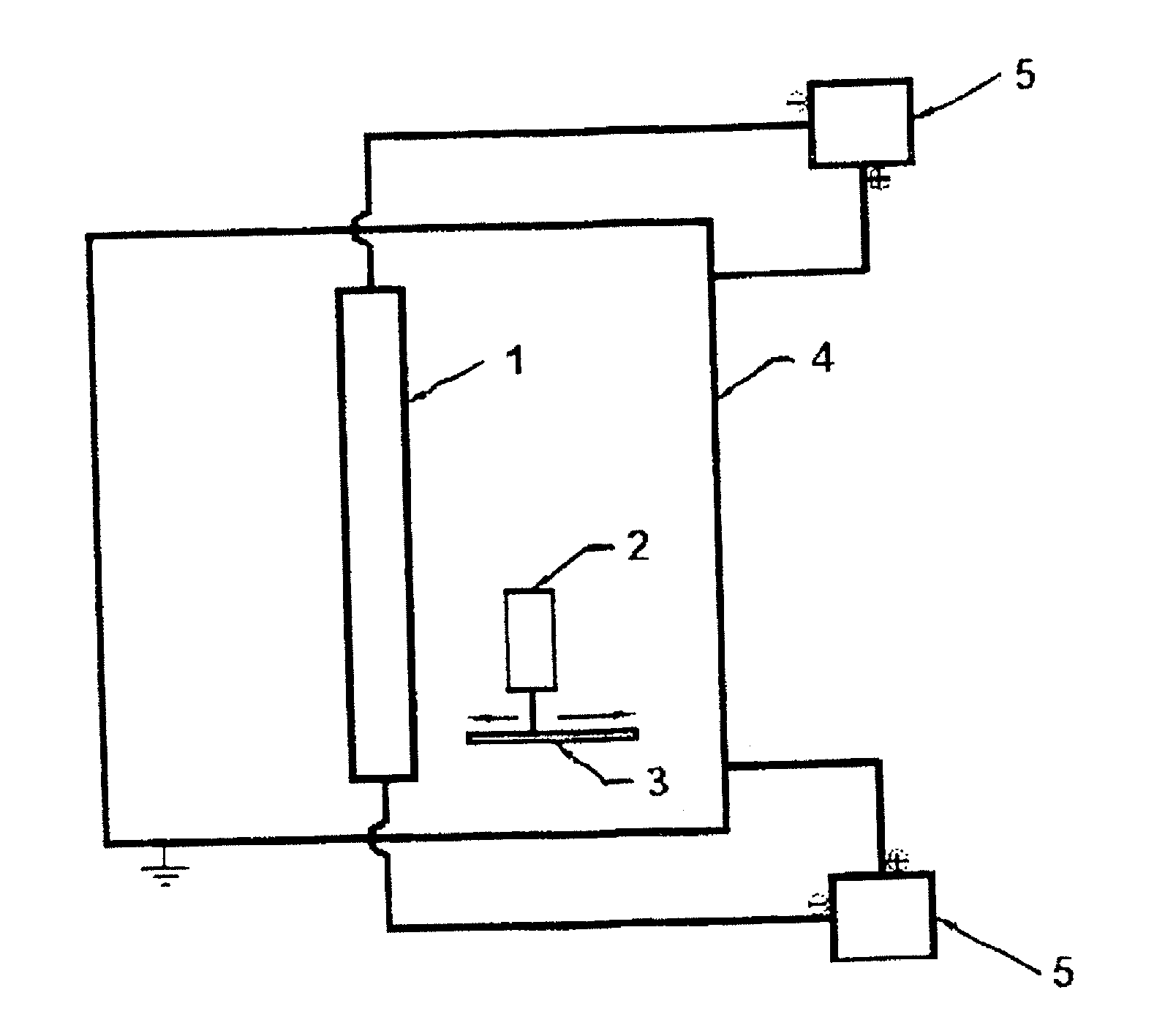

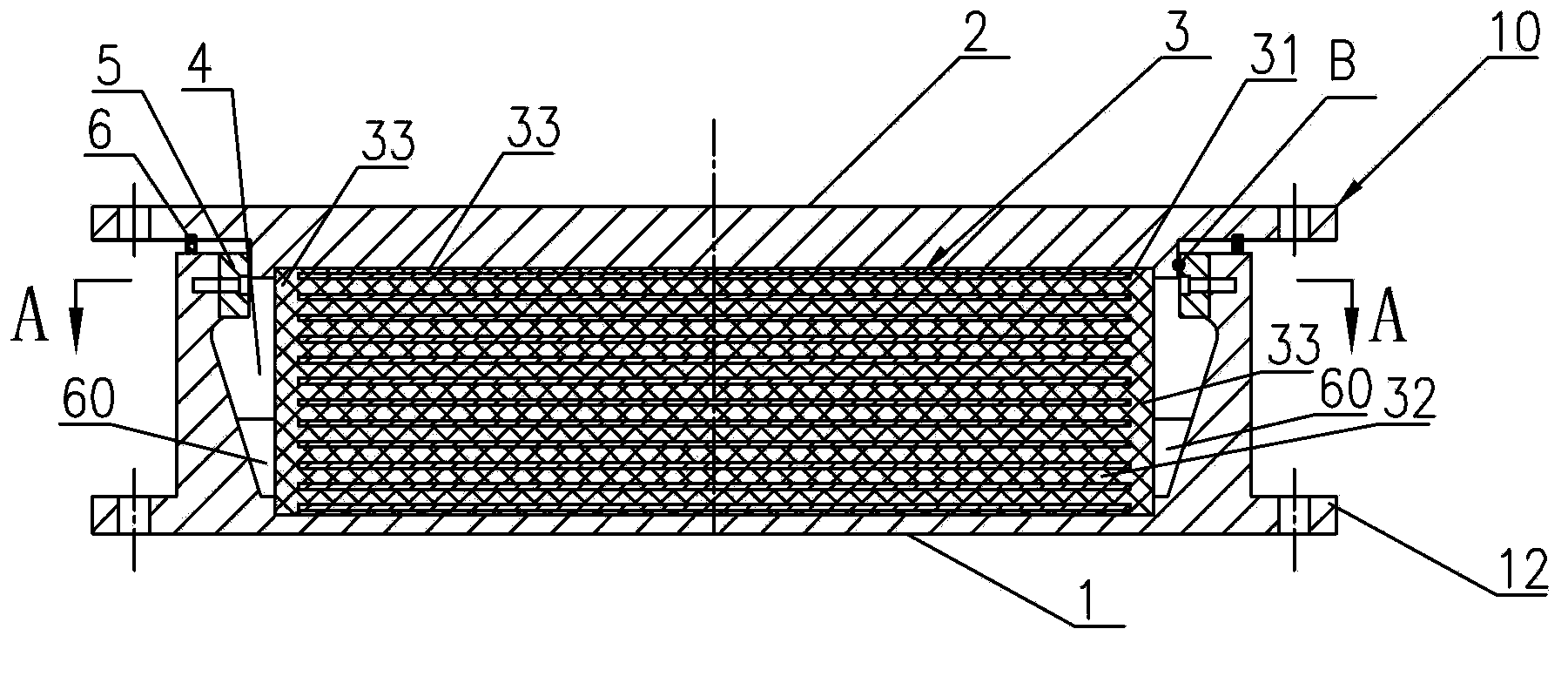

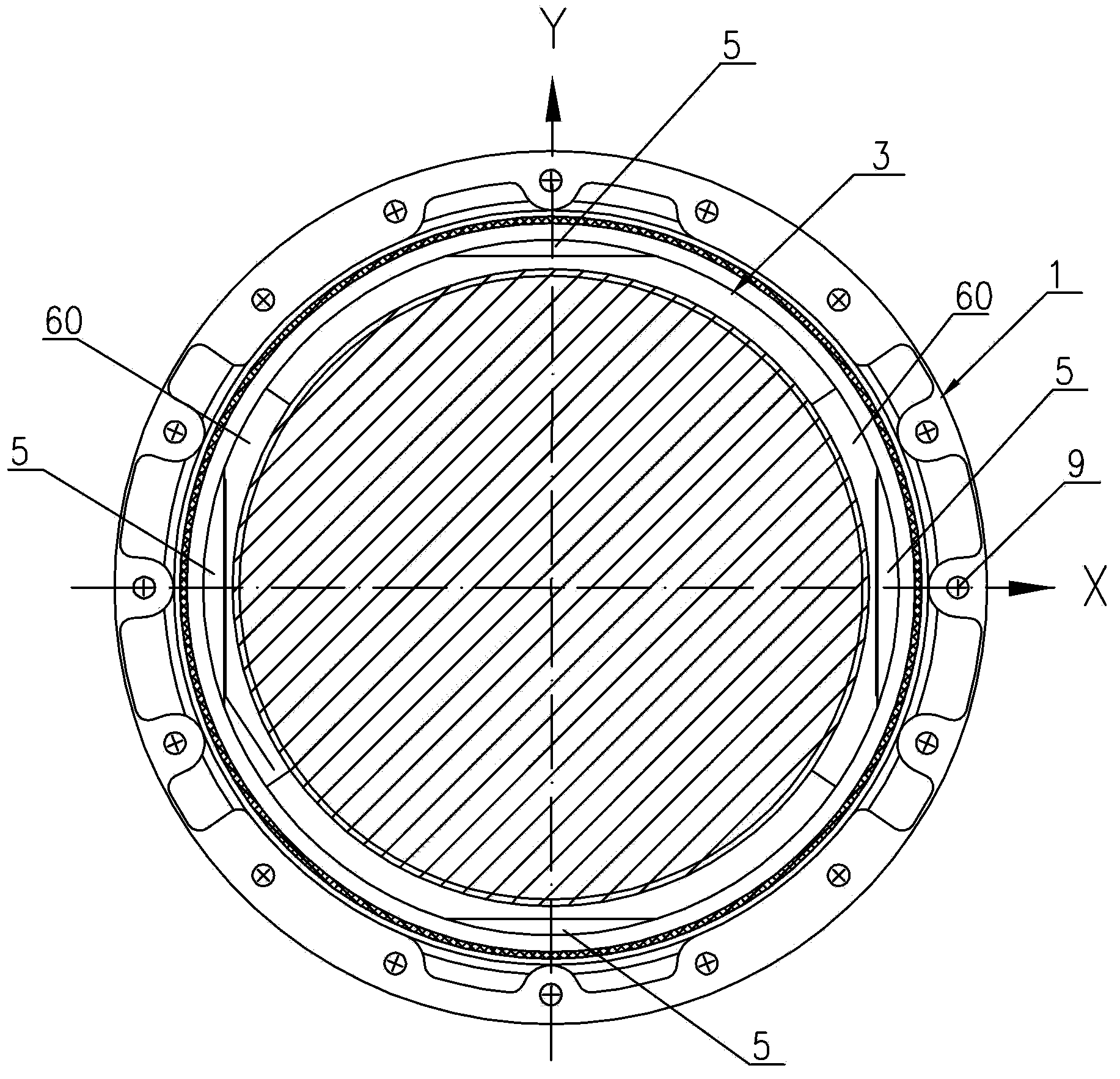

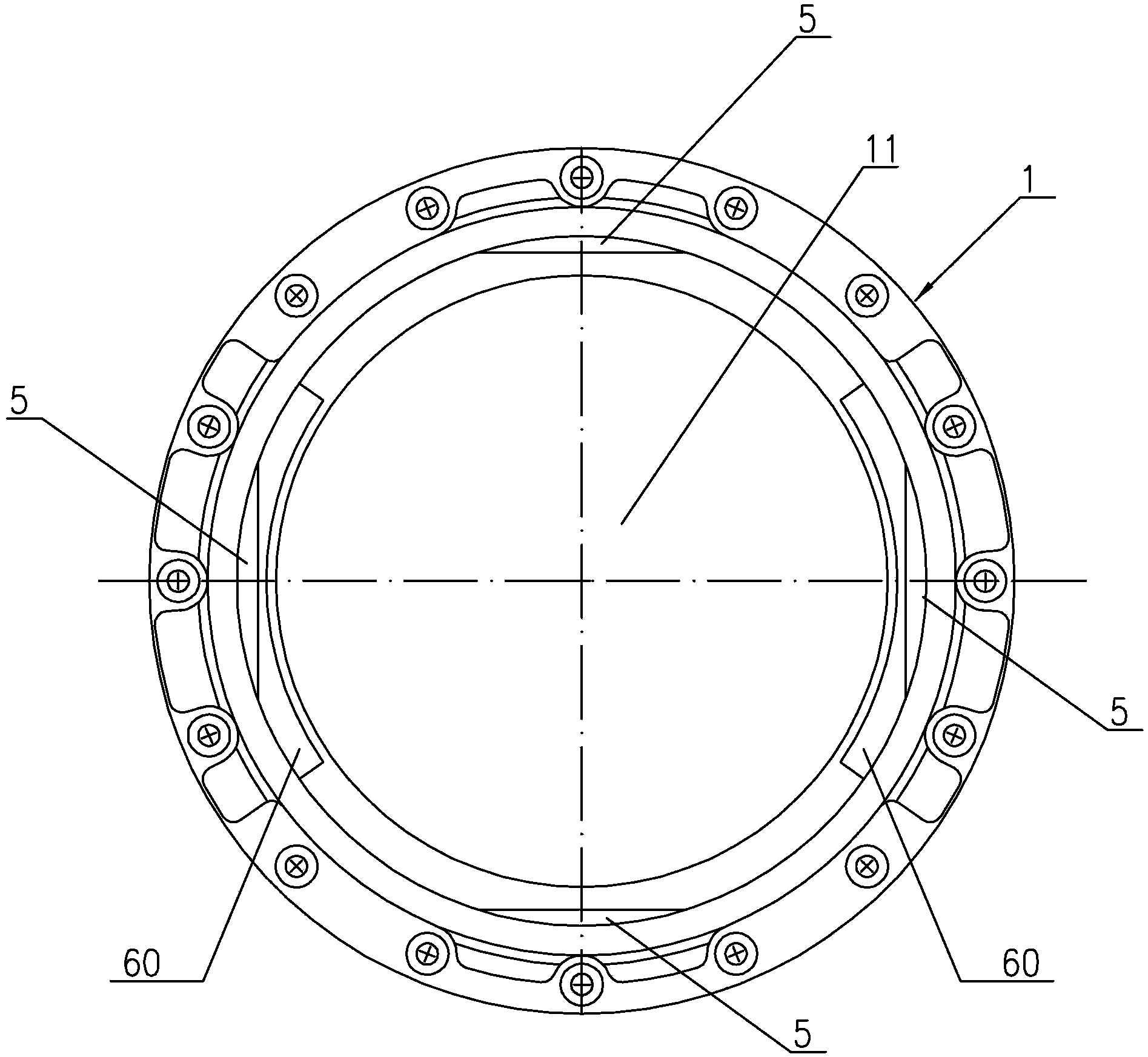

Hot press molding device for carbon fiber enhanced polyether-ether-ketone (PEEK) composite material and technological method thereof

The invention provides a hot press molding device for a carbon fiber enhanced polyether-ether-ketone (PEEK) composite board. The hot press molding device comprises a hydraulic machine, a molding die and a vacuum system. According to the device, a heating unit is separated from the hydraulic machine, and a heating pipe is used for heating the die to achieve a high temperature hot pressing function; by carrying out hot press molding in a vacuum environment, the content of bubbles in resin can be greatly reduced, and the test piece surface smoothness and workpiece performances are improved; a cooling unit is arranged in the die, and cooling speed is regulated by regulating the flow and temperature of high pressure cold air, so as to control the crystallinity of matrix resin and realize flexible selection between high strength and high toughness. Correspondingly, the invention also provides a hot press molding method for the carbon fiber enhanced polyether-ether-ketone (PEEK) composite board. A carbon fiber enhanced polyether-ether-ketone (PEEK) composite board produced by adopting the device and the method disclosed by the invention through hot press molding is simple in production equipment and solves the problems that material internal porosity is large, resin impregnation fiber is insufficient, test piece performance is insufficient, molding cycle is long and the like during production of polyether-ether-ketone resin with high melting point and high viscosity.

Owner:HUAZHONG UNIV OF SCI & TECH

Gutter cover installation

A gutter cover installation for covering a roof eave gutter to prevent debris from entering the gutter includes a main portion of the gutter cover formed with a pattern of openings and an outer edge of the outer side of the gutter cover projecting out and down past an outer wall of the gutter to form a diverter preventing overflow from flowing over the outer surface of the gutter outer wall and thereby avoid staining the same. The gutter cover inner side is held up by segments formed on the inner side of the cover forming a channel which projects down below the main portion and is engaged with a mounting bracket installed within the gutter to be supported thereby. An elastomeric sealing strip is inserted into the channel and projects up and back into engagement with a drip edge or fascia installed at the roof eave.

Owner:JOLY JR ROBERT E +1

Method for packaging organic electronic device

InactiveCN103258955AExtended service lifeKeep bendSolid-state devicesSemiconductor/solid-state device manufacturingComposite filmProcess integration

The invention discloses a method for packaging an organic electronic device. The method for packaging the organic electronic device comprises the following steps that a plurality of layers of composite thin films are deposited on the back side of a lining material before the electronic device is prepared, the layers of composite thin films are deposited on the surface of the organic electronic device after the electronic device is prepared. By the adoption of a chip scale packaging method, a packaging process is integrated to a device manufacturing technological process, and therefore the original method of firstly manufacturing the device on a wafer and then the device is singly packaged after being cut is replaced. The method for packaging the organic electronic device has the advantages of improving efficiency and reducing cost. By the adoption of packaging through organic / inorganic layers of composite thin films in an innovative mode, water and oxygen can be isolated, therefore, the service life of the organic electronic device is greatly prolonged, flexible packaging can be achieved, and foldable and bending performance of the organic electronic device can be saved to the maximum. Eventually, according to the method for packaging the organic electronic device, low-temperature film formation below 120 DEG C is achieved, and heat damage to the device and plastic lining is reduced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

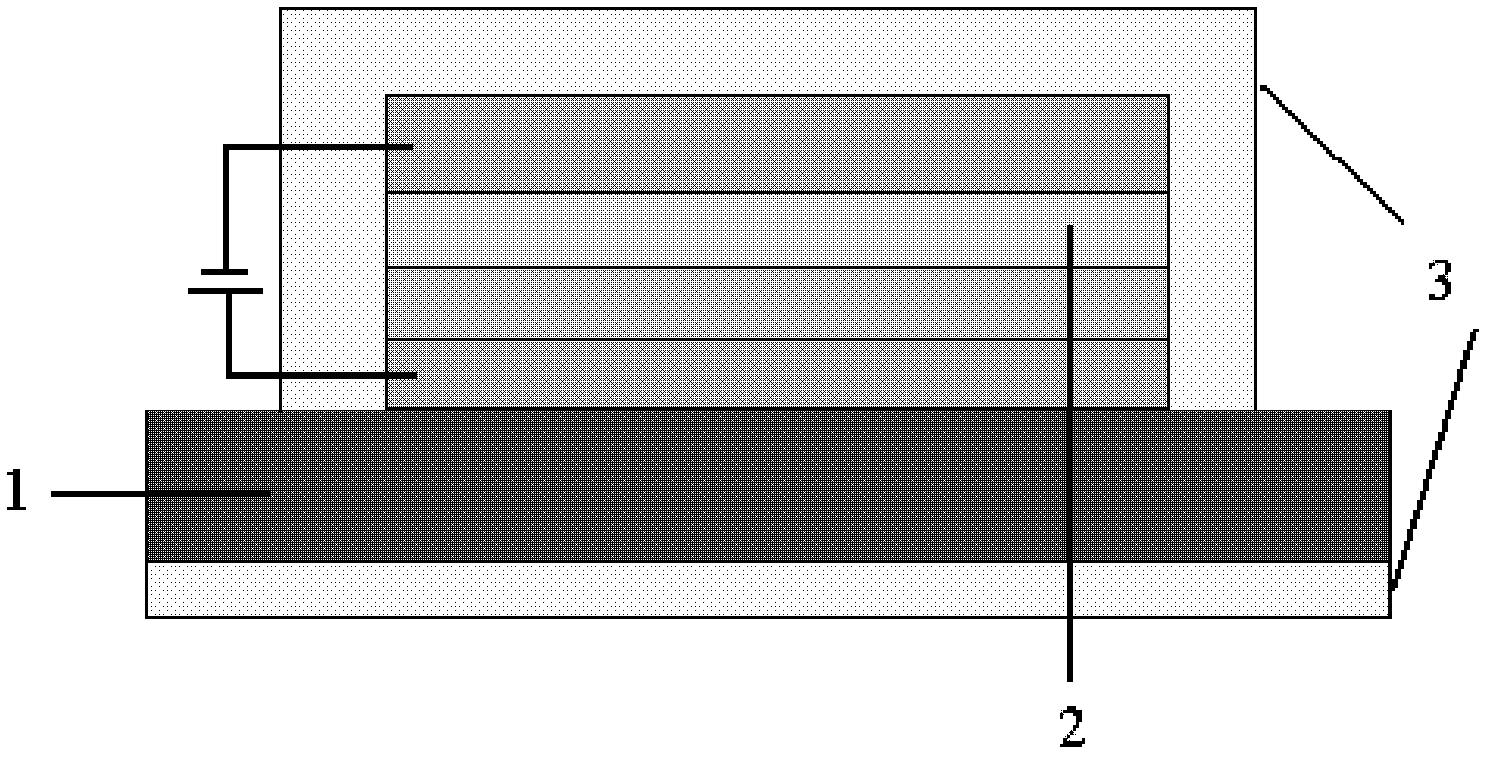

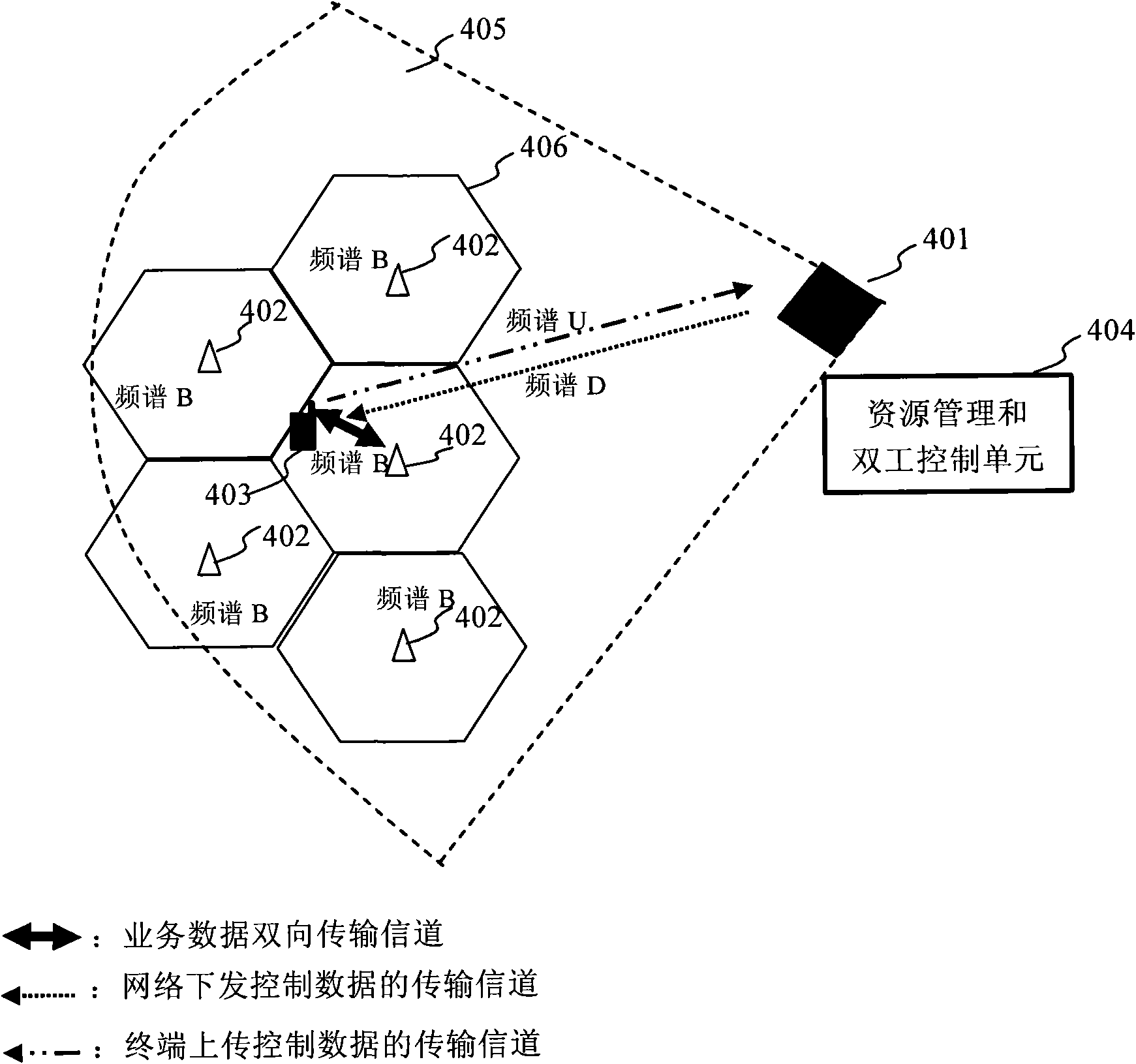

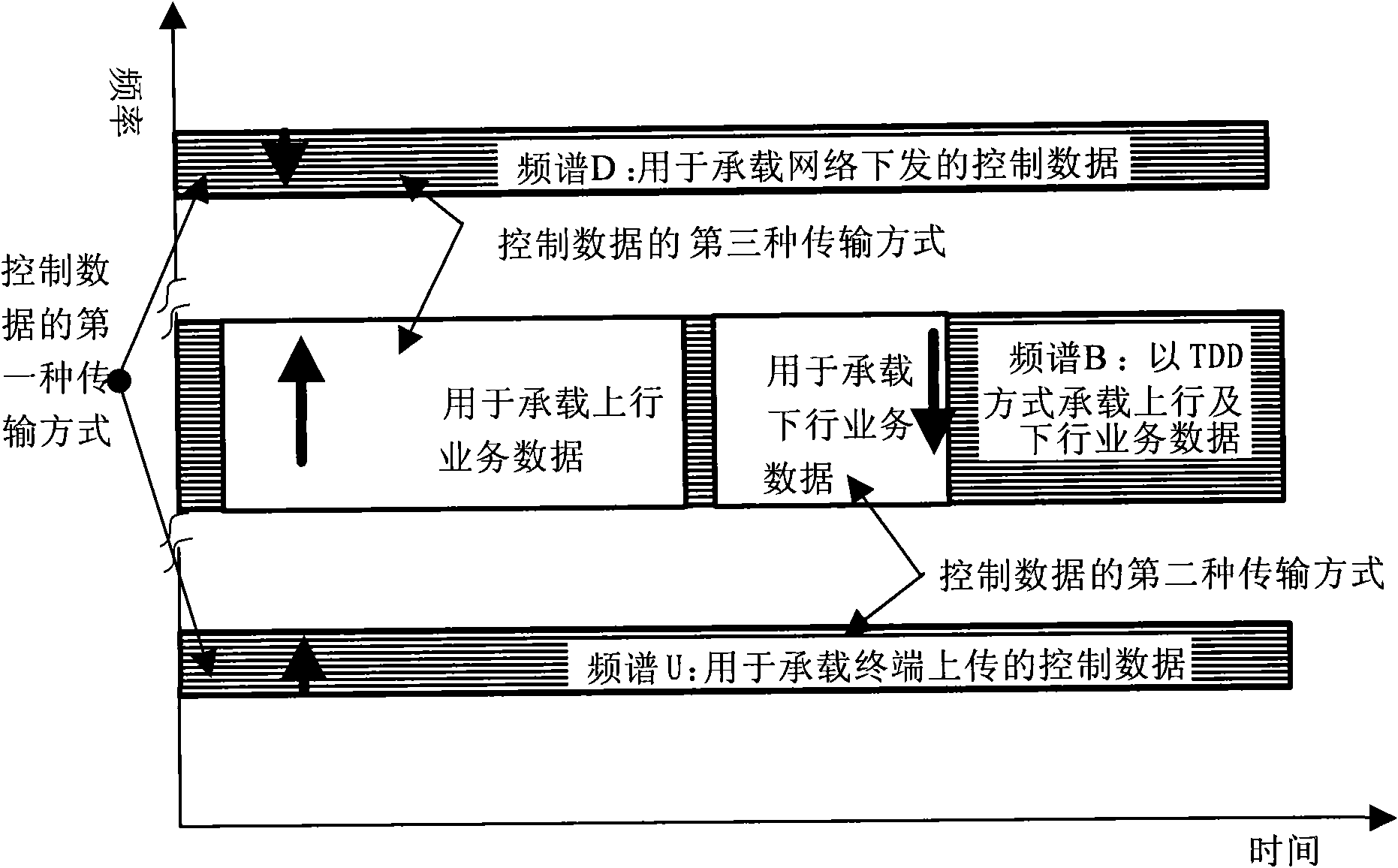

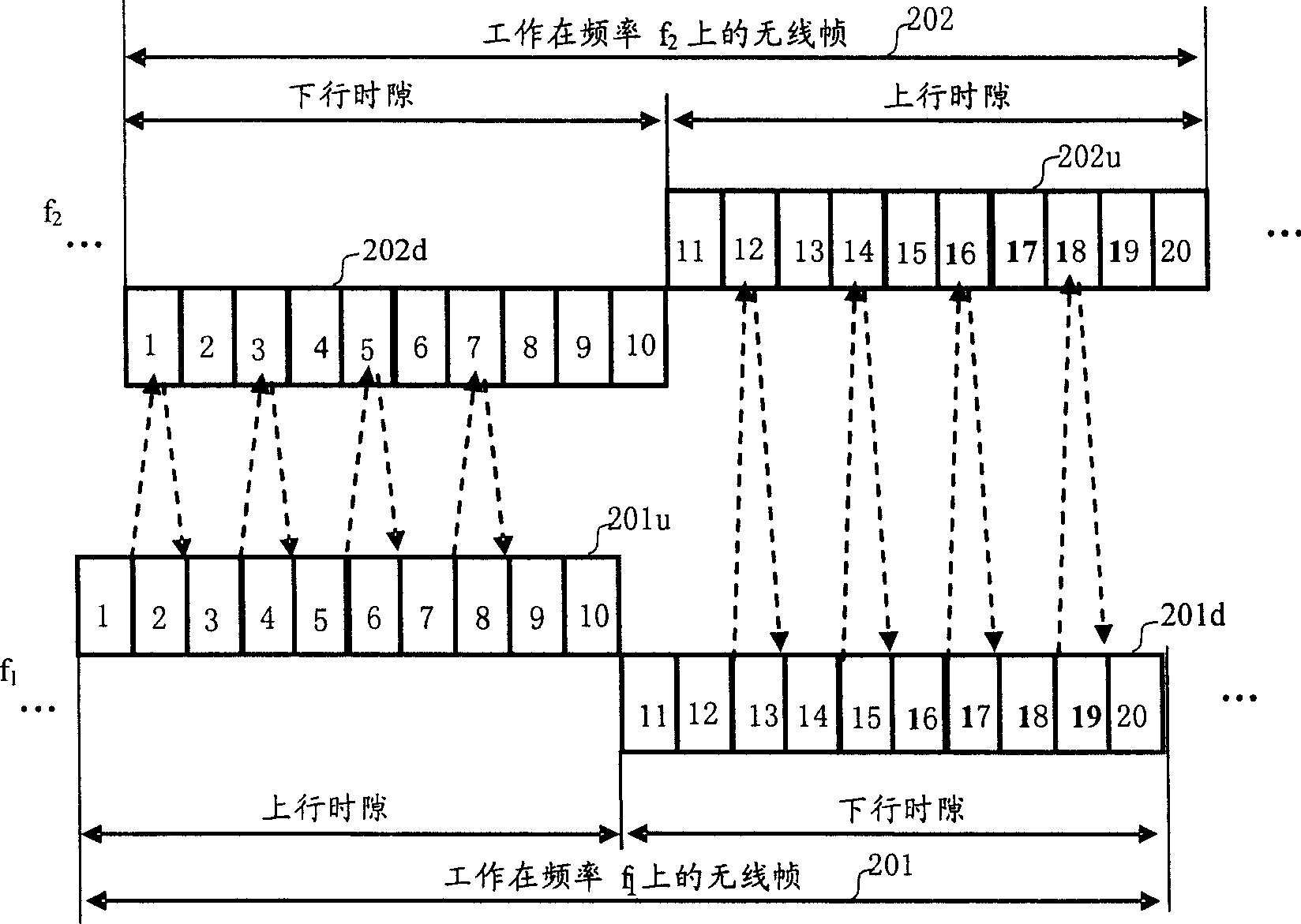

Hierarchical heterogeneous distributed base station and method thereof

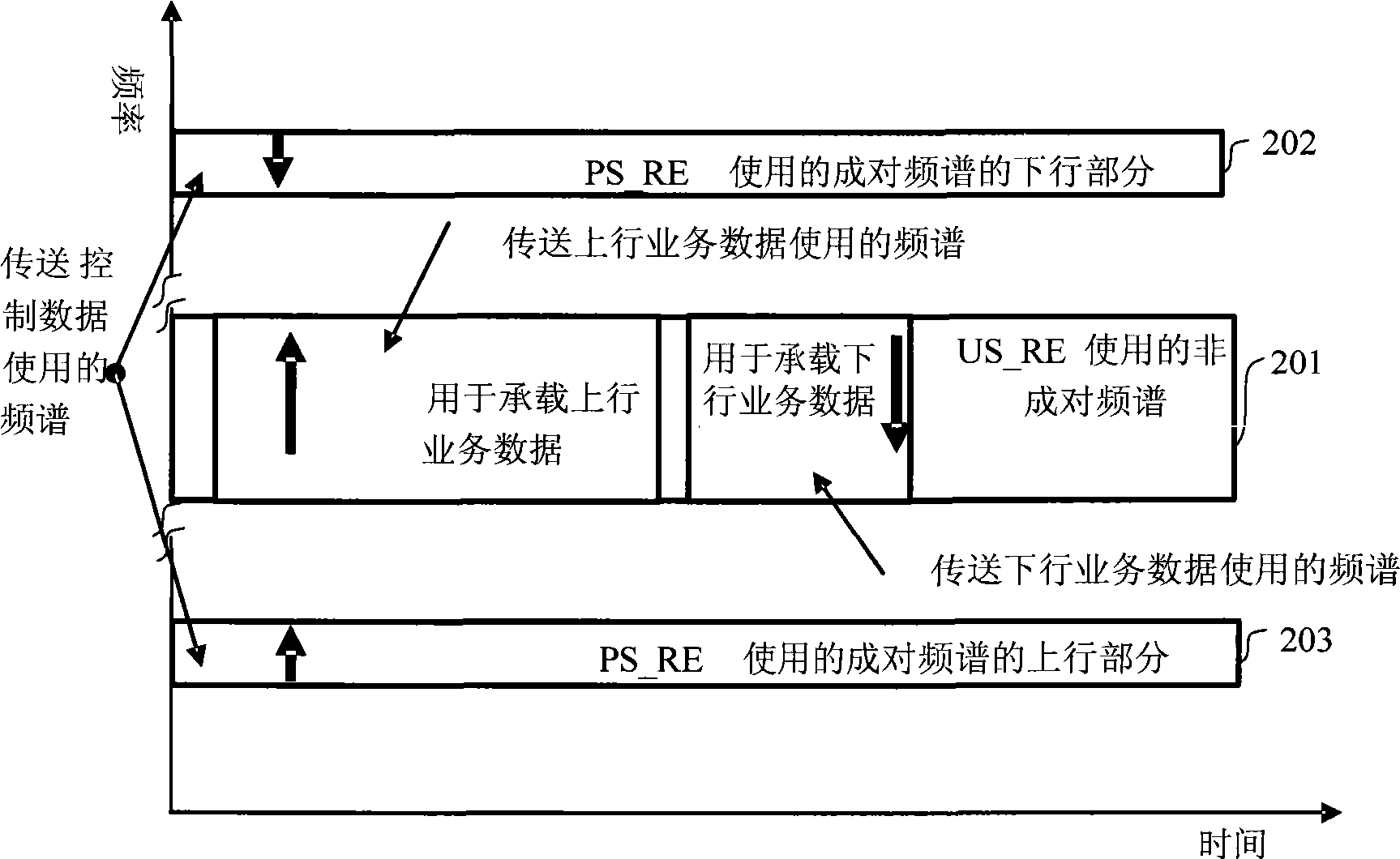

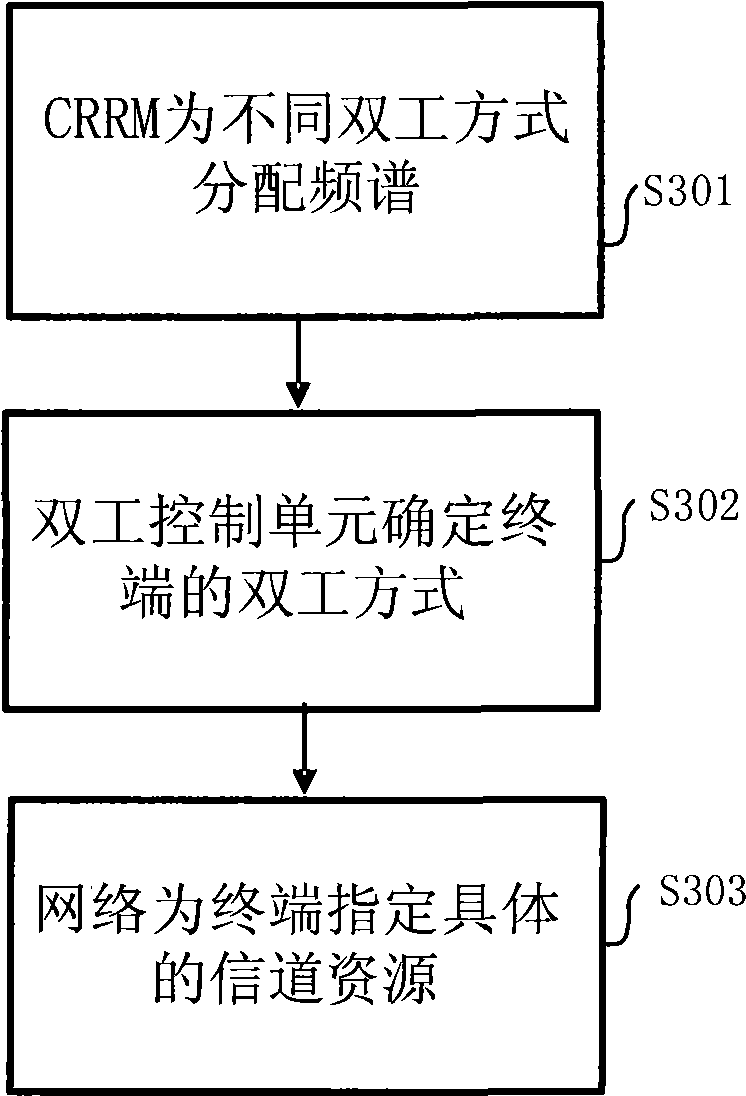

InactiveCN101547512APreserve channel reciprocityImprove dynamic performanceRadio transmission for post communicationWireless communicationTelecommunicationsFrequency spectrum

The invention provides a hierarchical heterogeneous distributed base station system, which comprises a wireless equipment control node, at least one FDD wireless equipment node using paired frequency spectrum and at least one TDD wireless equipment node using unpaired frequency spectrum; the wireless equipment control node configures an uplink / downlink service channel for a terminal which has communication with a hierarchical heterogeneous distributed base station in the TDD wireless equipment node and configures a control channel matched with the uplink / downlink service channel in the FDD wireless equipment node, thereby realizing hybrid duplexing between the hierarchical heterogeneous distributed base station and the terminal. The invention also provides a method for allocating the frequency spectrum resource, allocates the frequency spectrum for a plurality of duplexing modes and determines the duplexing mode of the terminal to allocate the channel resource for the terminal.

Owner:ZTE CORP

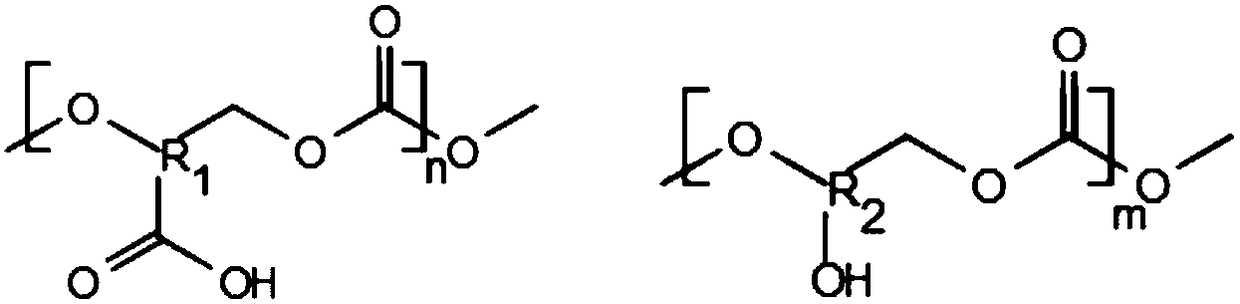

A preparation method of an all-solid-state polymer electrolyte and an all-solid-state polymer battery

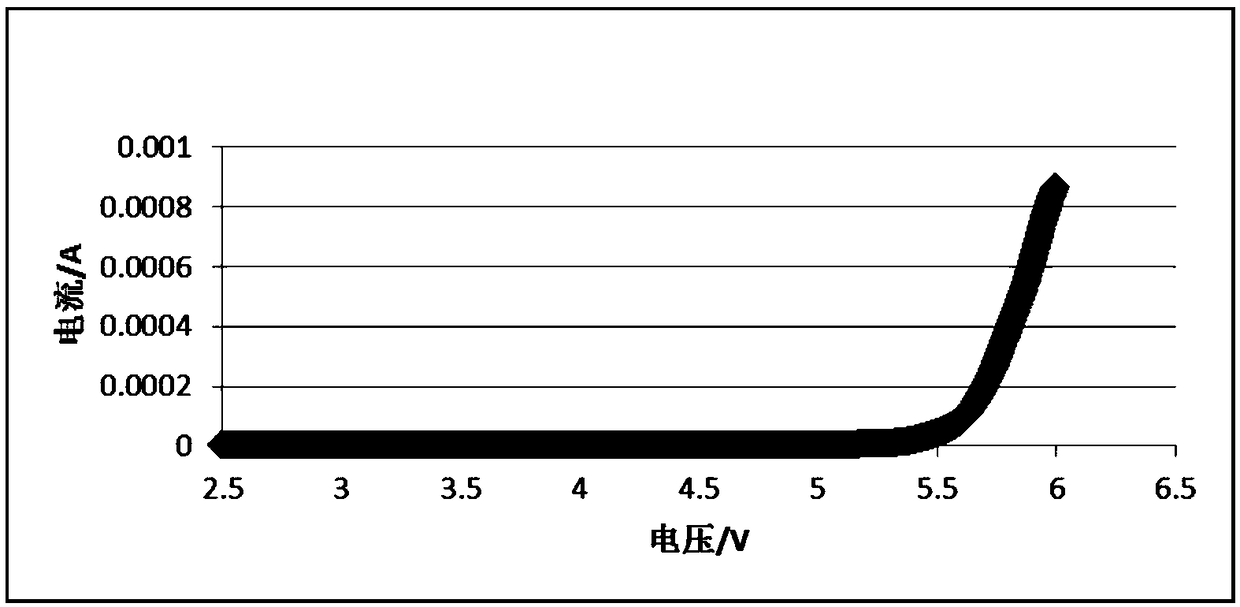

ActiveCN109004280AGood linear polymer with good interfacial contactImproved interface contactSolid electrolytesFinal product manufacturePolymer sciencePolyethylene glycol

The invention relates to a preparation method of an all-solid-state polymer electrolyte and an all-solid-state polymer battery. The preparation steps of the electrolyte are as follows: polymerizing apolycarbonate monomer with a carboxyl or hydroxyl polycarbonate monomer to obtain a polymer A; Adding polyether monomer, polyethylene glycol propylene monomer and functional polymer into solvent, adding lithium salt, initiator, selectively adding auxiliary agent and functional filler, and carrying out initiation reaction to obtain polymer B; Adding polymer A and polymer B into solvent and selectively adding carboxyl crosslinking agent to uniformly mix to obtain polymer mixing system; The hydroxyl crosslinking agent is added into the polymer mixing system and uniformly mixed, the obtained mixedliquid is uniformly coated on a mold, and the crosslinking reaction is carried out under an inert gas atmosphere in a vacuum drying box; At that end of the reaction, the polymer electrolyte membraneis vacuum dry in an inert gas atmosphere to obtain an all-solid polymer electrolyte membrane. The solid polymer electrolyte of the invention has good compatibility and mechanical strength and high room temperature ionic conductivity.

Owner:ZHUHAI COSMX BATTERY CO LTD

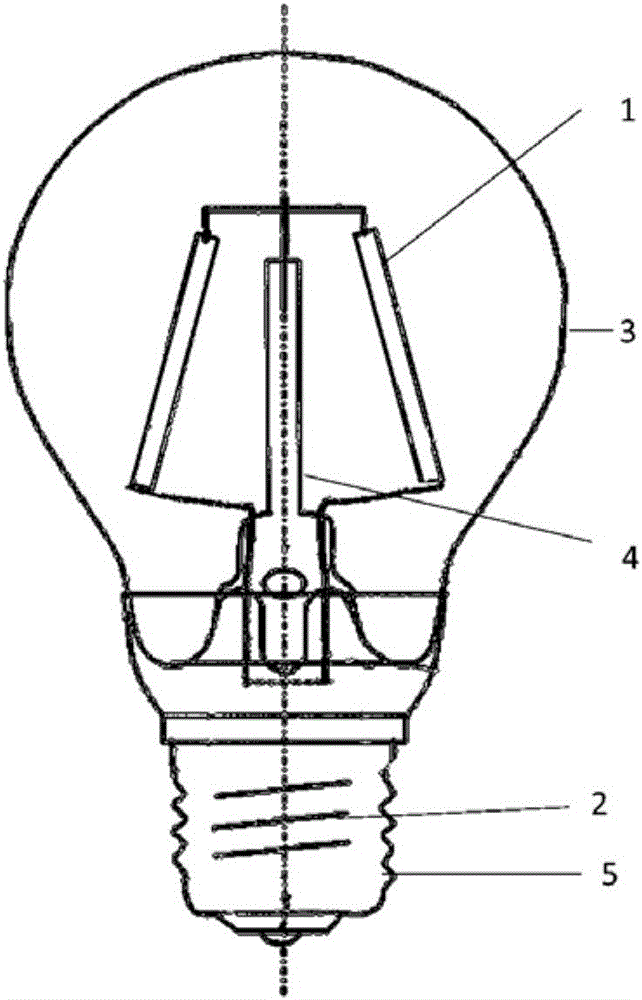

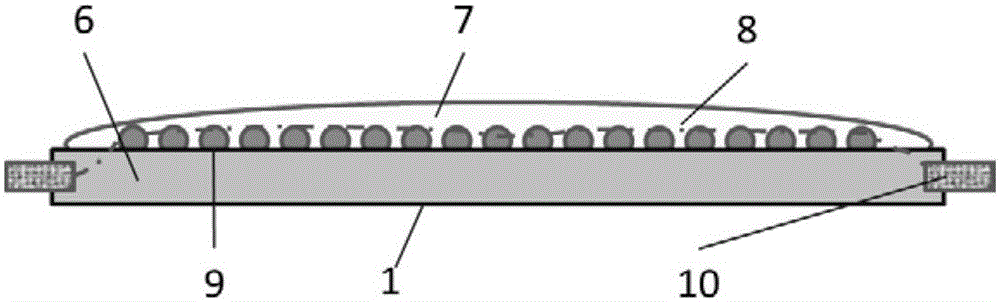

LED-chip shining-light-bar base plate material and LED bulb lamp

InactiveCN106190124AExtended service lifeImprove use reliabilityElectric circuit arrangementsChemical industryColor rendering indexOptical transmittance

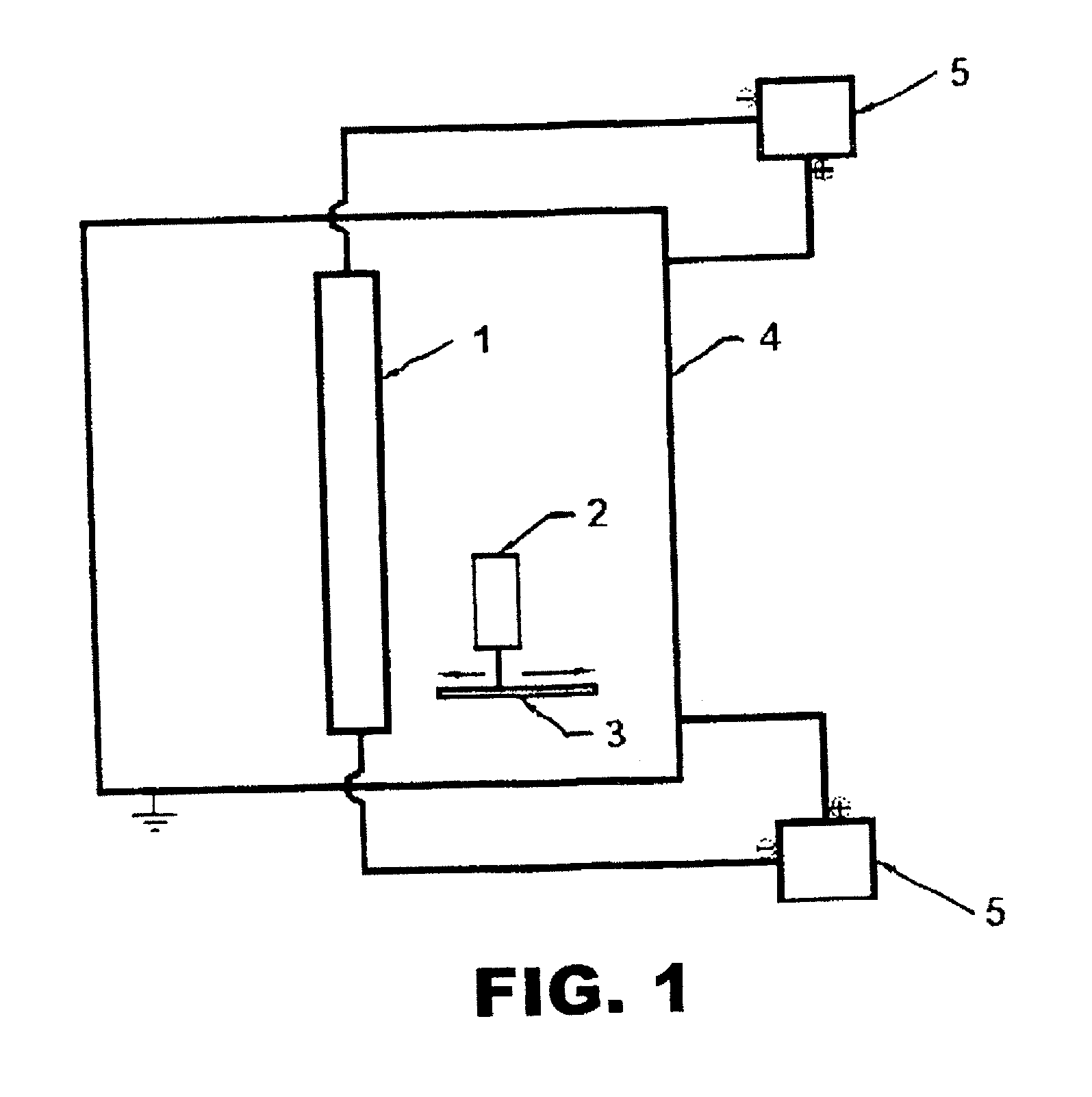

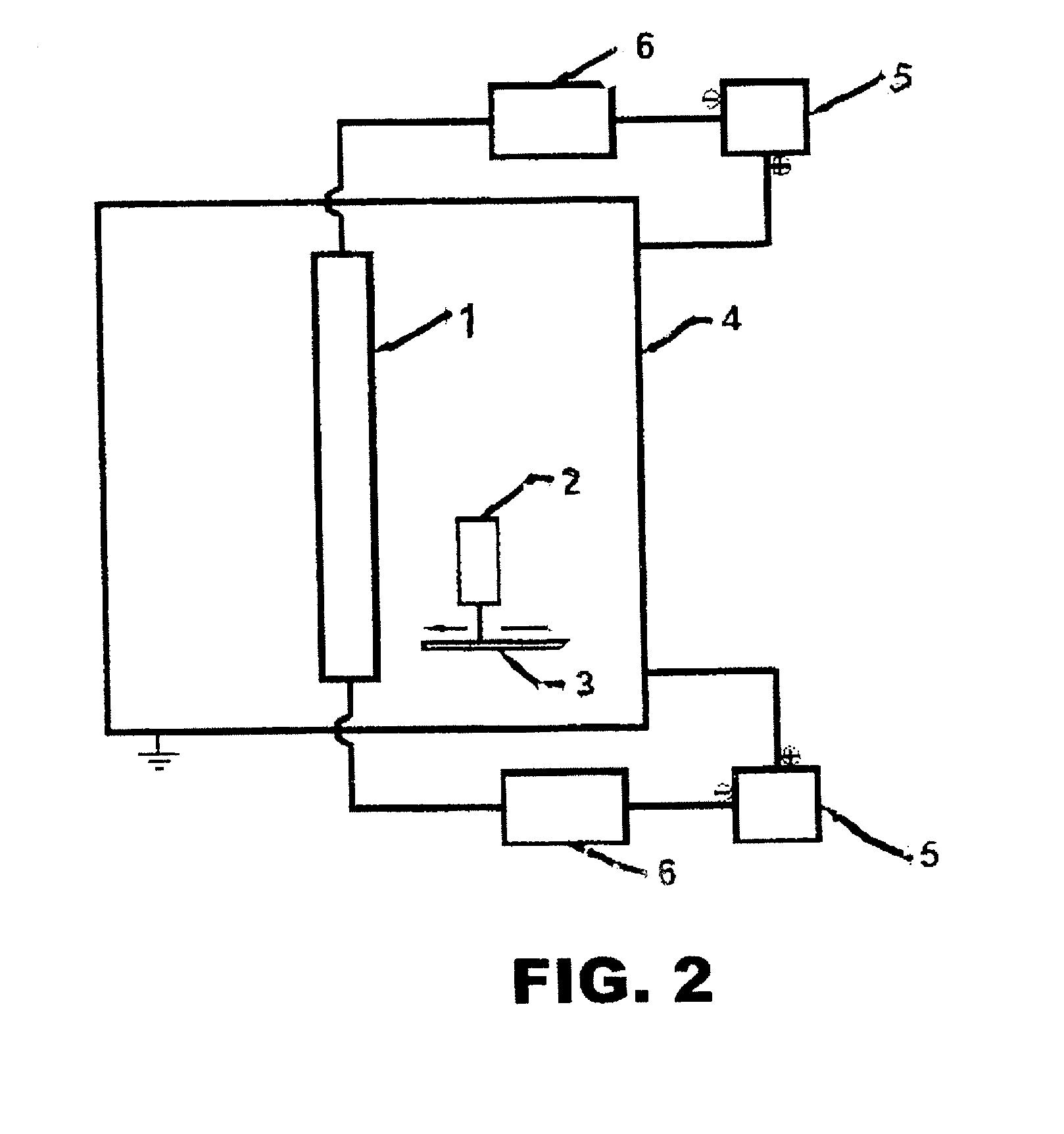

The invention relates to an LED-chip shining-light-bar base plate material and an LED bulb lamp. The LED-chip shining-light-bar base plate material and the LED bulb lamp are characterized in that the LED bulb lamp is composed of shining strips (1), a driving power source (2), a glass bulb shell (3), a glass support core column (4) and an electric connector (5); the glass bulb shell (3) and the glass support core column (4) are subjected to vacuum sealing to a cavity to be filled with high thermal conduction gas, the glass support core column (4) and the shining strips (1) fixed on the glass support core column (4) are contained in the sealed cavity; the shining strips (1) are sequentially electrically connected with the driving power source (2) and the electric connector (5); the LED-chip shining strips (1) are composed of YAG, wherein Ce raw material powder and nitride red fluorescence powder are fired to achieve the effect that one face of the base plate material (6) comprises LED blue light chips (9), and the surfaces of the blue light chips (9) are coated with a fluorescent powder layer (7). According to the LED-chip shining-light-bar base plate material and the LED bulb lamp, low-cost preparing of the high-quality transparent fluorescence polycrystal base plate material is achieved with the novel environment-friendly aqueous tape-casting technology. The fluorescence polycrystal base plate material which is high in lighting efficiency, color rendering index and optical transmittance and the bulb lamp which is good in color-temperature consistency heat dissipation, high in reliability and long in service life are obtained.

Owner:张伯文

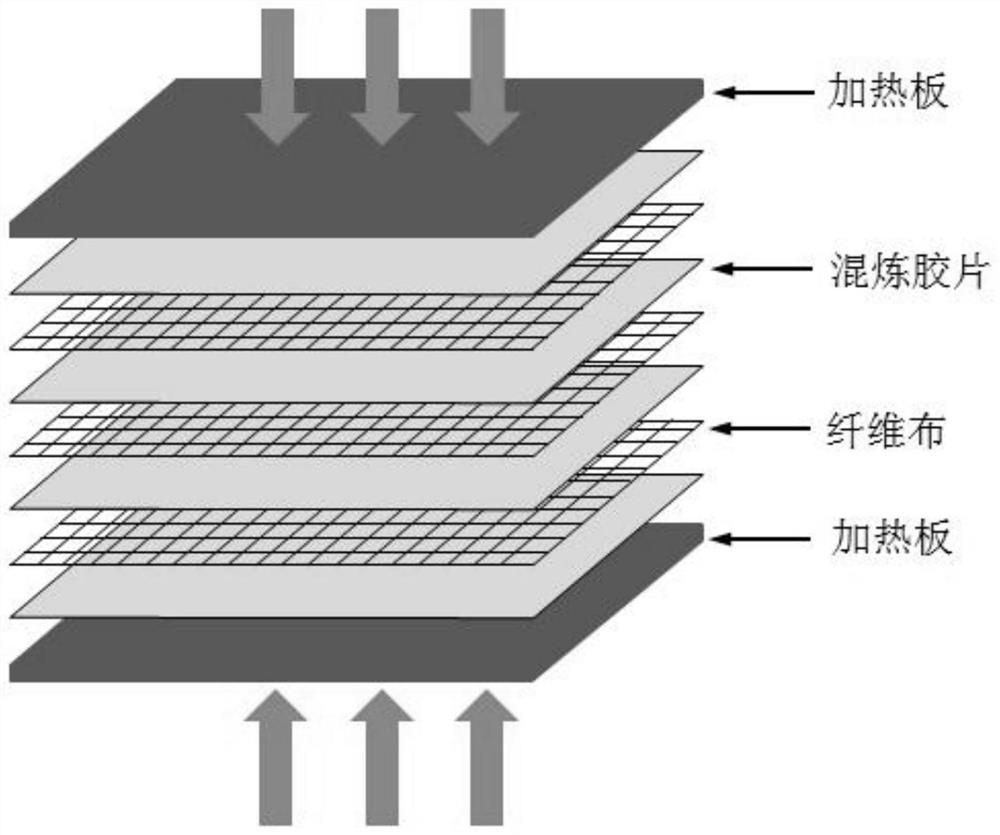

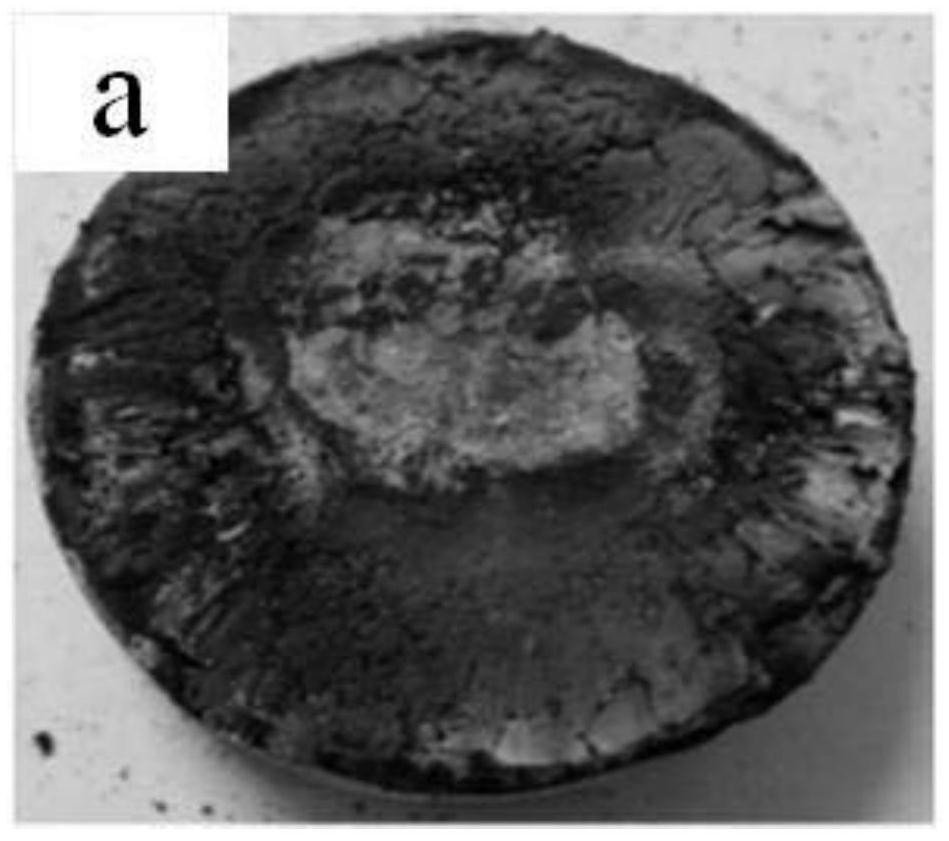

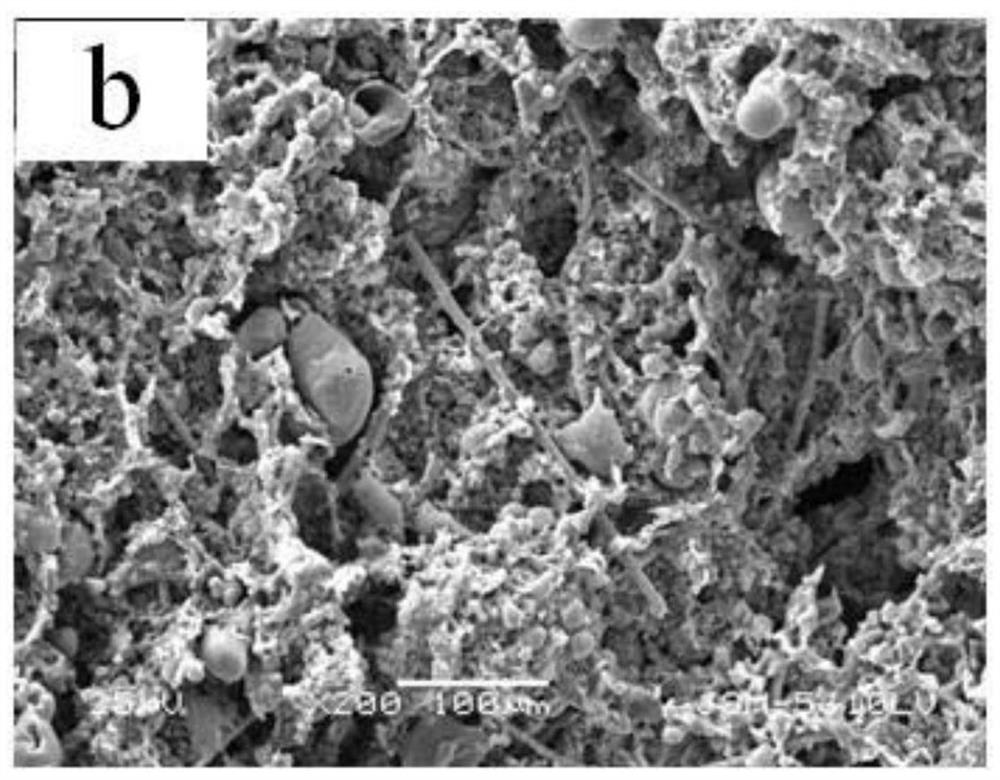

Flexible ceramizable silicone rubber thermal insulation composite material and preparation method thereof

PendingCN111761895AHigh mechanical strengthImprove anti-ablation performanceCosmonautic thermal protectionLaminationFiberVulcanization

The invention relates to a flexible ceramizable silicone rubber thermal insulation composite material and a preparation method thereof. The composite material is a silicone rubber / fiber cloth integralstructure, the silicone rubber is a support structure, and the fiber cloth penetrates through the silicone rubber; the composite material is obtained by stacking and vulcanizing mixed rubber sheets and fiber cloth at intervals, the mixed rubber sheets are obtained by mixing the silicone rubber, and the mixed rubber sheets are prepared from, by mass, 100 parts of the silicone rubber, 20-45 parts of fumed silica, 30-160 parts of ceramic powder, 0-40 parts of a fluxing agent, 6-20 parts of short fibers, 1-15 parts of a structure control agent and 1-4 parts of a vulcanizing agent. The ceramizablesilicone rubber composite material provided by the invention is good in flexibility, high in mechanical property, good in ablation resistance and resistant to high-speed airflow scouring, and can meet the requirements of the fields of aerospace and special fireproof engineering on fireproof, thermal-insulating and ablation-resistant thermal protection performance.

Owner:WUHAN UNIV OF TECH

Washer nozzle with integrated adjustable aim fluidic insert (chip) and method

InactiveUS7036749B1Additional costRetain flexibilityCircuit elementsSpray nozzlesFluidicsEngineering

The invention comprises a curved fluidic device and a housing piece with a curved slot to accommodate the curved fluidic device. The aim angle can be varied greatly by changing the depth of insertion of the fluidic device into the curved slot. By adjusting the curvature of the fluidic device and slot, the amount of variation possible and sensitivity to insertion depth can be controlled. With more curvature, the aim angle can be adjusted more but is more sensitive to insertion depth tolerance. With less curvature, the insertion depth is more robust but the aim adjustment range is smaller.

Owner:BOWLES FLUIDICS

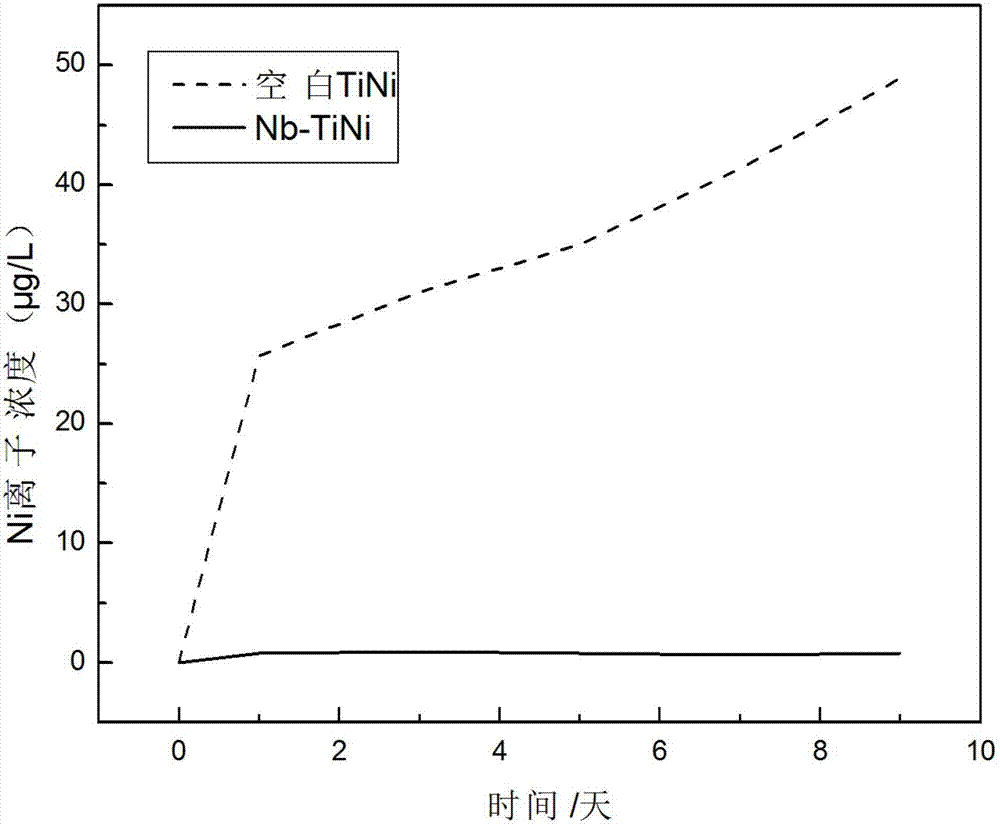

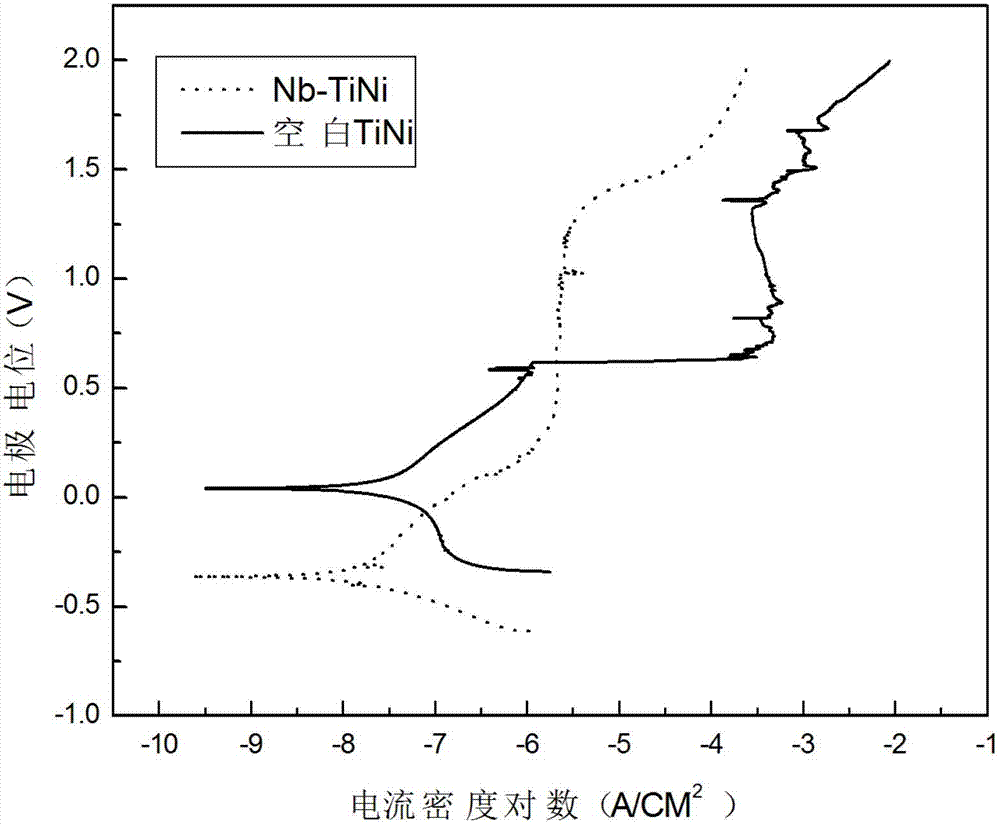

Method for conducting surface modification on medical titanium nickel (TiNi) shape memory alloys through niobium (Nb) ion injection deposition

ActiveCN102828157AGood biocompatibilityLow toxicityVacuum evaporation coatingSputtering coatingNiobiumBiocompatibility Testing

The invention discloses a method for conducting surface modification on medical titanium nickel (TiNi) shape memory alloys through niobium (Nb) ion injection deposition. The method compounds two methods of ion injection and ion beam strengthening deposition, wherein a transition layer formed by an ion injection method is mainly composed of TiO2 and Nb2O5, and an ion beam strengthening deposition method is that a pure Nb metal film layer is formed on the basis of the transition layer. After the surface modification is carried out on the alloys through the method of selecting appropriate parameters, the obtained shape memory alloys can completely prevent Ni ions from dissolving out from a matrix, and simultaneously the method has good shape memory effects which are not second to the matrix and stain resistance and biocompatibility superior to the matrix.

Owner:BEIHANG UNIV

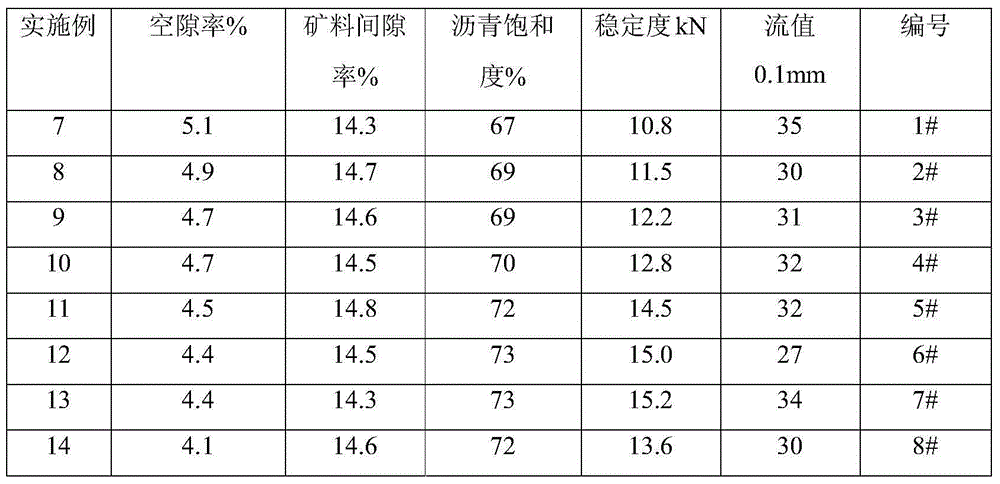

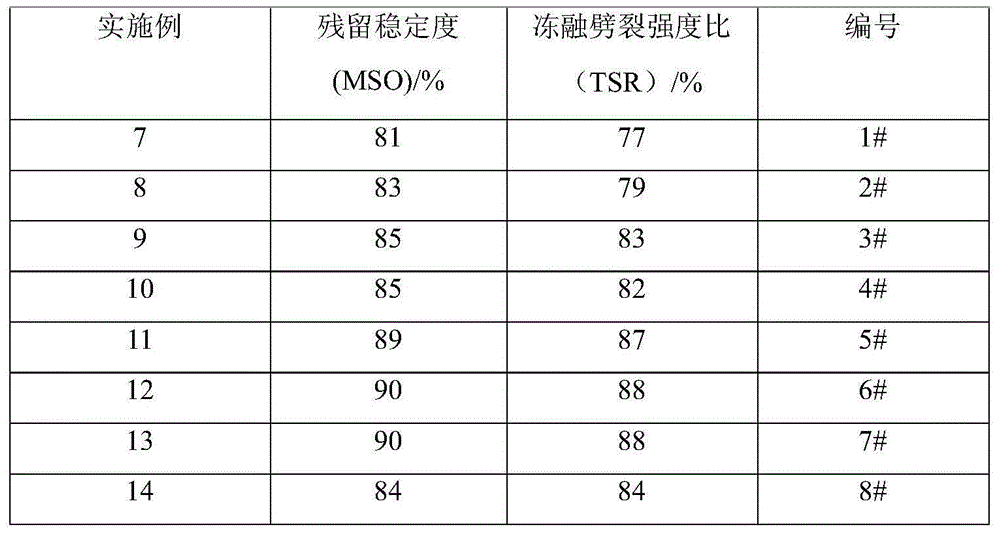

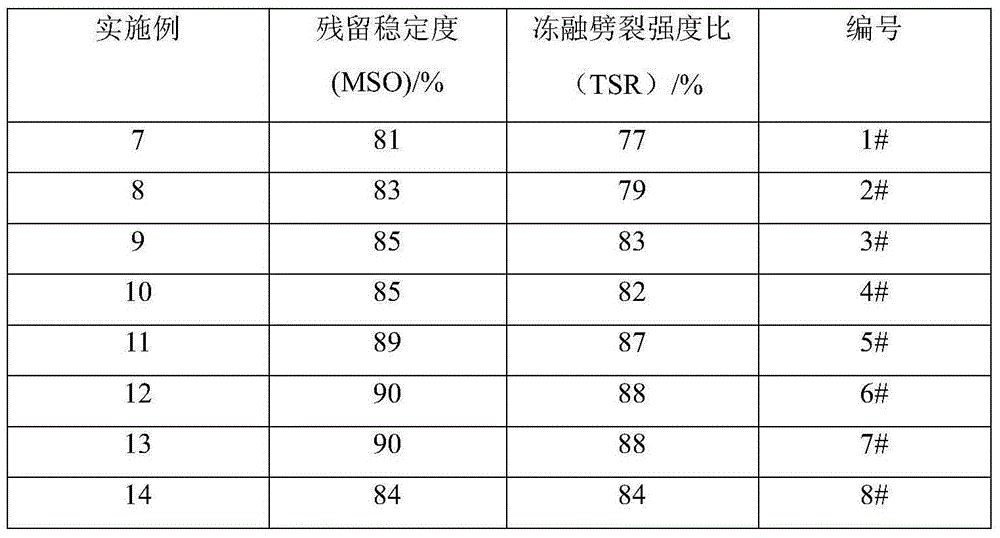

Bituminous mixture using DVS (direct vat set) high-adhesion modifier and preparation method thereof

ActiveCN104693821AControl "Secondary Pollution"Low costBuilding insulationsBulk chemical productionCrack resistancePolymer science

The invention relates to a bituminous mixture using a DVS (direct vat set) high-adhesion modifier and a preparation method thereof. The bituminous mixture is prepared from aggregates, a DVS high-adhesion bituminous mixture modifier and matrix asphalt by mixing, wherein the modifier is prepared from high-desulfurization-degree reclaimed rubber, modified high-temperature coal tar pitch and a skeleton proppant by stirring and extruding. Waste rubber is deeply activated under the high temperature and high shearing action of a twin screw extruder, so that the high-desulfurization-degree reclaimed rubber is obtained; then, the mixture of the modified high-temperature coal tar pitch modified by rubber pyrolysis oil, the high-desulfurization-degree reclaimed rubber and the skeleton proppant is fully mixed by using a screw, and then extruded and granulated so as to obtain the DVS high-adhesion bituminous mixture modifier; and finally, the modifier, the aggregates and the matrix asphalt are mixed so as to obtain a DVS high-adhesion bituminous mixture. The bituminous mixture disclosed by the invention has excellent water damage resistance, good high-temperature rutting resistance and low-temperature crack resistance.

Owner:TIANJIN HI TECH ENVIRONMENT DEV CO LTD

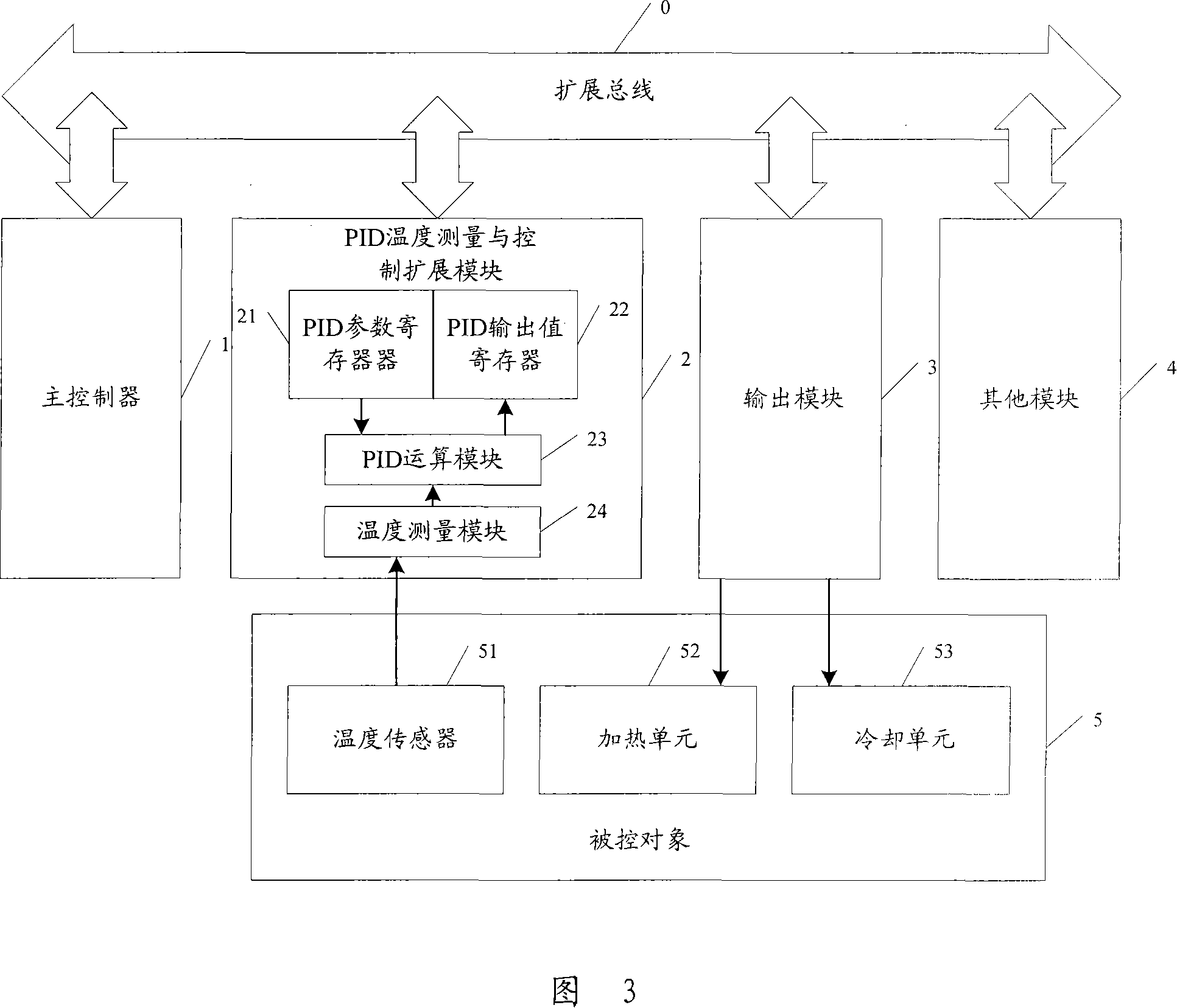

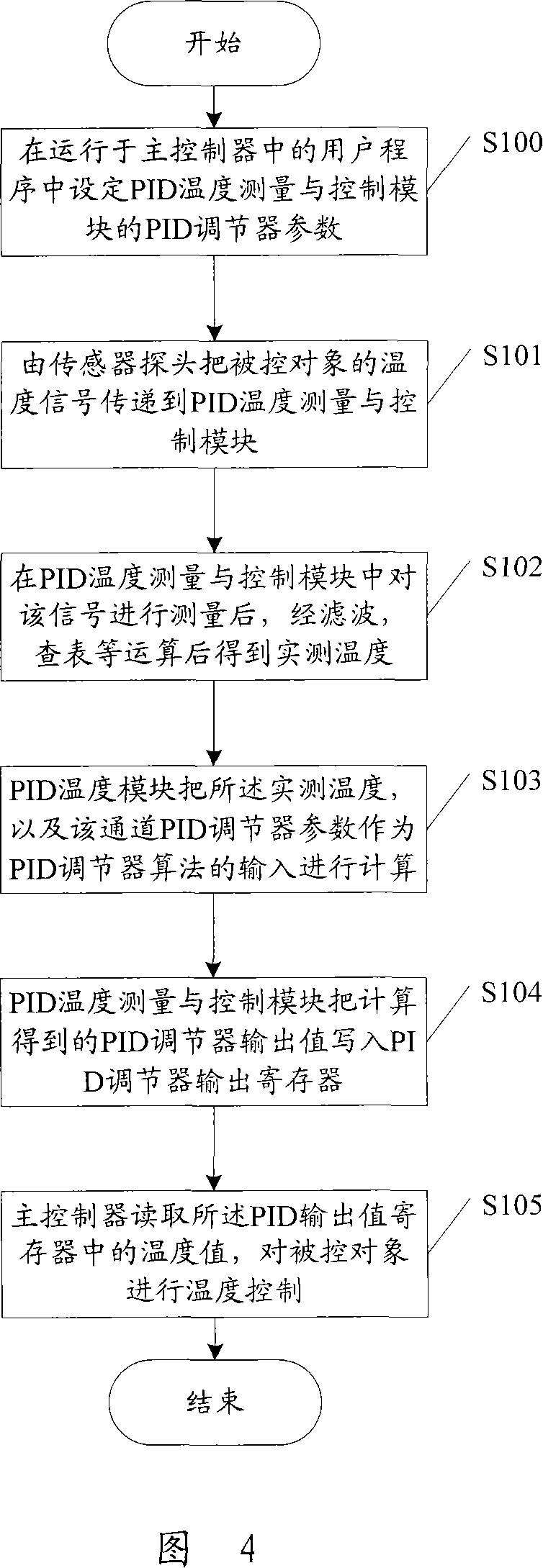

PLC system and its temperature measurement and control expansion module, its implement method

InactiveCN101105412AImprove real-time performanceImprove abilitiesThermometer detailsSystem stabilityMaster controller

The invention discloses a temperature measurement and control expansion module for PLC, which comprises an expansion bus interface connected to a master controller, wherein at least a register of PID adjuster parameters is disposed in the expansion bus interface and used for making the master controller of PLC to randomly set PID adjuster parameters through the expansion bus interface; at least a register of PID adjuster output values is disposed in the expansion bus interface and used for storing temperature values obtained by measurement and PID temperature output values obtained by calculation of the PID adjuster and providing these values to the master controller of PLC for implementation. The invention also discloses a PLC system and a method for measuring and controlling temperature using the temperature measurement and control expansion module for PLC. The invention can simplify the control program of PLC user, reduce the complexity of the control program application, and improve system stability.

Owner:深圳市合信自动化技术有限公司

Flexible conductive single wire

ActiveUS20130046368A1Improve radiopacityShort processing timeConductive layers on insulating-supportsElectric discharge tubesCell adhesionIn vivo

Thin conductive metal coatings suitable for flexible nonmetal fine wires and leads are described. Polymer clad silica fiber cores are produced by plasma coating with single or dual layers of metals such as silver, gold or titanium to provide micro thin leads such as those used for pacemakers and fracture resistant aircraft wires that are both conductive and resistant to flexing breakage. The metal surfaces can be used to transmit analog signals while the nonmetal cores can be designed to transmit digital signals. Select deposition conditions can produce nanorough metal coating surfaces which promote cell adhesion so that tissue scarring in vivo is greatly reduced.

Owner:SURFATEK

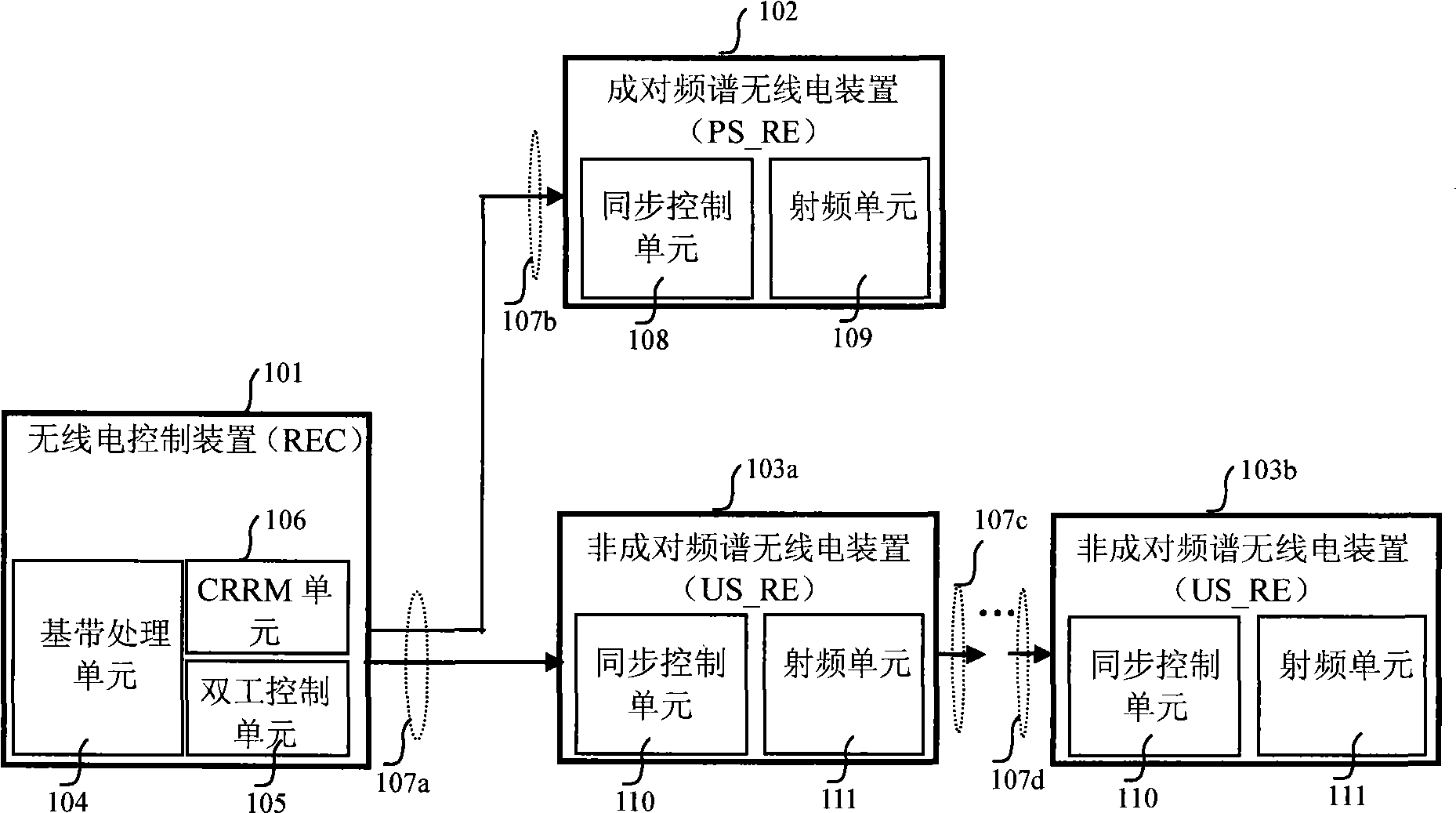

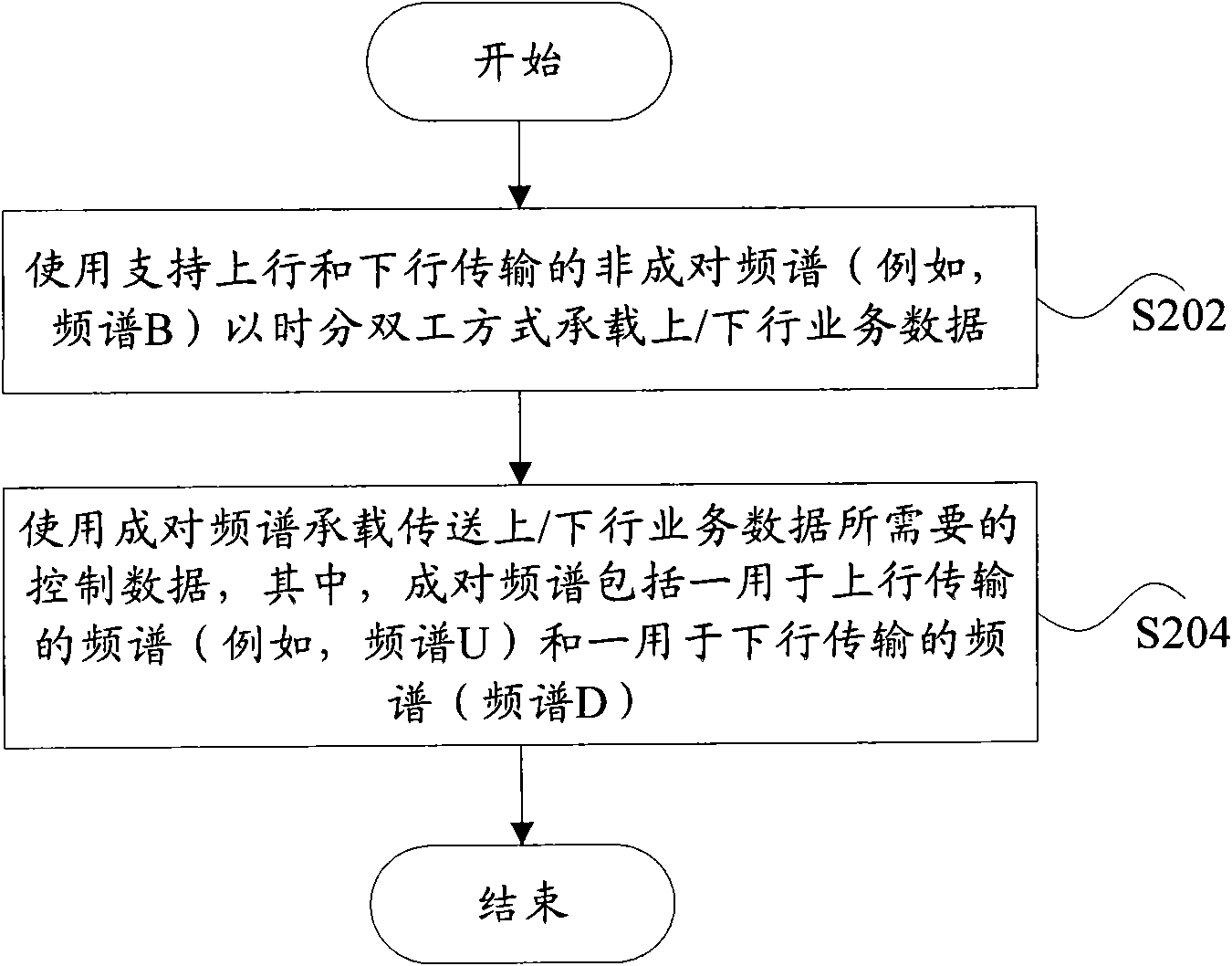

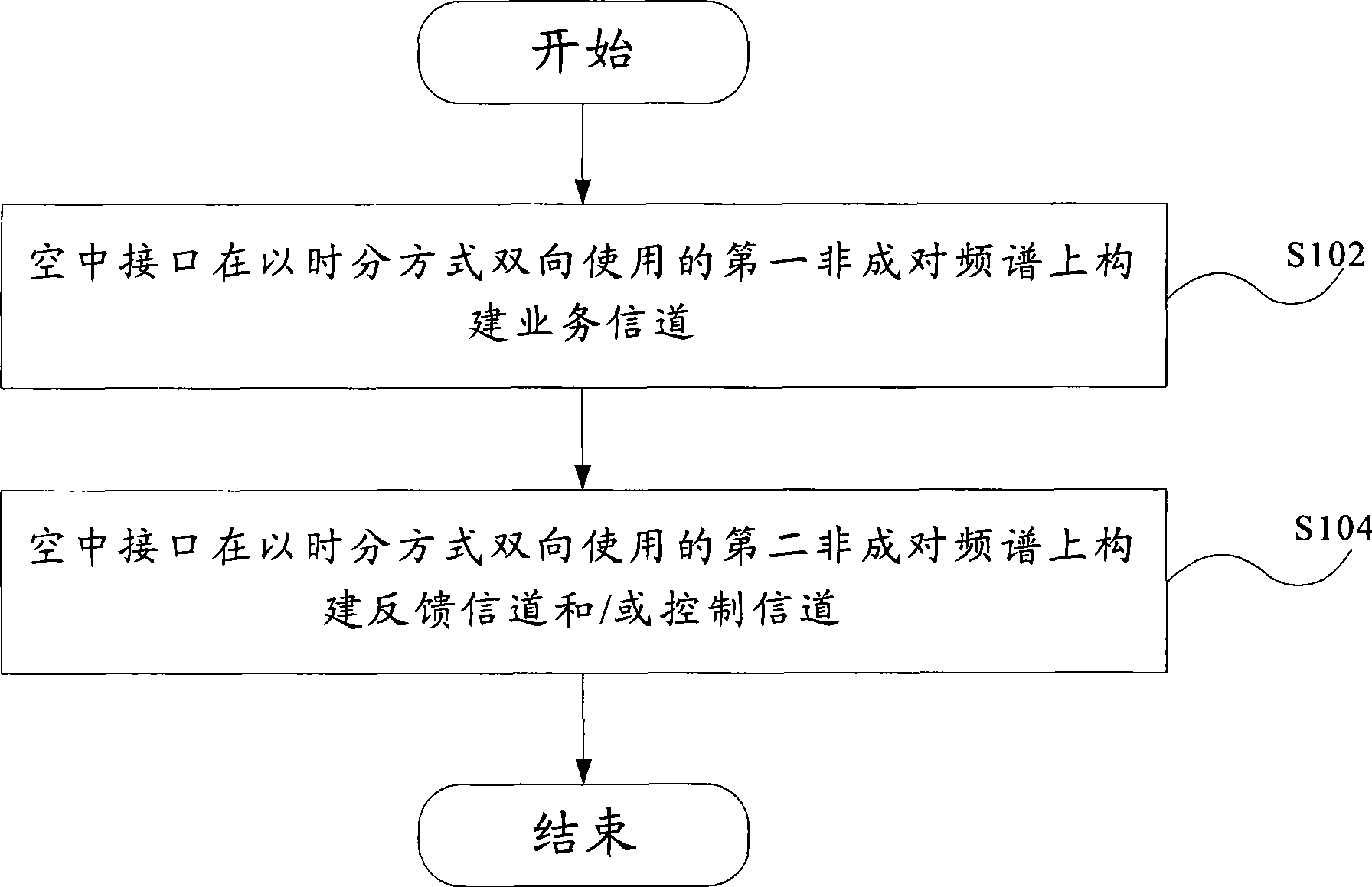

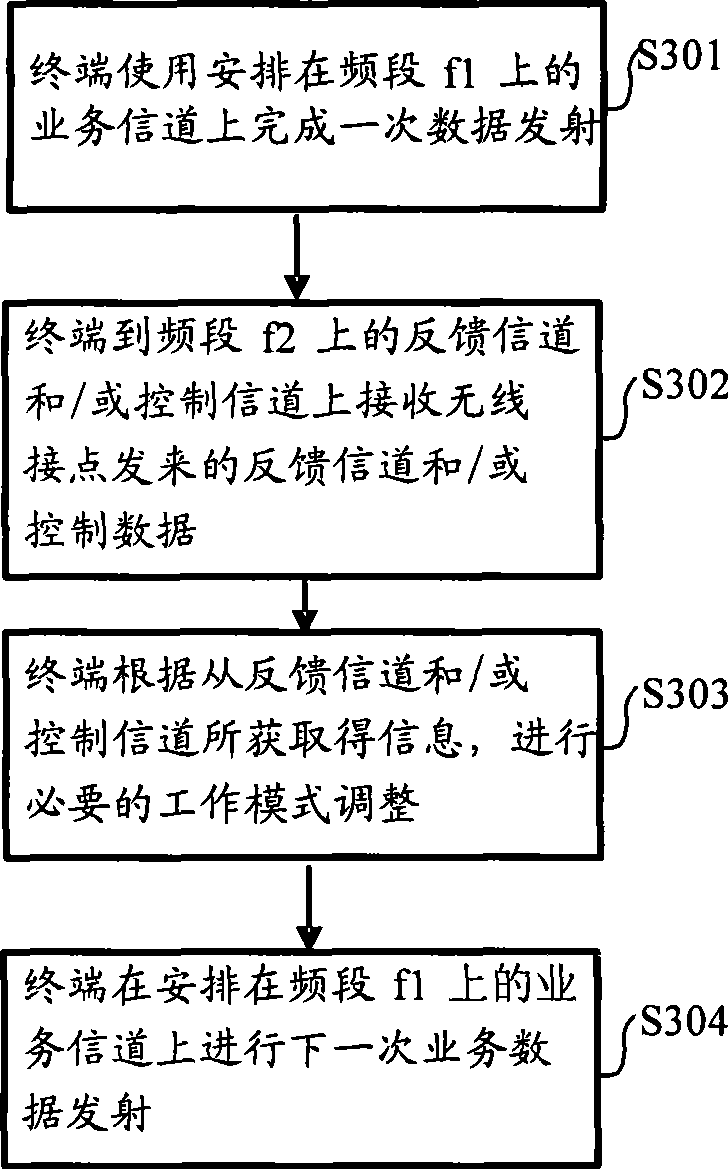

Mixed duplex realization method based on separated service and control as well as data transmission method

ActiveCN101527886AAchieve synergyPreserve channel reciprocityRadio transmission for post communicationMessaging/mailboxes/announcementsFrequency spectrumUplink transmission

The invention discloses a mixed duplex realization method and a mixed duplex realization system based on separated service and control. The method comprises the following steps: bearing uplink / downlink service data by using unpaired spectrums for supporting uplink and downlink transmission in a time division duplex mode; and bearing control data required by transmitting the uplink and downlink service data by using paired spectrums, wherein the paired spectrums comprise a spectrum used for uplink transmission and a spectrum used for downlink transmission. The invention also discloses a data transmission method. By the invention, the channel reciprocity of TDD of the service data and the flexibility of uplink / downlink service are maintained, the low feedback time delay of FDD of the transmission of the control data is realized, and the TDD system and the FDD system realize further synergism.

Owner:ZTE CORP

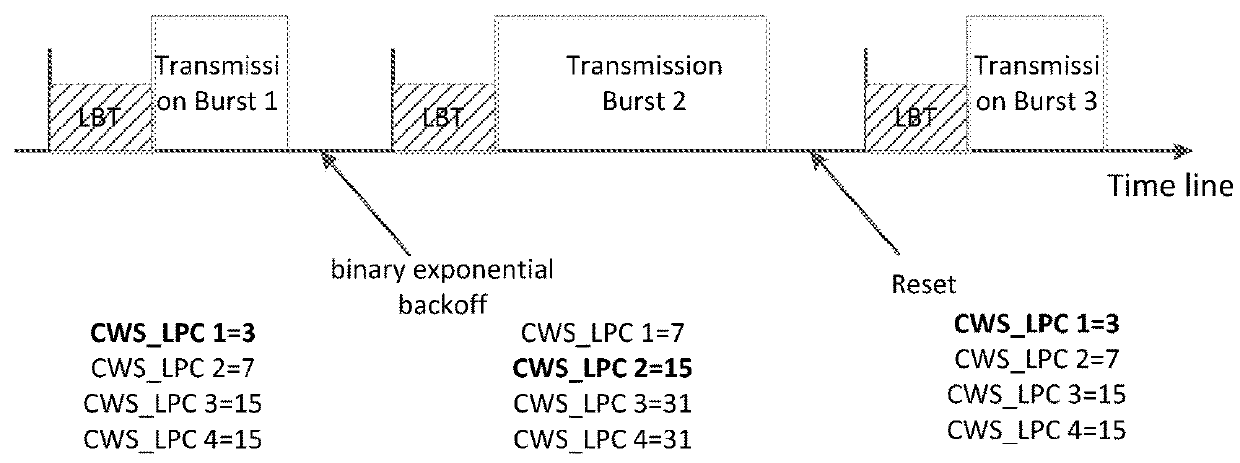

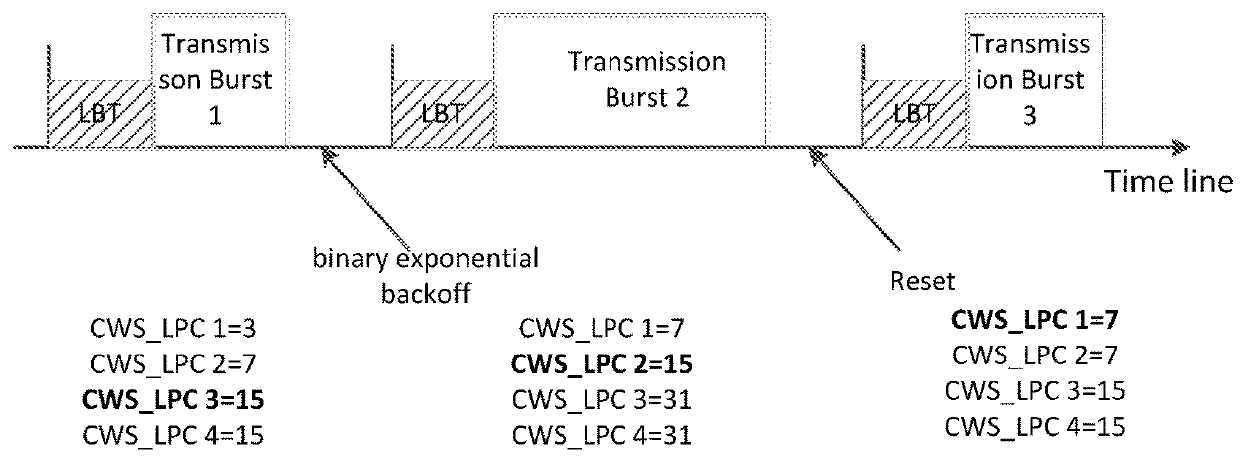

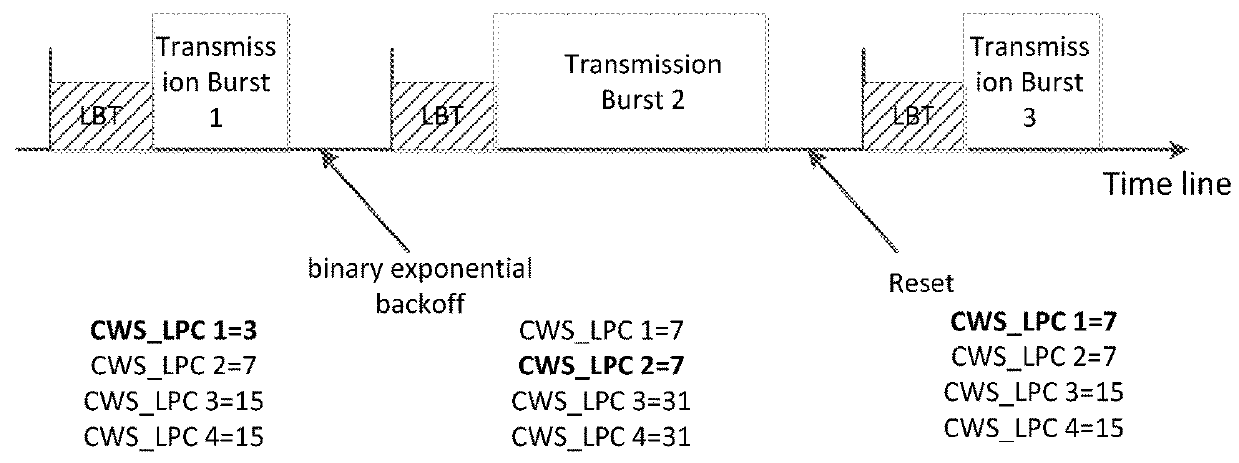

Method of supporting multiple QOS in a listen-before-talk operation

InactiveUS20180279370A1Enhanced distributed channel access parameterRetain flexibilityNetwork traffic/resource managementNetwork planningDistributed computingListen before talk

Owner:ALCATEL LUCENT SAS

Vibration-isolating and noise-reducing rubber support for buildings

ActiveCN103437445AWill not be damaged by tensionLight weightShock proofingEngineeringMechanical engineering

The invention discloses a vibration-isolating and noise-reducing rubber support for buildings, which comprises a base, a top seat plate and a cylindrical vibration isolator, the base is a block with a sunken mounting cavity, the vibration isolator is arranged in the mounting cavity, the top seat plate covers the top end of the mounting cavity of the base and presses the vibration isolator, the bottom of the mounting cavity is provided with at least one pair of oppositely arranged guide blocks, and the guide blocks are extended along the circumference of the bottom of the inner wall of the mounting cavity and located around the vibration isolator, and hold the lower part of the vibration isolator. Since the lower part of the vibration isolator is held by the guide blocks of the vibration-isolating and noise-reducing rubber support, the guide blocks can be arranged at different positions according to actual requirement to control the horizontal deformation direction and displacement of the vibration isolator, thus ensuring that the concrete members of an upper structure supported by the support cannot be pulled and pressed to be damage due to excessive deformation under the action of the additional stress of vibration.

Owner:ARCHITECTURAL DESIGN RES INST OF GUANGDONG PROVINCE

Method and system for inducting outer feedback in TDD aerial interface

ActiveCN101415275APreserve reciprocityRetain flexibilityTime-division multiplexWireless communicationAccess networkFrequency spectrum

The invention discloses a method for introducing outer zone feedback into a time division duplex air interface. The method comprises the following processes: an air interface structures a service channel on a first unpaired spectrum which is used in a time-division manner in two directions, and the air interface structures a feedback channel and / or a control channel on a second unpaired spectrum which is used in a time-division manner in two directions. In addition, a system which corresponds to the method is also provided. The air interface has the advantages of reserving the channel reciprocity of TDD, the flexibility of downlink and uplink services and the like; in addition, the air interface has various advantages brought by the low feedback latency of half-duplex FDD. In particular, when the air interface is applied to the double layer and double frequency wireless access network, the capability of supporting a high-speed mobile terminal of a micro-cell wireless contact can be improved.

Owner:ZTE CORP

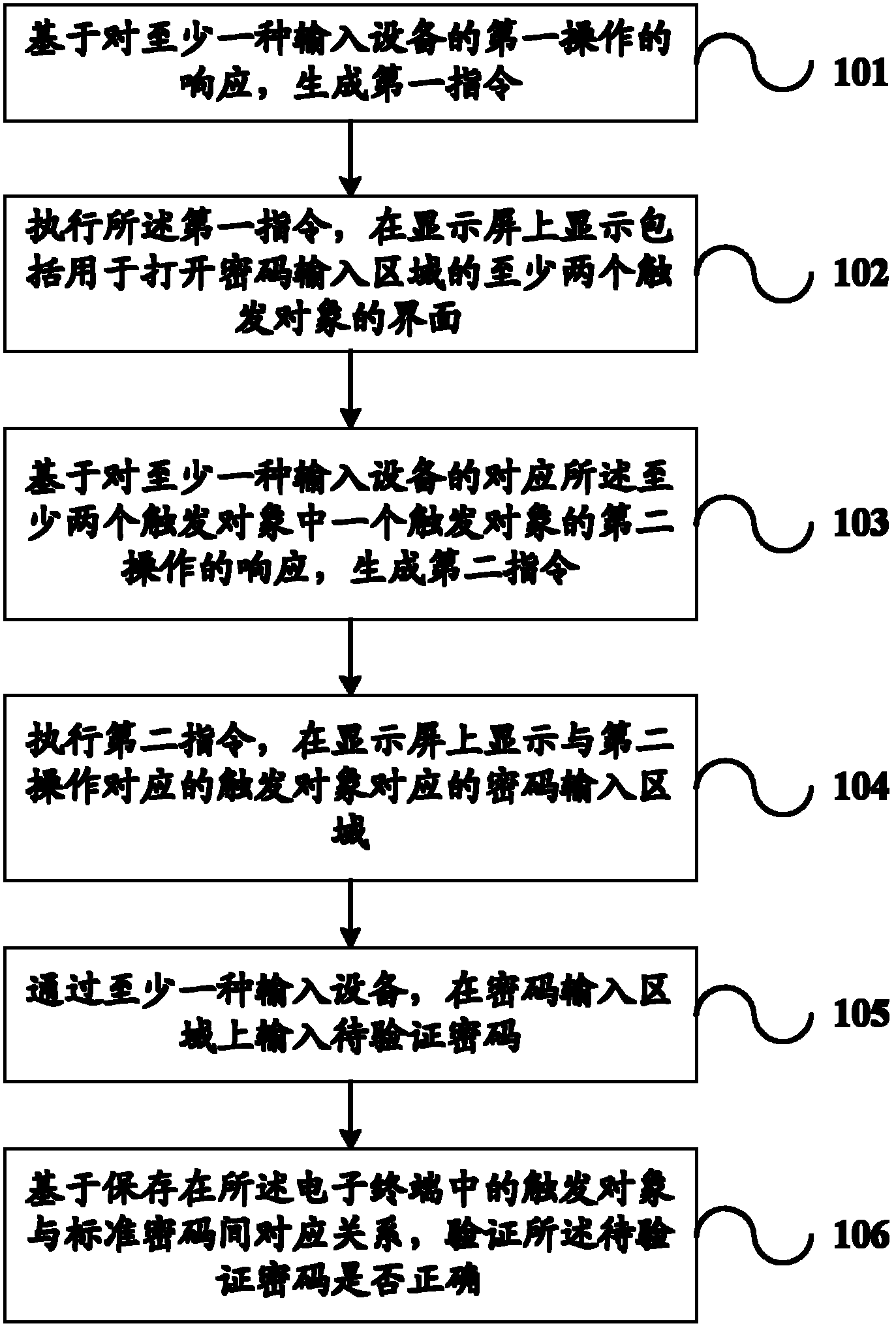

Method and system of password authentication

ActiveCN103136462AImprove protectionEasy to operateInput/output for user-computer interactionDigital data authenticationPasswordObject store

The invention discloses a method and a system of password authentication. The method and the system of password authentication are applied into an electronic terminal, wherein the electronic terminal comprises a display screen, at least one input device. The method of password authentication comprises the following steps: generating a first instruction based on a response to a first operation of the at least one input device, carrying out the first instruction and displaying an interface comprising at least two triggered objects which are used for opening a password input area, generating a second instruction based on a response of the at least one input device to a second operation of one triggered object of the at least two triggered objects, carrying out the second instruction and displaying a password input area corresponding to the triggered object corresponding to the second operation, inputting a password to be confirmed in the password input area through the at least one input device, and confirming whether the password to be confirmed is right or not based on the corresponding relation between the triggered object stored in the electronic terminal and a standard password.

Owner:LENOVO (BEIJING) CO LTD

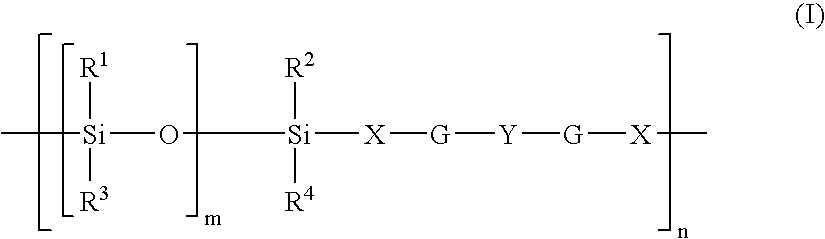

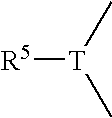

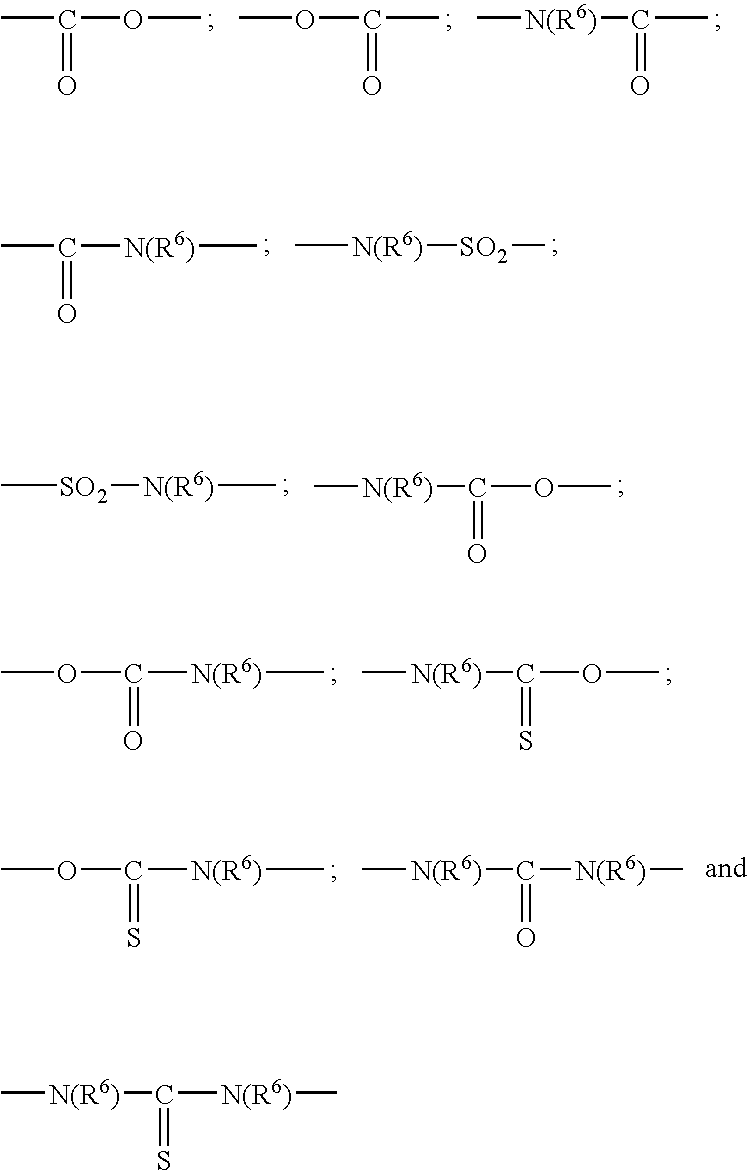

Composition containing a polyorganosiloxane polymer, a thickening agent and at least one volatile alcohol

The invention relates to a physiologically acceptable composition, especially a cosmetic composition, comprising (a) at least one polyorganosiloxane containing polymer comprising at least one moiety which comprises at least one polyorganosiloxane group consisting of 1 to about 1000 organosiloxane units in the chain of the moiety or in the form of graft, and at least two groups capable of establishing hydrogen interactions; (b) at least one volatile alcohol; and (c) at least one thickening agent, as well as to methods of using such compositions and kits containing such compositions.

Owner:LOREAL SA

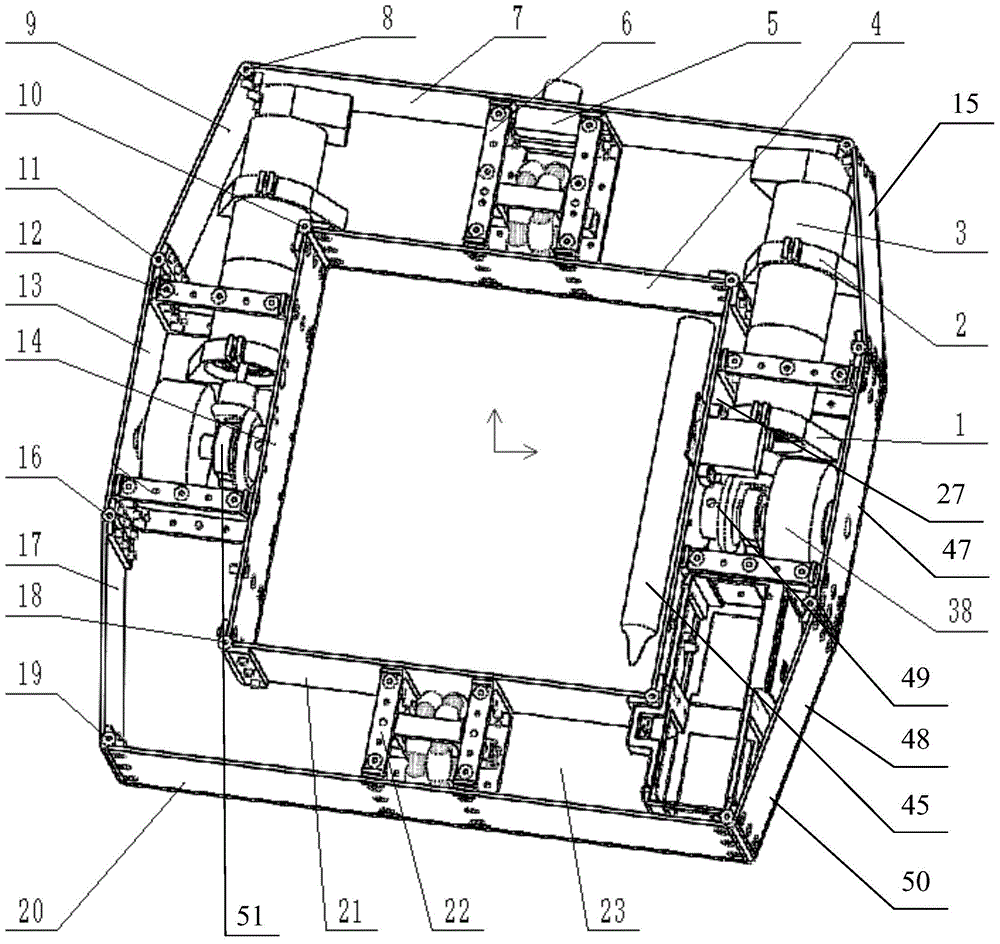

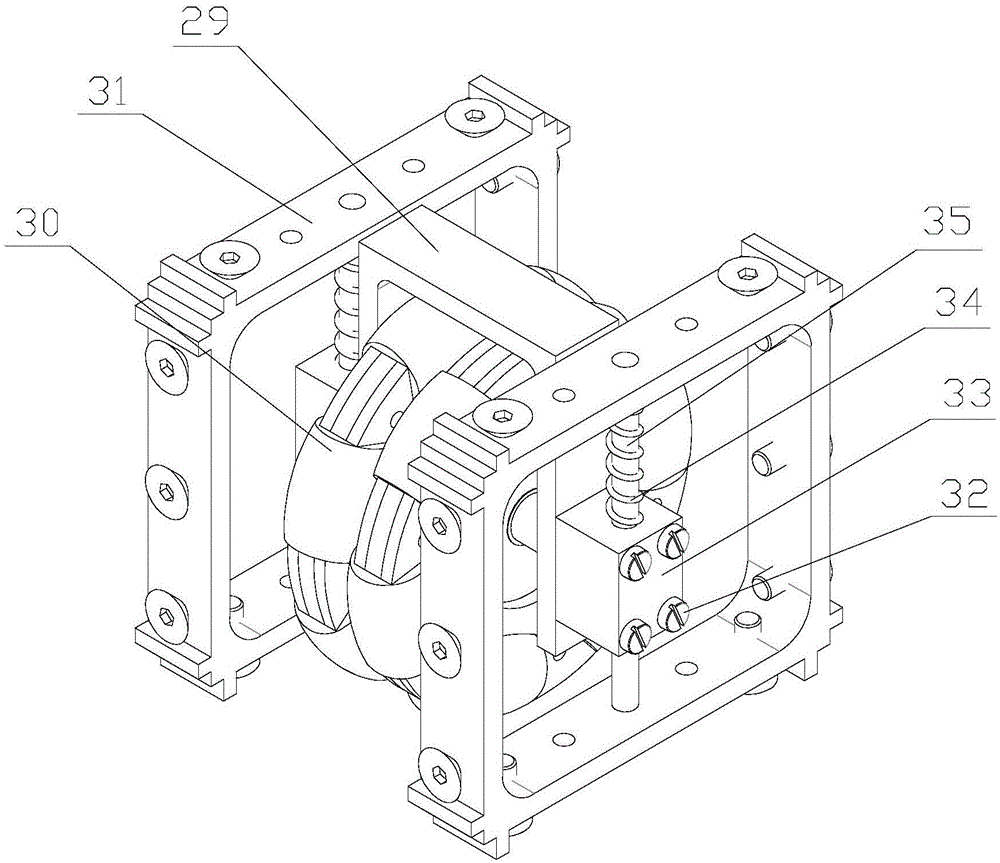

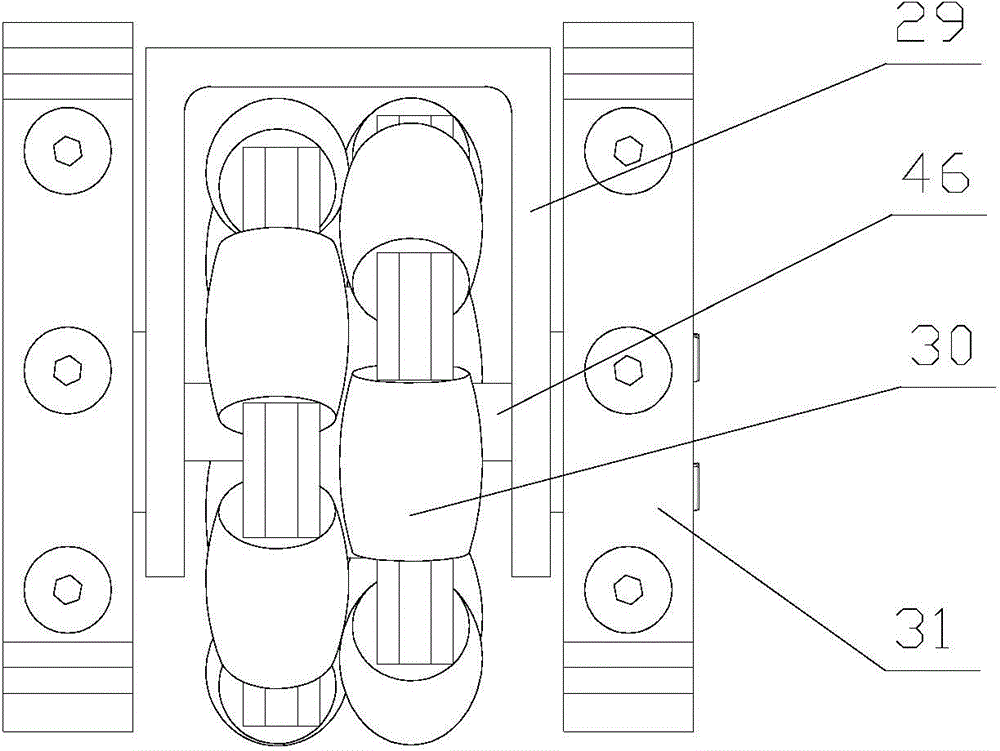

Magnetic-adsorption multifunctional flaw detection robot

ActiveCN104787144AMaximum adsorption capacityRetain flexibilityVehiclesCarrying capacityRemote control

The invention discloses a magnetic-adsorption multifunctional flaw detection robot and belongs to the technical field of robot manufacturing. The magnetic-adsorption multifunctional flaw detection robot is mainly used for flaw detection of large ships and tanks, data collection of a dangerous point and the like and is efficient, simple, flexible and high in carrying capacity. The magnetic-adsorption multifunctional flaw detection robot comprises a shell and a remote control handle arranged outside the shell, wherein a floating mechanism, a transmission mechanism, a controller, a motor and at least two magnetic wheels are arranged in the shell; the floating mechanism, the transmission mechanism, the controller and the motor are fixed in the shell; the power output end of the motor is fixedly connected with a wheel shaft of the magnetic wheels through the transmission mechanism; the control end of the motor is connected with the controller; a wireless emitter is arranged in the remote control handle; a wireless receiver is arranged in the shell, corresponds to the wireless emitter and is connected with the controller; a camera is arranged on the shell and connected with an external display screen through an image transmission module.

Owner:NORTHEASTERN UNIV

Preparation method for flexible heat-conducting pad

InactiveCN103965839AImprove thermal conductivityRetain flexibilityHeat-exchange elementsPorosityHeat conducting

The invention relates to a preparation method for a flexible heat-conducting pad. The preparation method comprises the following steps: providing a foam metal; providing a heat-conducting material; and filling the foam metal with the heat-conducting material so as to form the heat-conducting pad. According to the invention, gaps of the foam metal are filled with the material with good heat-conducting performance and a proper size, so the prepared heat-conducting pad has better heat-conducting capability compared with the foam metal and the filling material before treatment and retains good flexibility of the foam metal; through adjusting parameters like thickness and porosity of the foam metal and parameters like variety, components and quality of the filling material, the thickness, heat conductivity coefficient, flexibility and the like of the heat-conducting pad can be controlled; the prepared heat-conducting pad can be cut into any shape. The preparation method has high repeatability and is simple and easily practicable.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

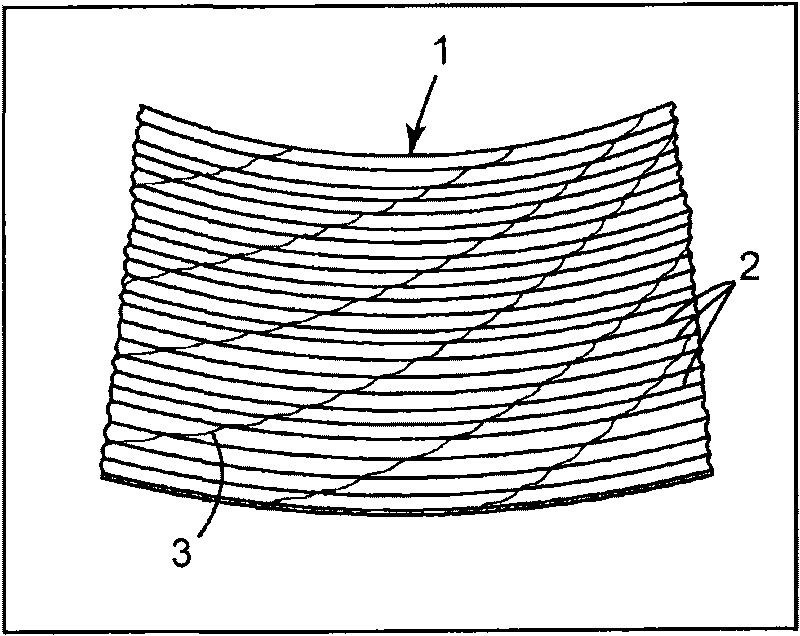

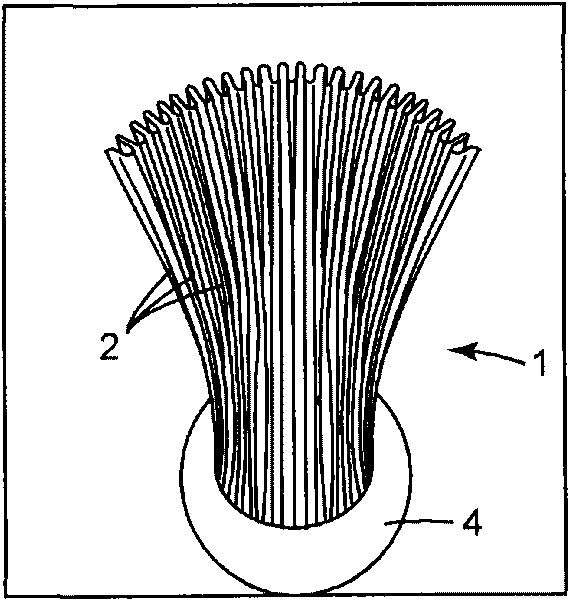

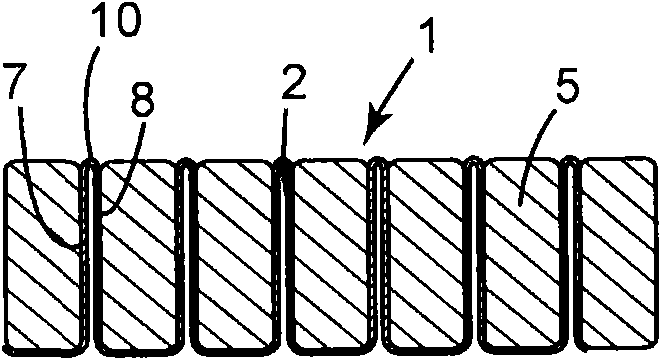

Corrugated skins for aircraft and methods of their manufacture

InactiveCN101723084ARetention strengthRetain flexibilityEfficient propulsion technologiesFuselage bulkheadsMorphingEngineering

A skin (1) for a morphing structure of an aircraft is disclosed, said skin comprising one or more corrugations (2). A corresponding method of manufacturing a skin for a morphing structure of an aircraft is also disclosed comprising shaping the skin (1) to a desired form including one or more corrugations (2). In one embodiment, Aluminium forming bars (5) are sequentially introduced between folds (7, 8) in the material of the skin.

Owner:GE AVIATION SYST LTD

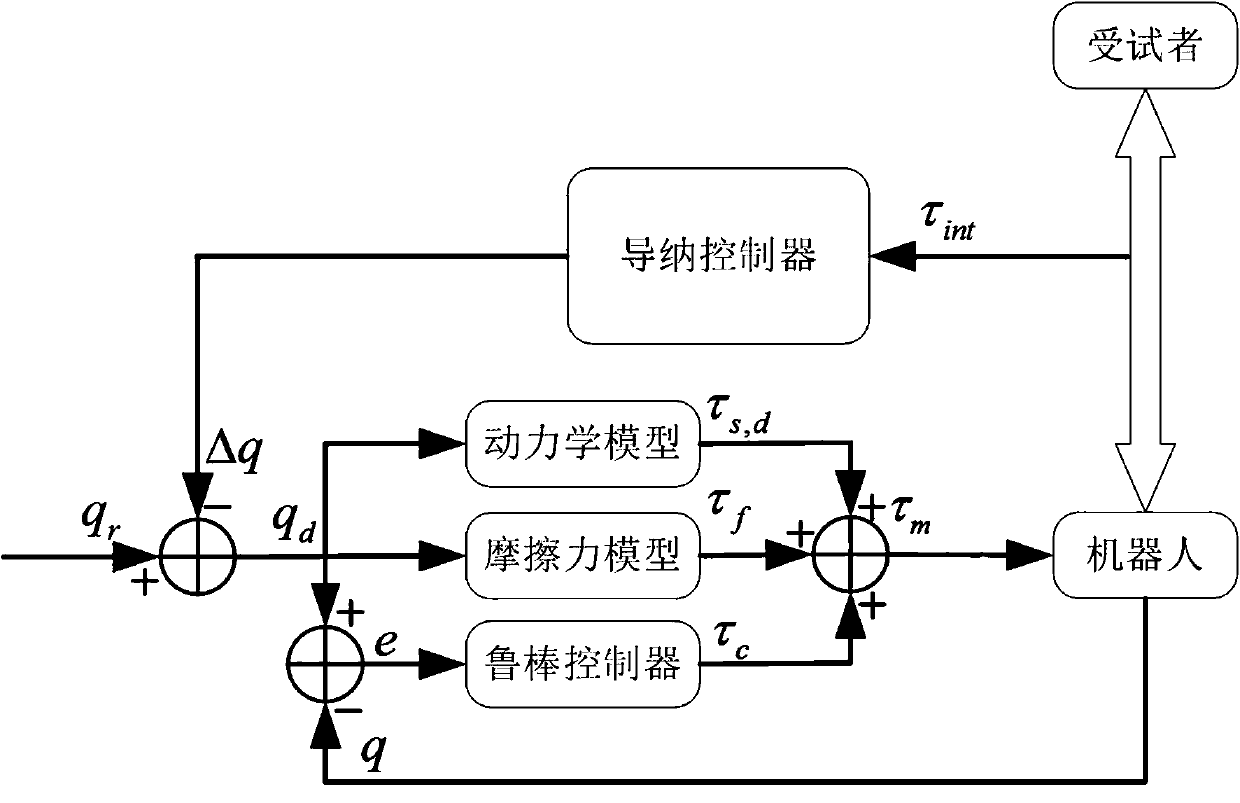

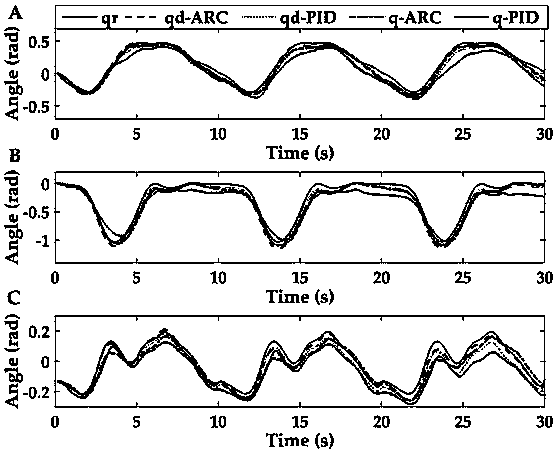

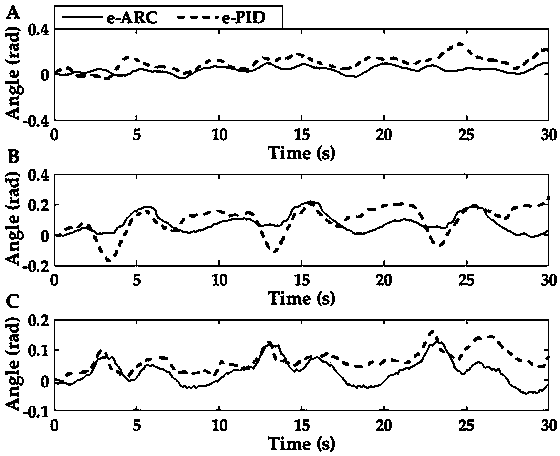

Control method of lower limb rehabilitative robot based on combination of robust control and admittance control

InactiveCN109806106AEliminate distractionsImprove robustnessChiropractic devicesRobust control systemAdmittance

The invention discloses a control method of a lower limb rehabilitative robot based on the combination of robust control and admittance control. A robust controller is added in traditional admittancecontrol, so that a whole control system has the flexibility of the admittance control and anti-interference performance of the robust control; furthermore, shaking influences of system friction and the robust control are also considered and are compensated and balanced, so that the control precision is wholly improved.

Owner:SUN YAT SEN UNIV

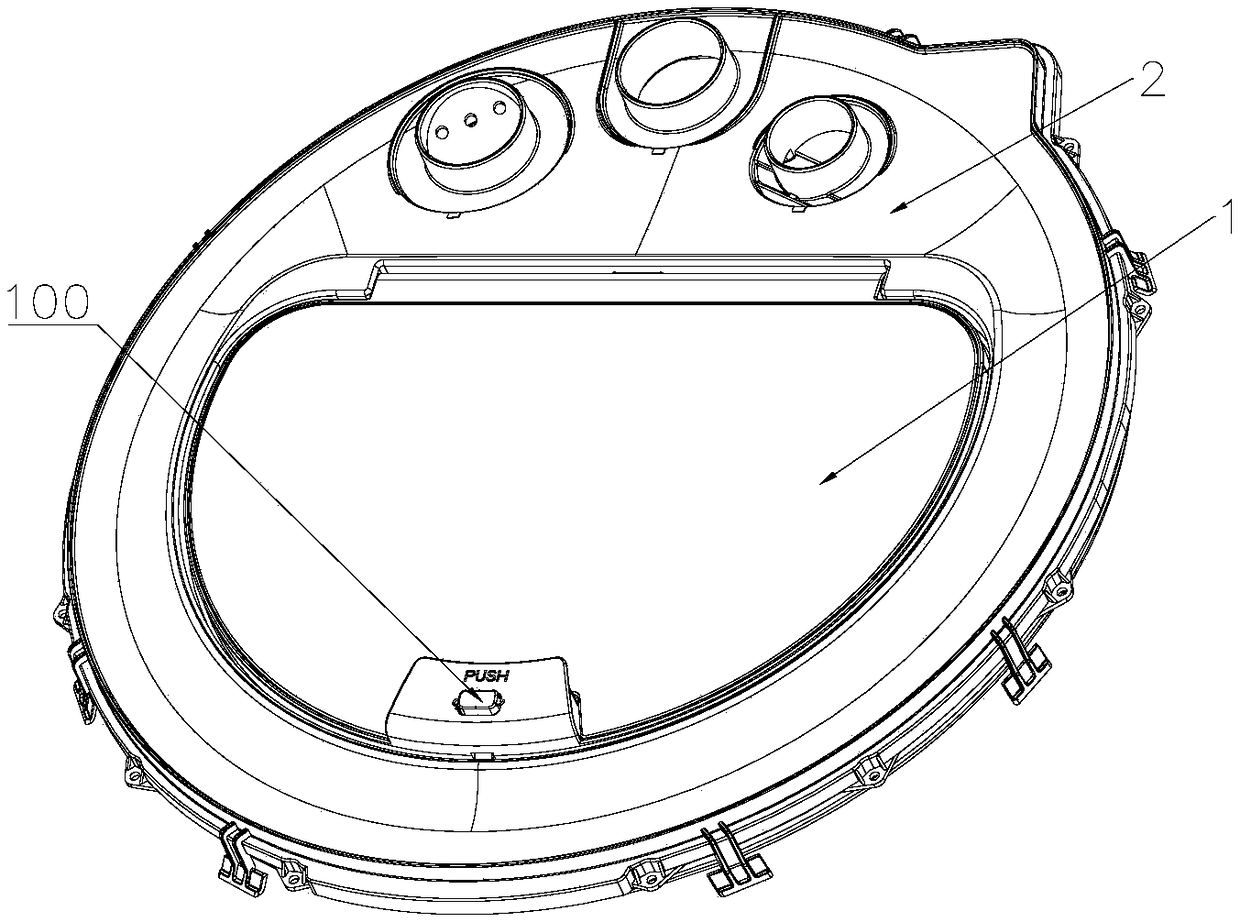

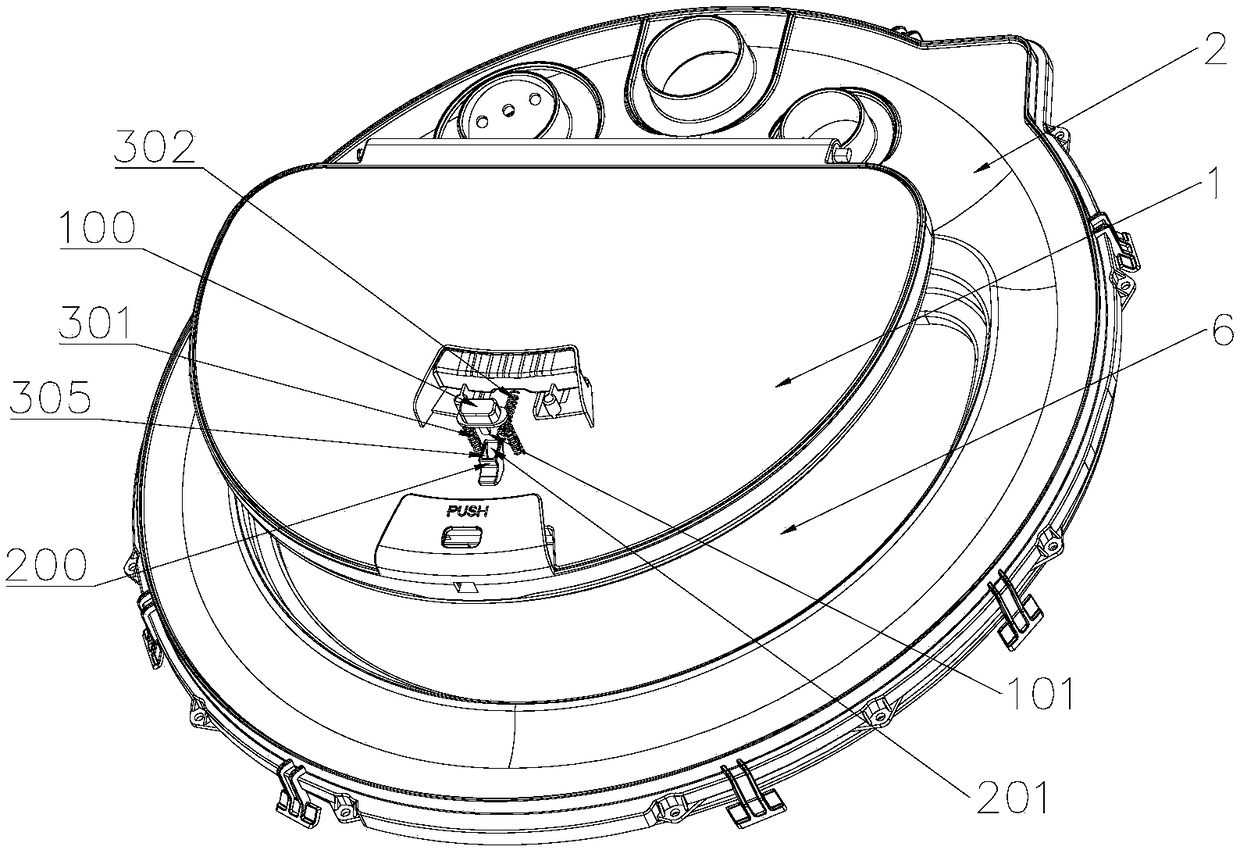

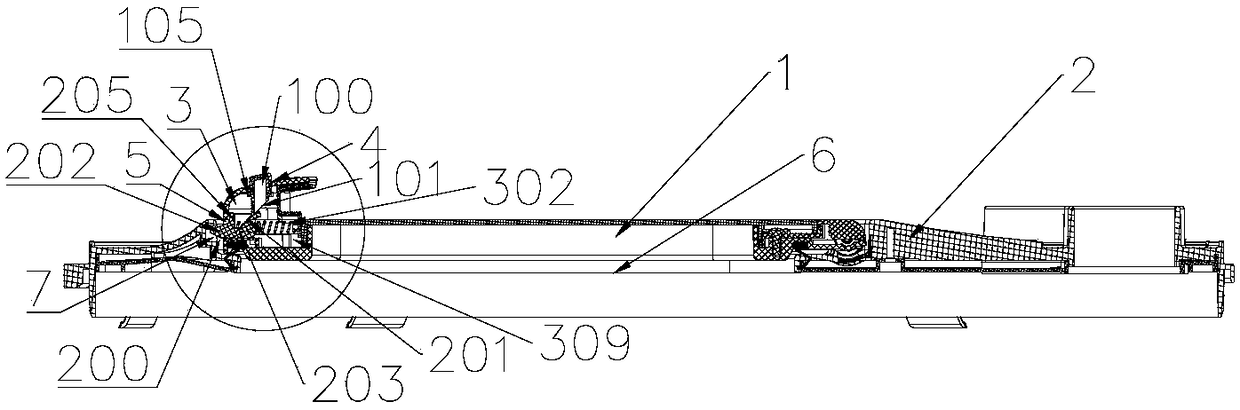

Washing machine

ActiveCN108179597AReduce overflowImprove drying efficiencyOther washing machinesTextiles and paperPulp and paper industry

The invention belongs to the field of washing machines, and particularly relates to a washing machine. The washing machine comprises an inner cover, a sealing ring and an outer cylinder cover; the sealing ring is arranged between the inner cover and the outer cylinder cover and comprises a body provided with a deformation part; when the inner cover and the outer cylinder cover are locked, the deformation part deforms to seal the inner cover and the outer cylinder cover. The washing machine has the advantages that the sealing ring is arranged between the inner cover and the outer cylinder cover, thus the gap between the inner cover and the outer cylinder cover is sealed through the sealing ring to reduce the hot wind or washing water overflow situation, and the drying efficiency is improvedor washing water overflow is reduced.

Owner:CHONGQING HAIER WASHING MASCH CO LTD +1

Direct-vat type high-adhesion bituminous mixture modifier and preparation method thereof

InactiveCN104693823AControl "Secondary Pollution"Low costBuilding insulationsBulk chemical productionCrack resistancePolymer science

The invention discloses a direct-vat type high-adhesion bituminous mixture modifier and a preparation method thereof. The modifier is prepared by regenerated rubber with high desulfurization degree, modified high-temperature coal tar pitch and a skeleton proppant at the mass ratio of (30-50) to (30-50) to (5-20) in stirring and extruding manners. The preparation method of the modifier comprises the following steps: deeply activating waste rubber through high-temperature and high-shearing action of a double-screw extruder, thus obtaining the high-desulfurization degree regenerated rubber; fully mixing a mixture of the modified high-temperature coal tar pitch, the high-desulfurization degree regenerated rubber and a skeleton backing material, which is modified by rubber pyrolysis oil under the blending action of a screw; and extruding and pelleting, so as to prepare the direct-vat type high-adhesion bituminous mixture modifier. The modifier disclosed by the invention is directly fed when the mixture is stirred, no extra equipment is used, and the process is simple and easy to operate; the bituminous mixture prepared by the method has excellent moisture damage resistance, good high-temperature anti-rutting performance, low-temperature crack resistance and excellent economic and social benefits.

Owner:TIANJIN HI TECH ENVIRONMENT DEV CO LTD

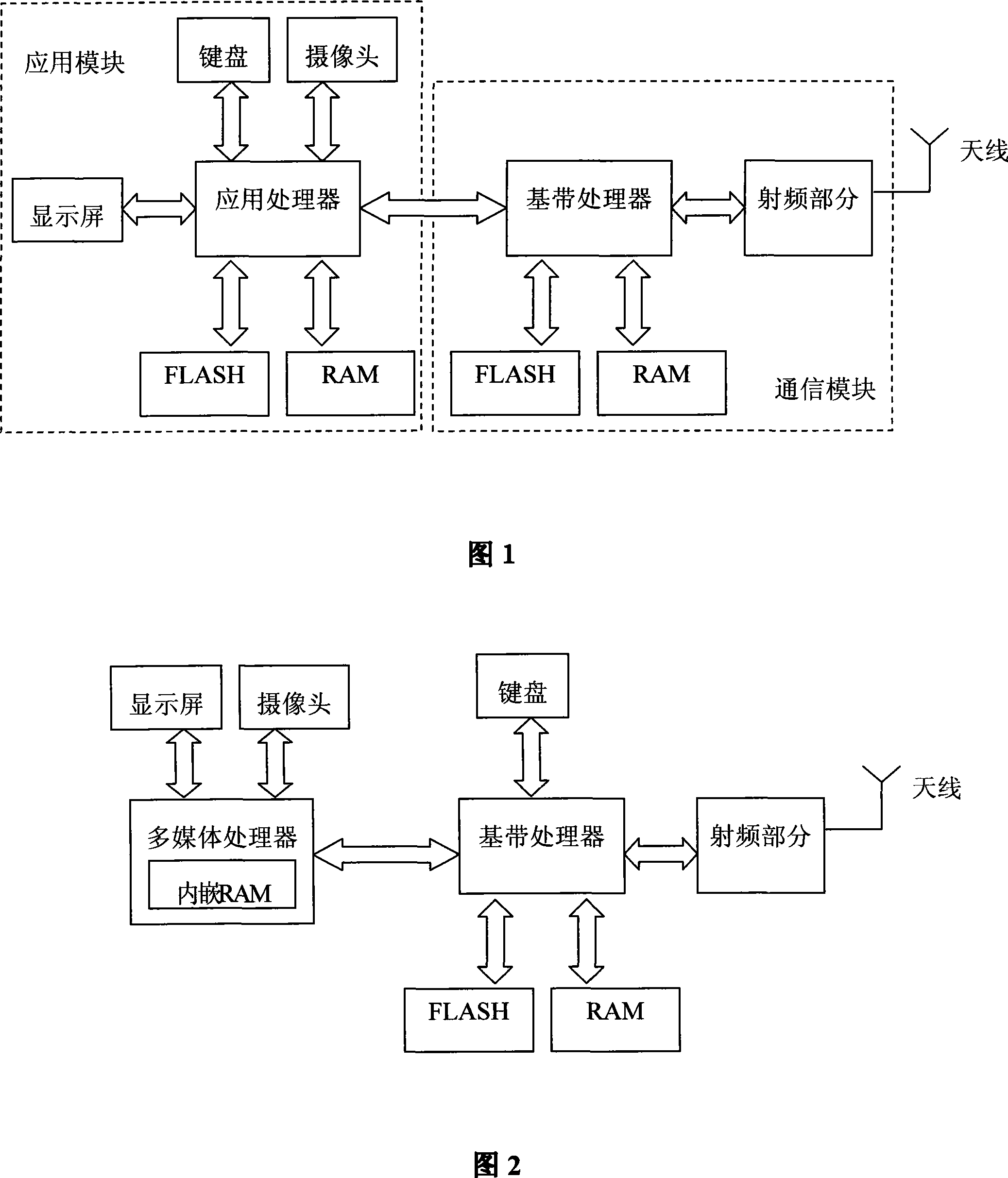

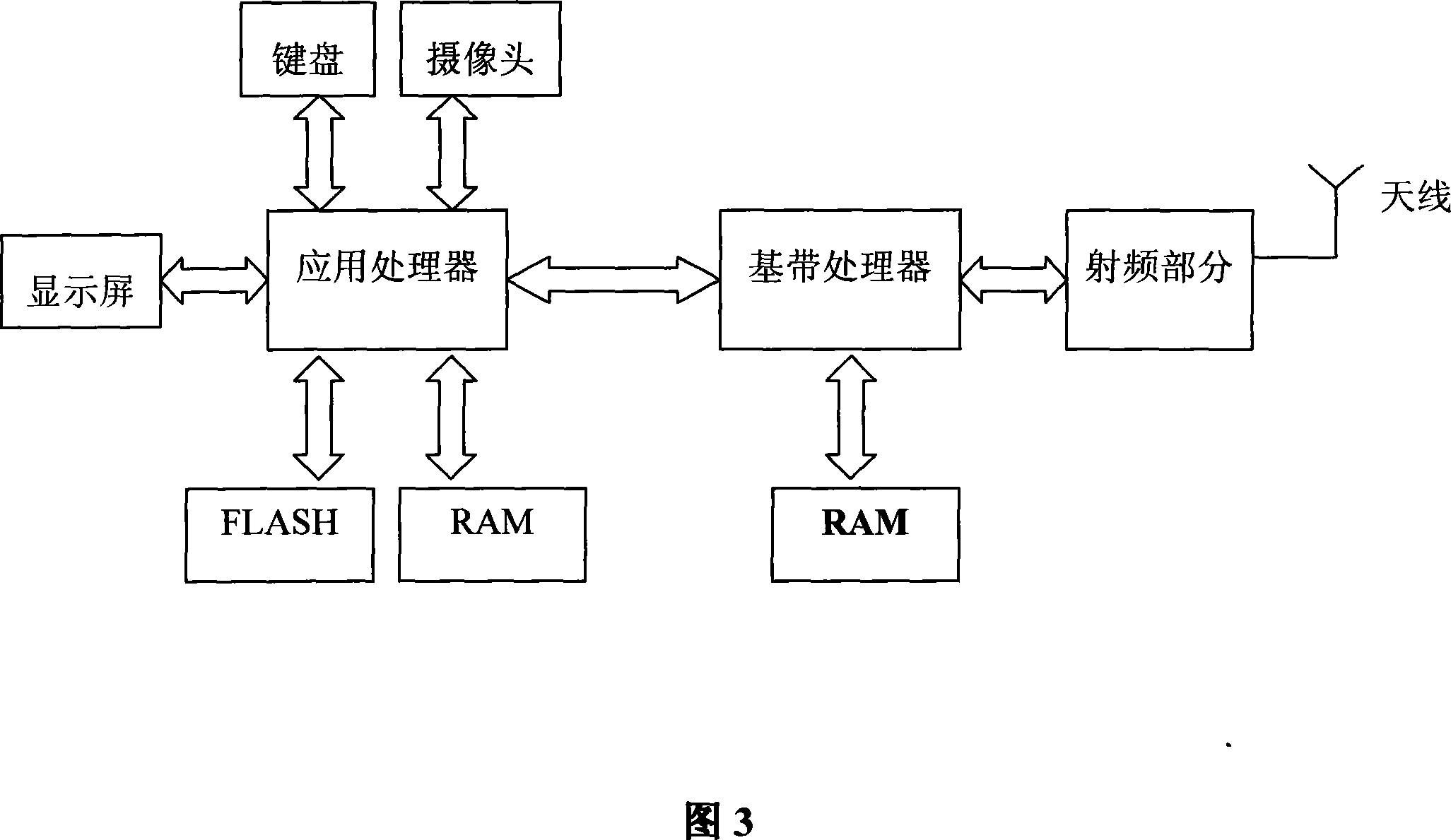

A mobile telephone based on application processor structure

InactiveCN101217735ARetain flexibilityOmit FLASHRadio/inductive link selection arrangementsTransmissionComputer architectureApplication processor

The invention provides a mobile phone which is based on a processor structure application. The invention is mainly characterized in that the invention implements the functions which are completely the same with those of the mobile phone in which the processor structure is applied, achieves the starting skillfully by adopting the external starting mode of the baseband processor of the mobile phone through a baseband processor which is controlled by the application processor, thus abolishing the FLASH which is externally connected with the original baseband processor and used for storing programs and other data. Therefore, the invention remains the flexibility and succession of the software of the mobile phone in which the processor structure is applied, reduces the cost of the whole machine at the same time, and has important and practical significance.

Owner:WINGTECH COMM