Low power content addressable memory architecture

A memory and memory array technology, applied in the field of CAM architecture, can solve the problems of unsuitable battery power and low power consumption applications, not taking into account, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

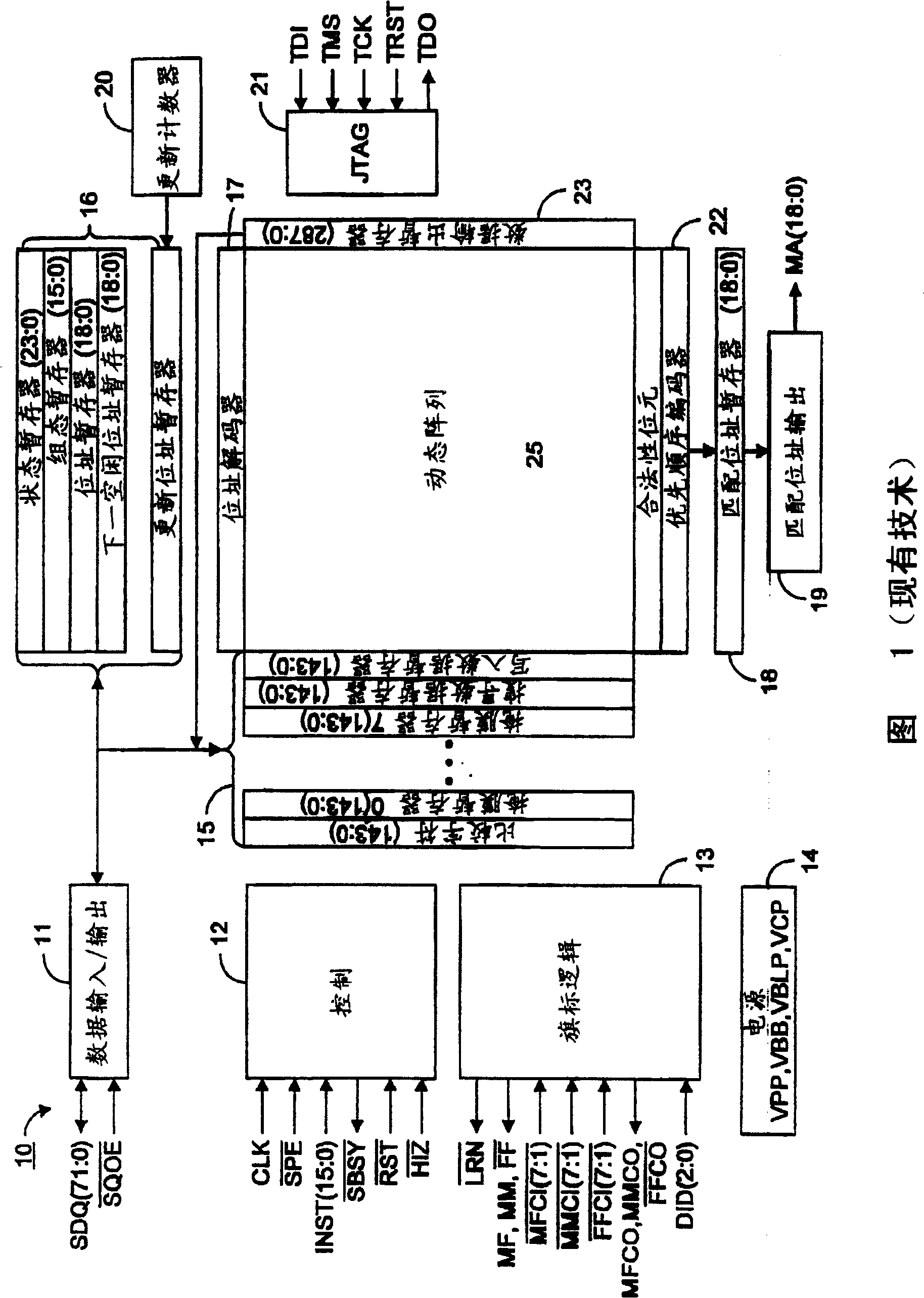

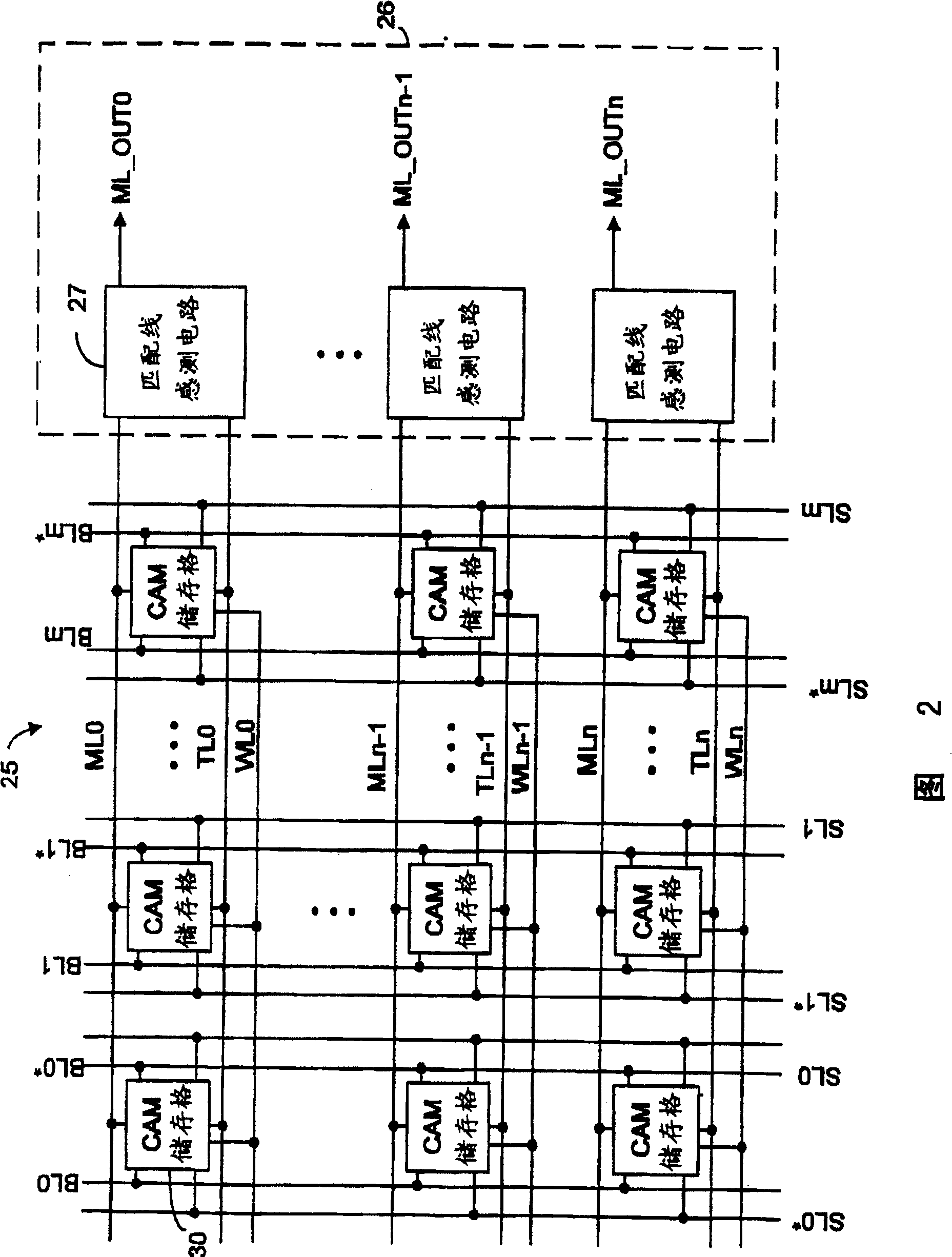

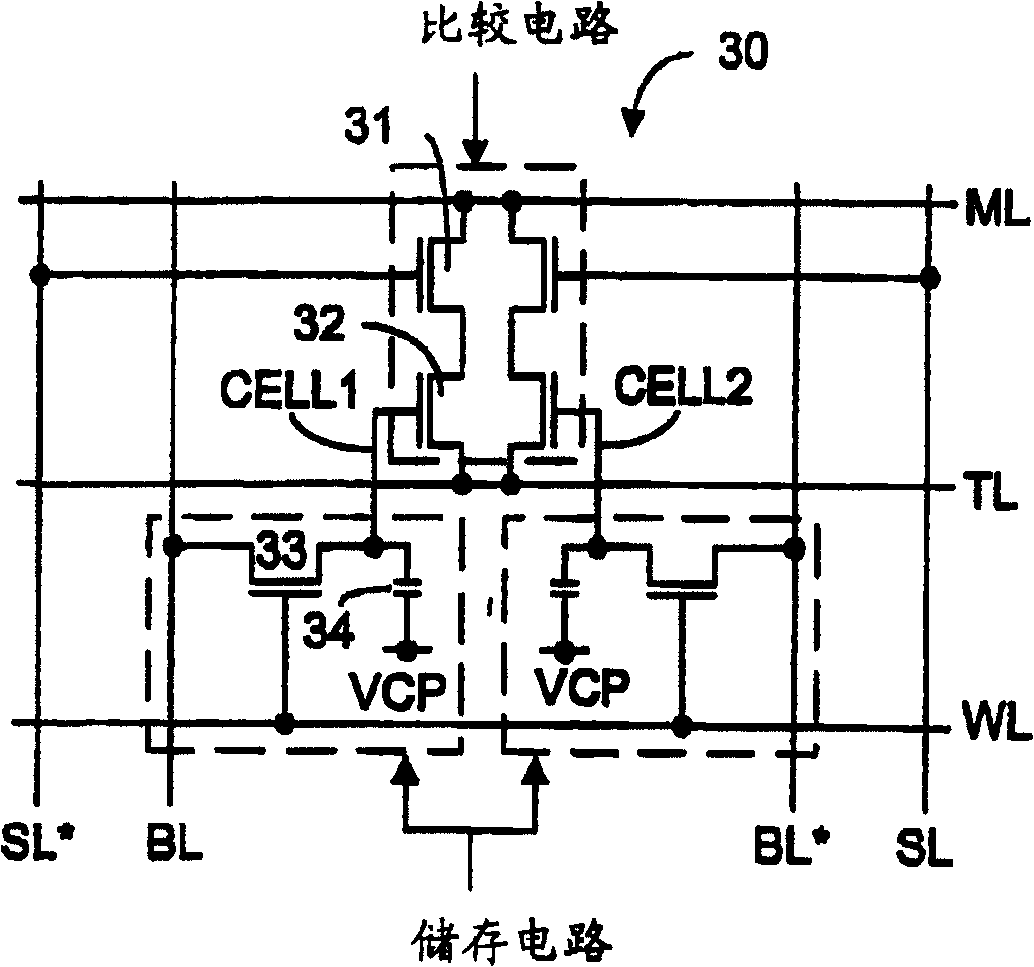

[0039] A low power consumption CAM architecture is hereby disclosed. The matching line of this CAM array is segmented into two search sections: a pre-search section and a main search section. After the search command is issued, the first search operation is performed at the pre-search part of the matching line, that is, the pre-search is performed. If the result of the preliminary search is a match, then a second search is performed on the main search portion of the matching line, that is, the main search is continued. If the result of the pre-seek is a mismatch, the main seek is disabled and the main seek is not performed, so there is no power dissipation in the main seek of the match line. Both pre-search and main search operations can be pipelined to maintain high throughput and minimum latency. The power consumption can be further reduced by using the match line sensing circuit to detect the current on the match line pre-search section and the main search section. The m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More