Heat radiation type packaging structure and its making method

A packaging structure and heat dissipation technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve the problems of large stamping or cutting tool loss, inability to greatly improve production efficiency, and affect the appearance of packages, etc. Less wear and tear, conducive to cutting cost control, not easy to produce burrs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

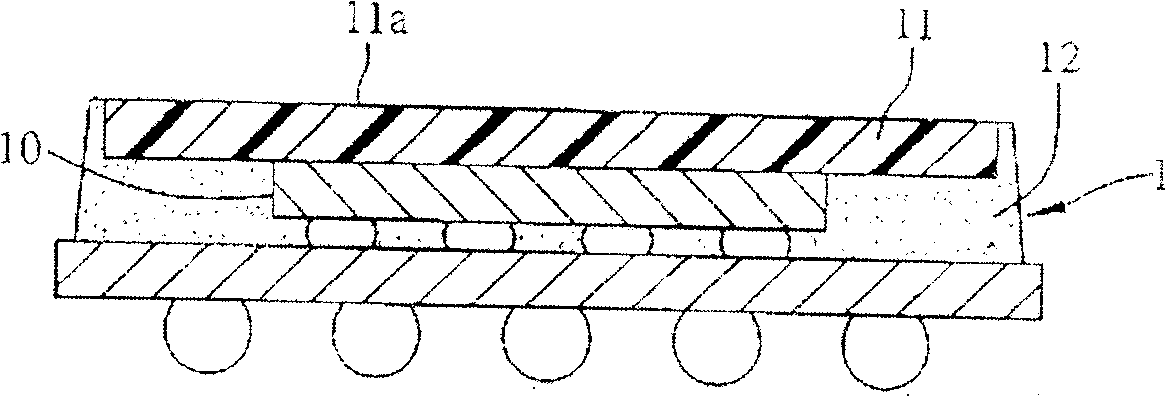

[0043] See Figure 4A to Figure 4F , It is a schematic diagram of the manufacturing process of Embodiment 1 of the manufacturing method of the heat-dissipating package structure of the present invention.

[0044] Such as Figure 4A and Figure 4B As shown, first, a matrix substrate module sheet 40A is provided, and the substrate module sheet 40A is composed of a plurality of substrate units 40 arranged in an array. The substrate unit 40 has an upper surface 400 and a lower surface 401 respectively, and a through hole 402 is opened. In addition to being arranged in an array, the substrate unit 40 can also be arranged in a straight strip, and if the process conditions permit, it can also be carried out in a single substrate unit.

[0045] Then, at a predetermined position on the upper surface 400 of each substrate unit 40, the active surface 41a of the chip 41 is connected to it through an adhesive layer 45 such as silver glue, and the chip 41 is made to seal the opening 402. At one...

Embodiment 2

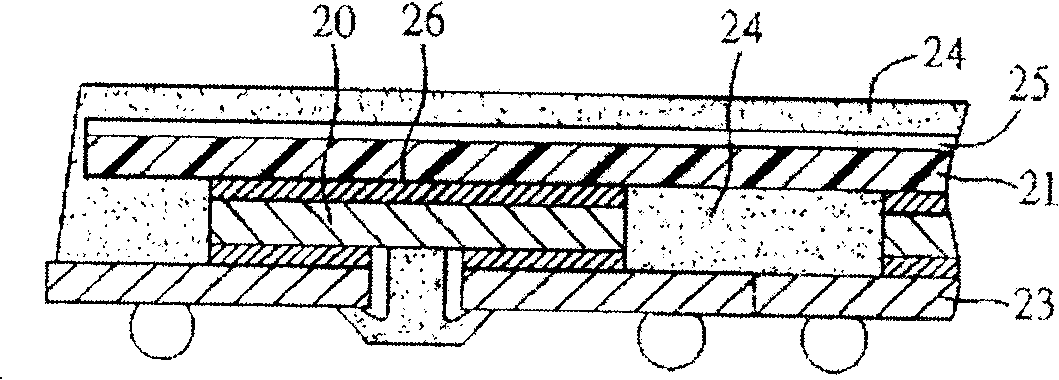

[0052] Please refer to FIGS. 5A to 5G, which are schematic diagrams of the manufacturing process of Embodiment 2 of the manufacturing method of the heat dissipation type package structure of the present invention. The process of the second embodiment of the present invention is roughly the same as that of the first embodiment, and the main difference is that the semiconductor chip in the second embodiment is flip-chip connected and electrically connected to the substrate.

[0053]As shown in FIGS. 5A and 5B, first, a matrix substrate module sheet 50A is provided. The substrate module sheet 50A is composed of a plurality of substrate units 50 arranged in an array. The substrate unit 50 each has an upper surface 500 and a lower surface 501. Wherein, the substrate unit 50 can be arranged in a straight strip manner in addition to being arranged in an array manner, and if the process conditions permit, it can also be performed in a single substrate unit manner.

[0054] Next, at a pred...

Embodiment 3

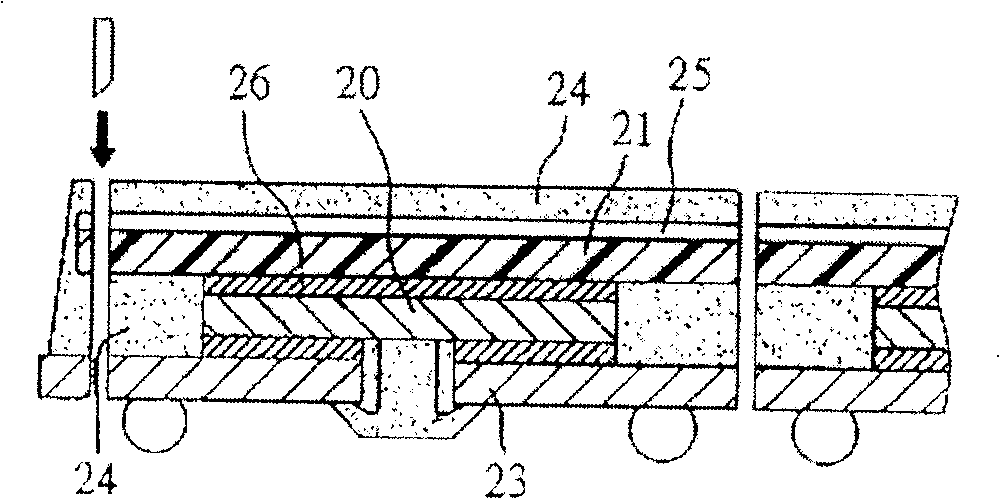

[0061] See Figure 6 As shown, it is a schematic cross-sectional view of Embodiment 3 of the semiconductor package structure made by the above-mentioned heat-dissipating package structure manufacturing method of the present invention. The packaging structure of the present invention includes: a chip carrier, a semiconductor chip, a heat sink, and a packaging colloid. The semiconductor package structure of the present invention is manufactured by a method similar to the preparation embodiment 1 and embodiment 2. The difference is that in the semiconductor package structure of the present embodiment, the heat sink connected to the semiconductor chip 61 63 is formed with an opening 63b at a position corresponding to the connecting chip 61, that is, at the position of the connecting chip 61, the thin metal layer 631 and the insulating core layer 630 on the lower surface of the heat sink 63 are removed, so as to be on the heat sink 63 An opening 63b exposing the thin metal layer 631 on...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More