Method for manufacturing inlaid structure

A manufacturing method and technology of damascene structure, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as dielectric layer damage, and achieve the effects of maintaining breakdown voltage, reducing damage, and eliminating photoresist residues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

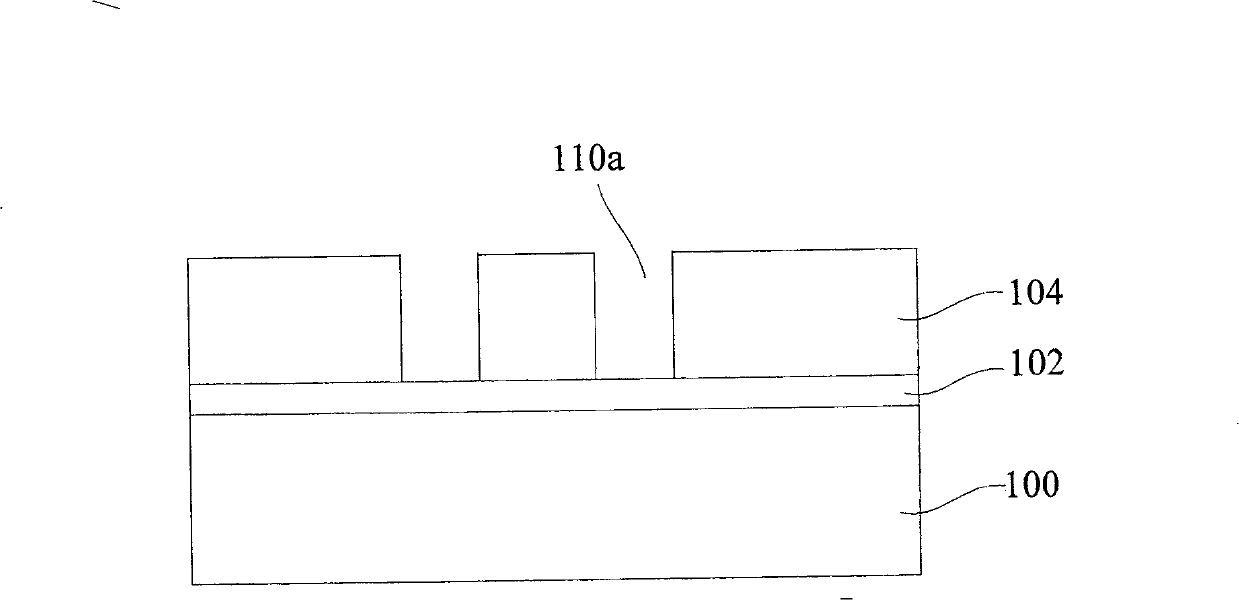

[0027] In the manufacturing process of the mosaic structure of the present invention, the photoresist layer formed on the low dielectric constant dielectric layer is removed by oxygen plasma ashing. The damage to the dielectric layer caused by the ion bombardment during the chemicalization process maintains the breakdown voltage of the dielectric layer, thereby improving the stability of the formed device.

[0028] Figure 6 It is a flowchart of an embodiment of the manufacturing process of the damascene structure of the present invention.

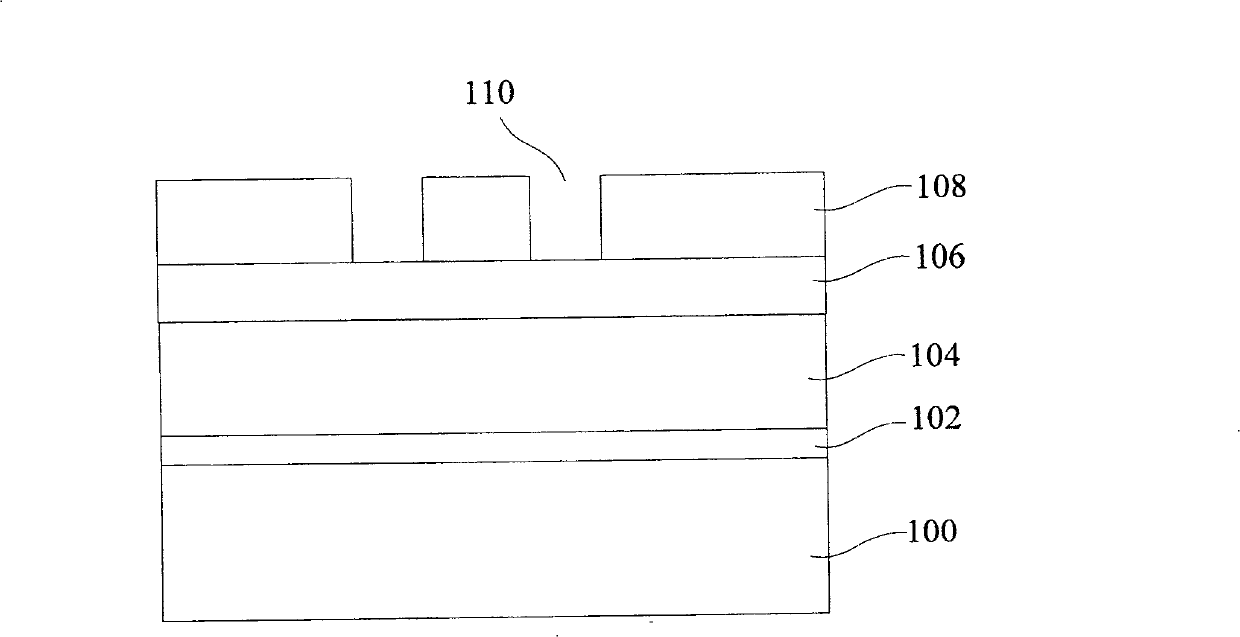

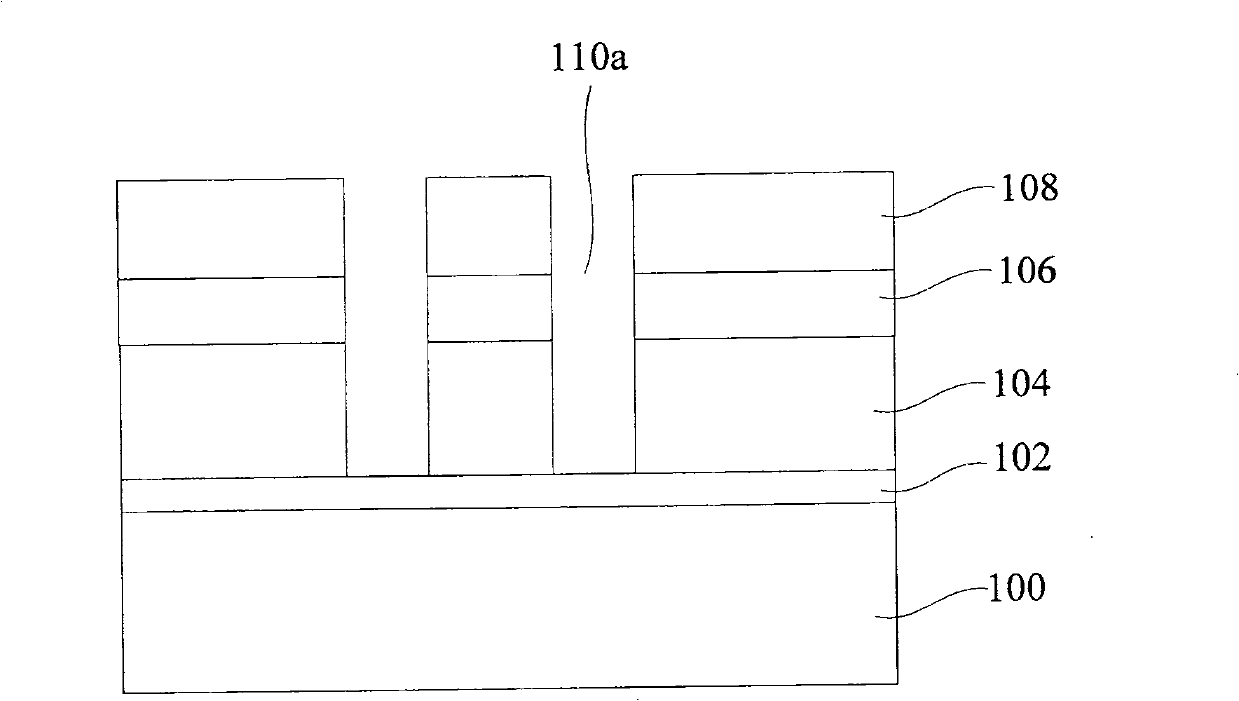

[0029] like Figure 6 As shown, first, a semiconductor substrate is provided, and a conductive layer is formed in the semiconductor substrate ( S100 ). The semiconductor substrate can be polycry...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More