Clock deviation arrangement method driven by production yield under technique parametric variation

A technology of clock deviation and process parameters, applied in the field of clock deviation arrangement driven by yield rate, can solve the problems of improving yield rate and unfavorable

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0071] The present invention is further illustrated below by specific examples.

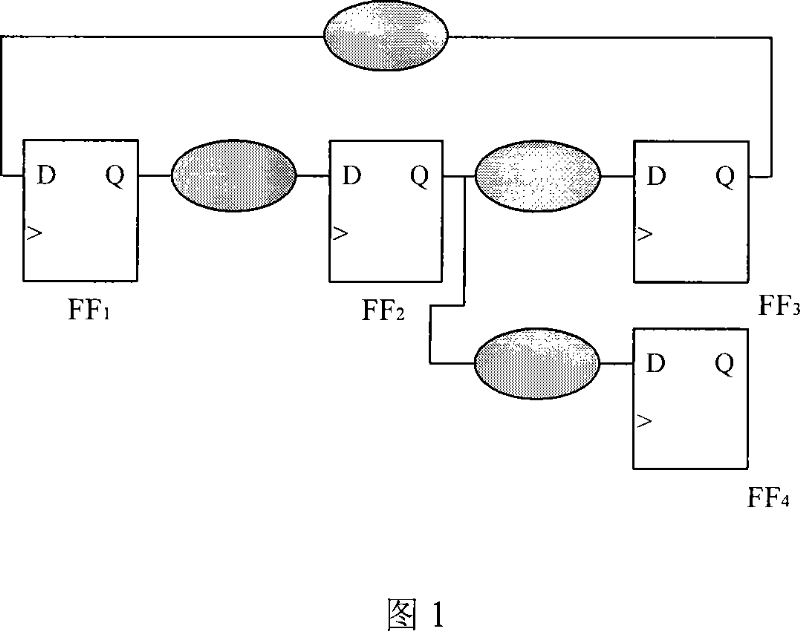

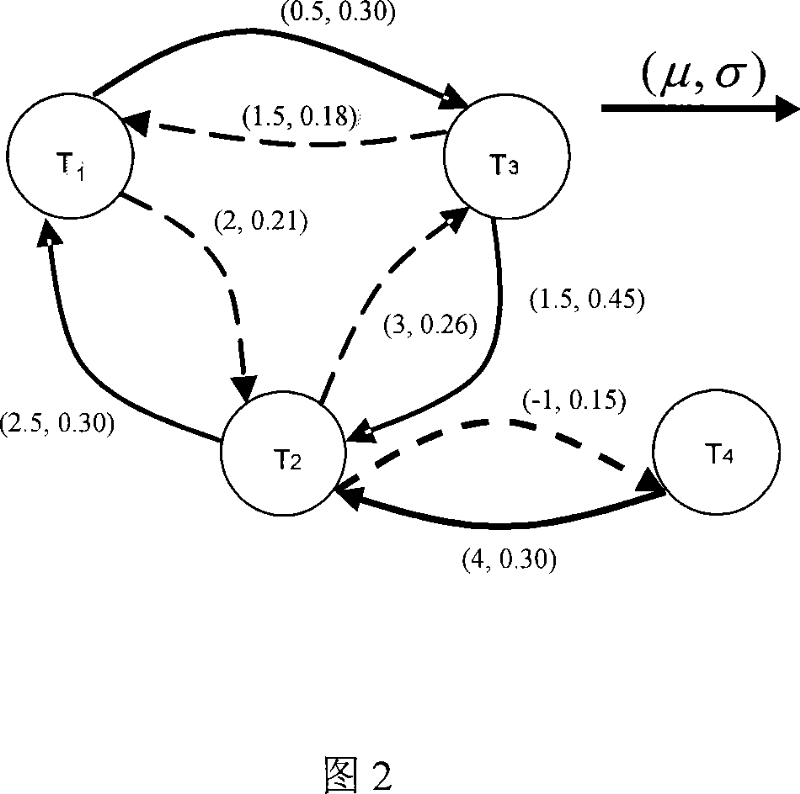

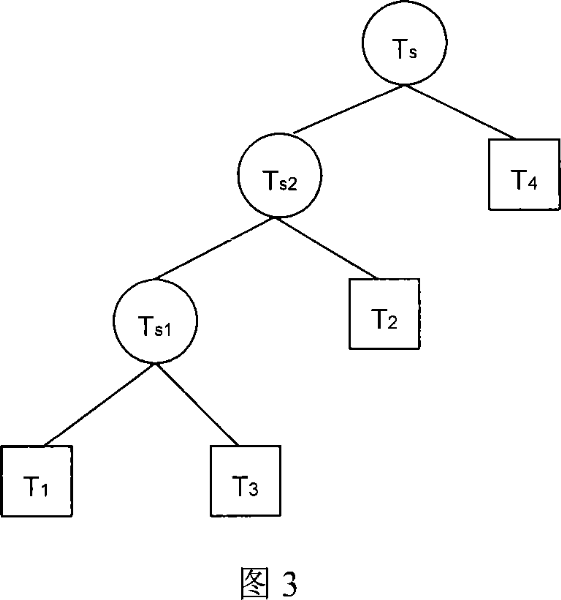

[0072] Standard test circuits using ISCAS'89, which includes flip-flops and combinational circuits. Before arranging the clock skew, it is necessary to perform statistical timing analysis to obtain the probability distribution information of the maximum delay and the minimum delay between flip-flops with adjacent timings. When doing statistical timing analysis, it is assumed that the delay of each logic gate obeys a mutually independent Gaussian distribution N(μ, σ 2 ). In the experiment, μ=1ps and σ=0.15ps are selected.

[0073] circuit name

Number of triggers

clock skew approx.

bundle number

clock cycle

(ps)

Timing Yield (%)

Props

Method of the invention

α=1.5

α=

S344

15

74

19.40

84.86

87.50

1.633,87.72

S526

21

123

10.00

90.99

95.74

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More