Wafer level packaging method and its structure

A chip packaging and chip technology, which is applied in the field of integrated wafer-level packaging technology, can solve the problems of increasing packaging structure failures and complex processes, and achieve the effects of reducing time and complexity, reducing packaging time, and being easy to rework.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0093] The purpose, functions and advantages of the present invention can be better understood through the following detailed description and corresponding illustrations.

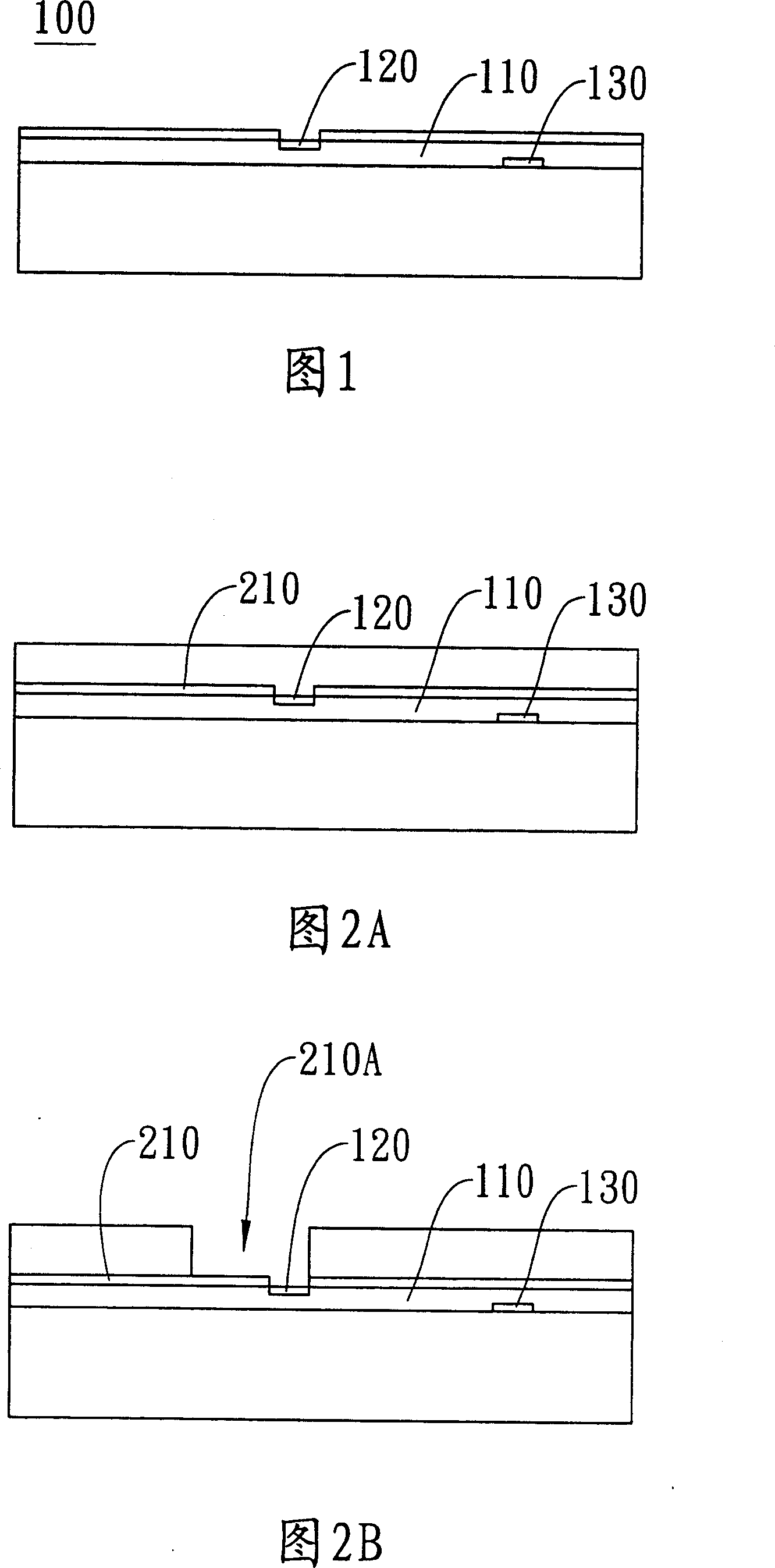

[0094] Please refer to FIG. 1, which is a chip 100 according to a preferred embodiment of the present invention, the chip 100 includes at least one circuit element 110, at least one surface connection pad 120 and at least one internal connection pad 130, and the circuit element 110 is located on the In the chip 100 , the surface connection pad 120 is located on the surface side of the chip 100 , and the internal connection pad 130 is located in the chip 100 and is electrically connected to the circuit element 110 .

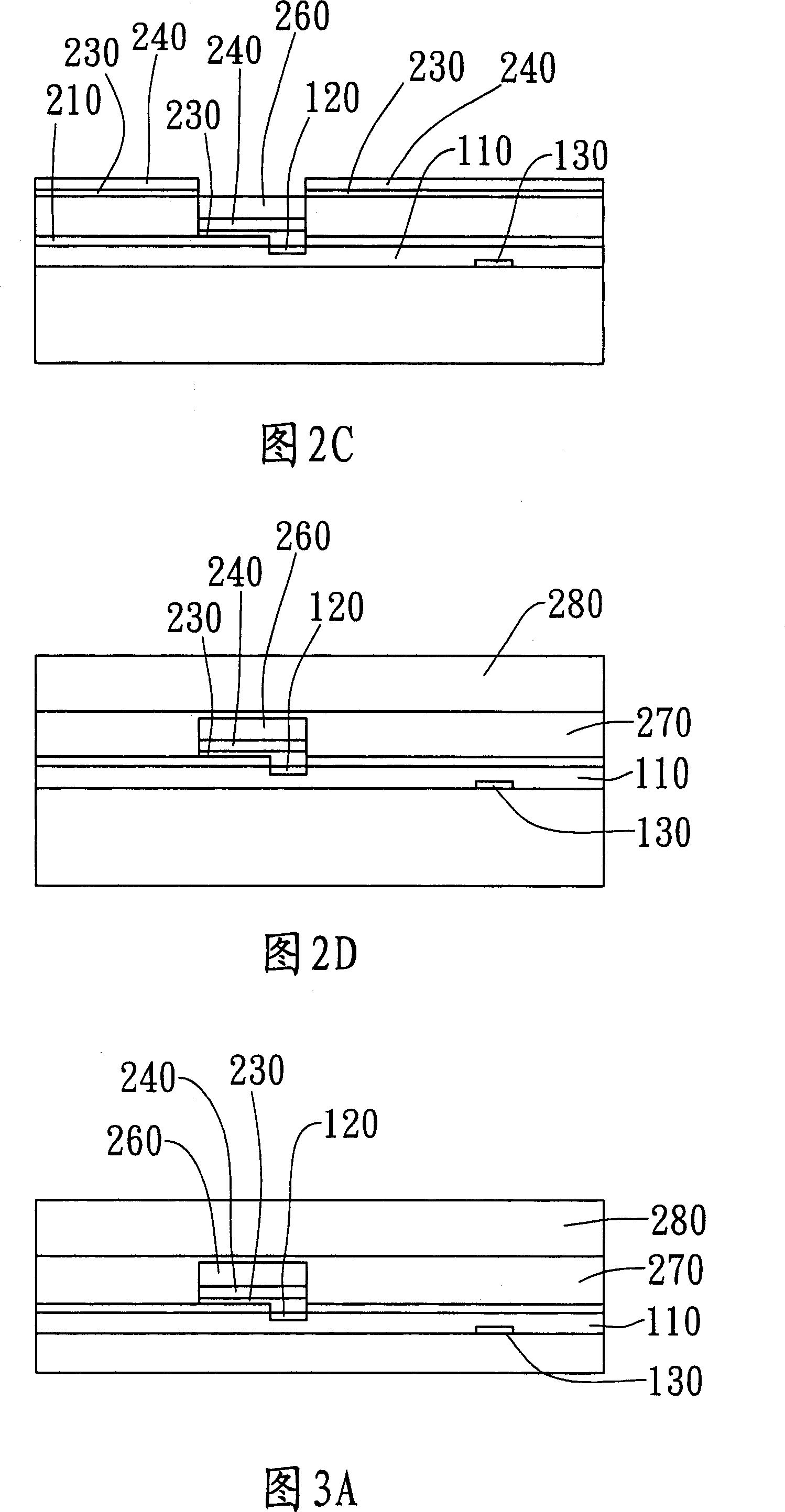

[0095] First, a surface activation process can be selectively implemented according to needs. The surface activation process is used to remove pollutants on the wafer surface and surface connection pads, such as oxides or particles, so as to increase the connection between the wafer surface and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More