Semiconductor wafer welding material projected block structure and its production

A technology of solder bumps and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of poor consistency of solder bump height and volume, and achieve consistent height and volume Easy to control, high density of solder joints, beneficial to miniaturization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0054] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

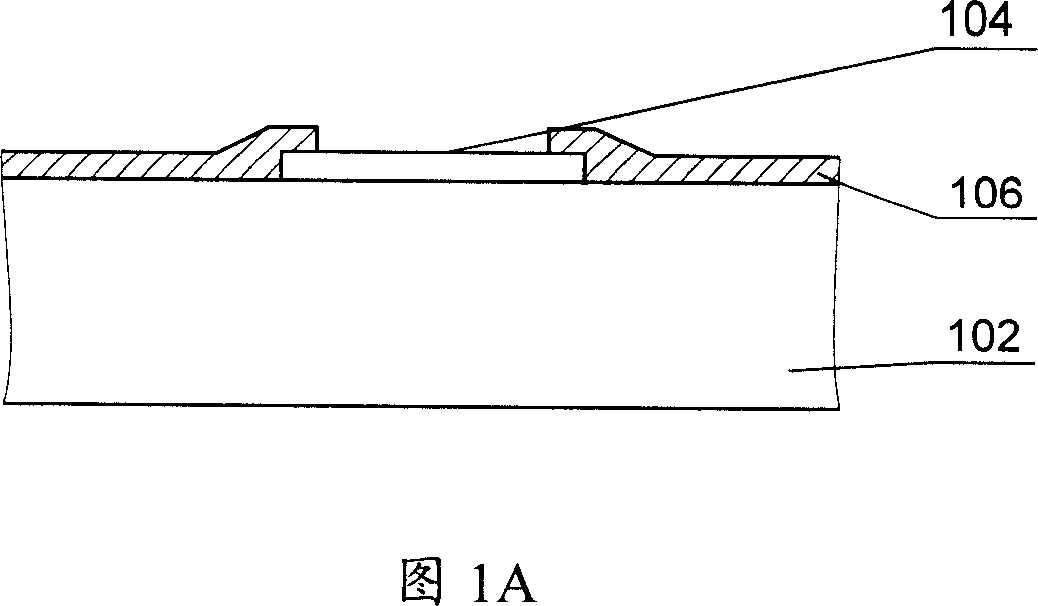

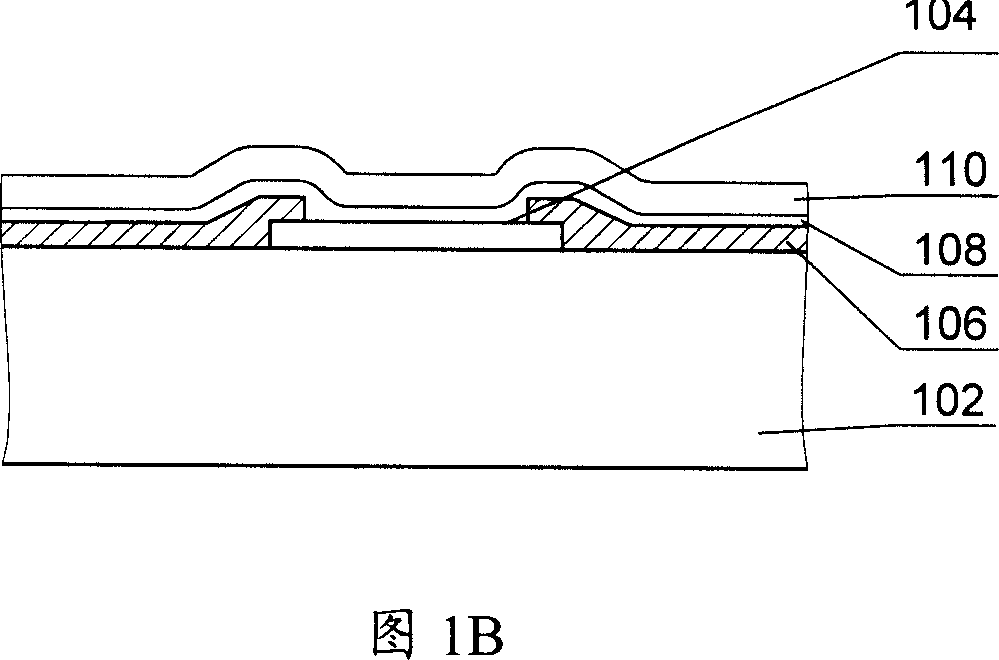

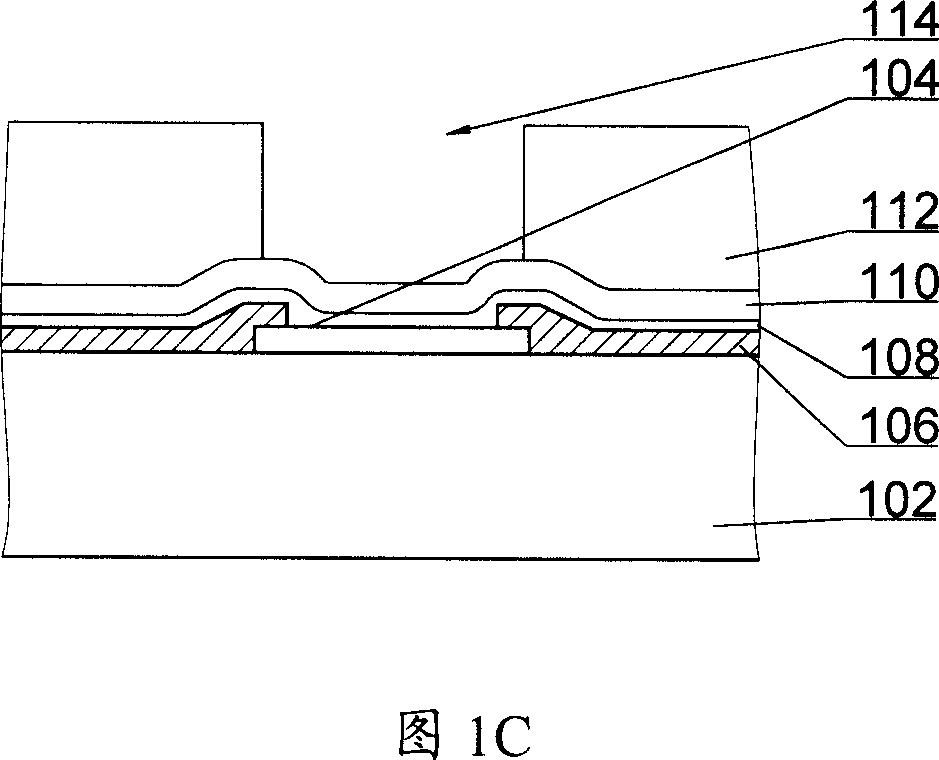

[0055] The solder bump structure of the semiconductor wafer and the manufacturing method thereof of the present invention planarize the bonding pad (ie pad) and the passivation layer through chemical mechanical polishing (CMP), so that the UBM layer formed thereon has a flat structure. The UBM layer structure adopts a hybrid laminated structure of a heat-resistant metal layer (refractory metal layer), a metal wetting layer (wetting layer), an adhesion layer and a barrier layer. Fig. 2 is a schematic diagram of the solder bump structure of the semiconductor wafer according to the present invention. As shown in FIG. 2, the solder bump structure of the present invention includes a pad 304 and a passivation layer 306 formed on a substrate 302. Preferably, the bottom layer of the pad 304 may have a stabilizing pad 303 to enhance the mechanical ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More