Low-density odd-even checking codec hardware simulation system based on programmable gate array

A low-density parity and hardware emulation technology, applied in the application of multi-bit parity error detection coding, error correction/detection using block codes, special data processing applications, etc., can solve the problem of rapid development of LDPC code research , time-consuming and other problems, to achieve the effect of shortening the simulation verification time, improving the noise quality, and speeding up the research process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

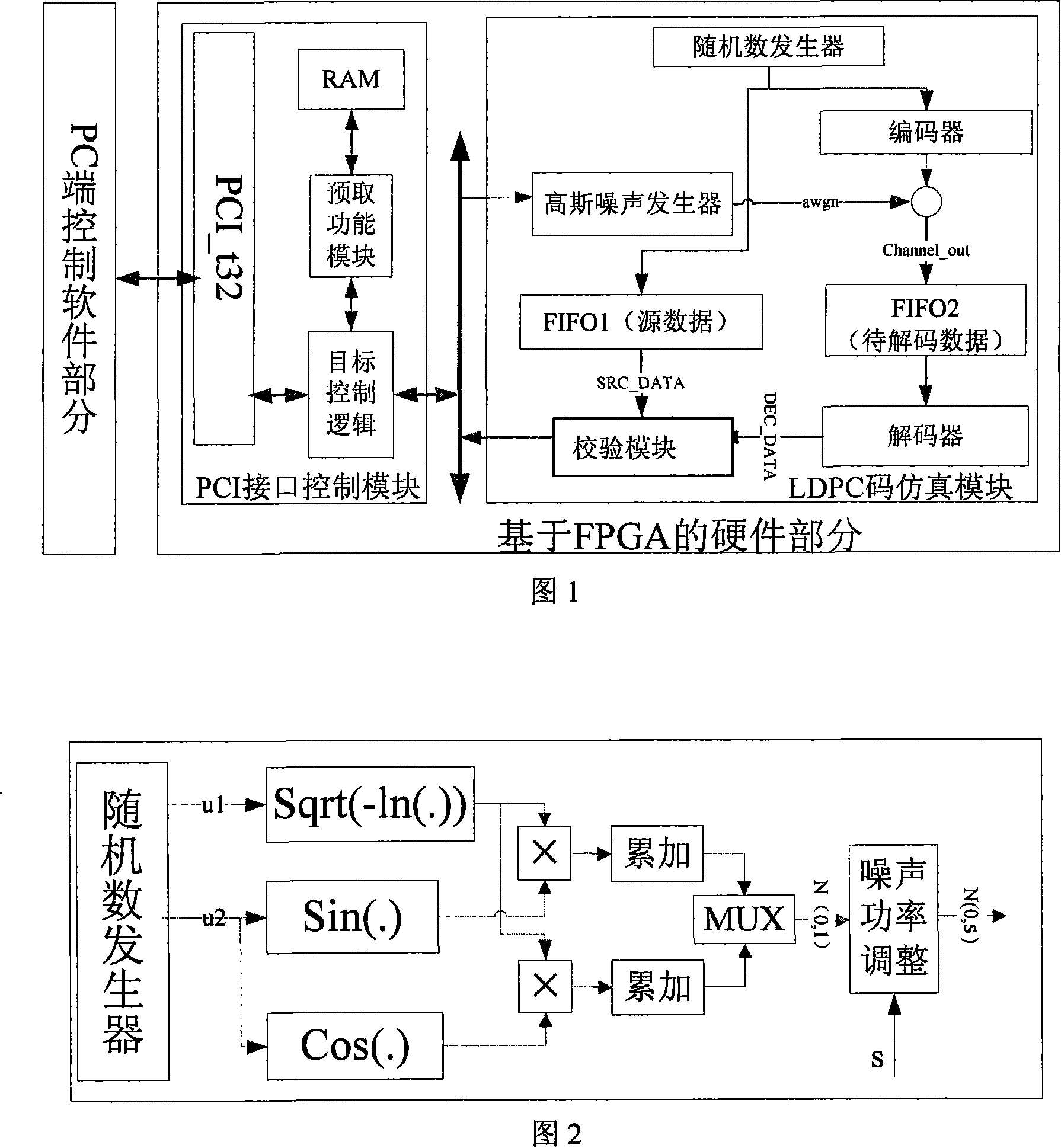

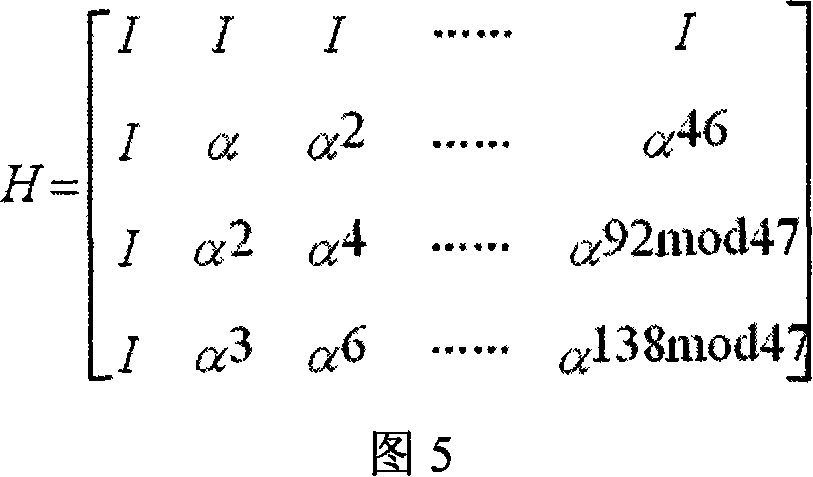

[0022] The present invention will be further described in detail below with reference to the accompanying drawings. In this embodiment, a (2209, 2021) Array LDPC code with code length N=2209 is selected, and the structure of the LDPC code is shown in FIG. 5 . where I is a 47×47 identity matrix, α i is the matrix formed after the identity matrix I is shifted by i bits.

[0023] The input clock of the simulation system is 100MHz, and two clocks of 120MHz and 40Hz are obtained through the processing of the digital phase-locked loop (DPLL) inside the FPGA. The entire FPGA hardware part except the decoder part works at 40MHz, and the other parts work at 120MHz.

[0024] 1 is a schematic structural diagram of an FPGA-based LDPC encoding / decoding hardware emulation system of the present invention, which includes a PC-side control software part and an FPGA-based hardware part. The FPGA hardware part includes PCI interface control module and LDPC code simulation module. The LDPC co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More