Chip embedding bury type packaging structure

A packaging structure and chip technology, applied in electrical components, electrical solid devices, circuits, etc., can solve the problems of chip cracking, ineffective heat dissipation, increased weight and cost, and achieve the effect of improving reliability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] Embodiments of the present invention are described below through specific specific examples, and those skilled in the art can easily understand other advantages and effects of the present invention from the content disclosed in this specification. The present invention can also be implemented or applied through other different specific embodiments, and various modifications and changes can be made to the details in this specification based on different viewpoints and applications without departing from the spirit of the present invention.

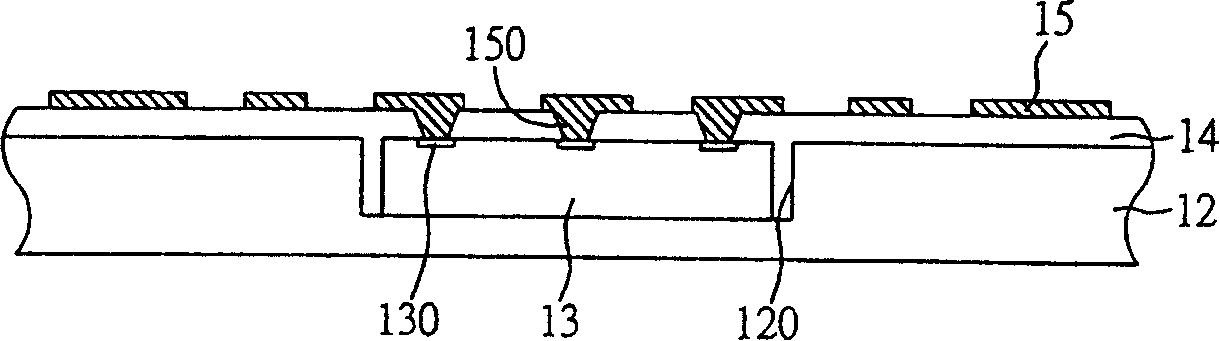

[0051] The chip-embedded package structure of the present invention is mainly characterized in that the carrier board has at least one raised portion for receiving a semiconductor chip. The protruding part is described in detail as an example, but it is not used to limit the present invention.

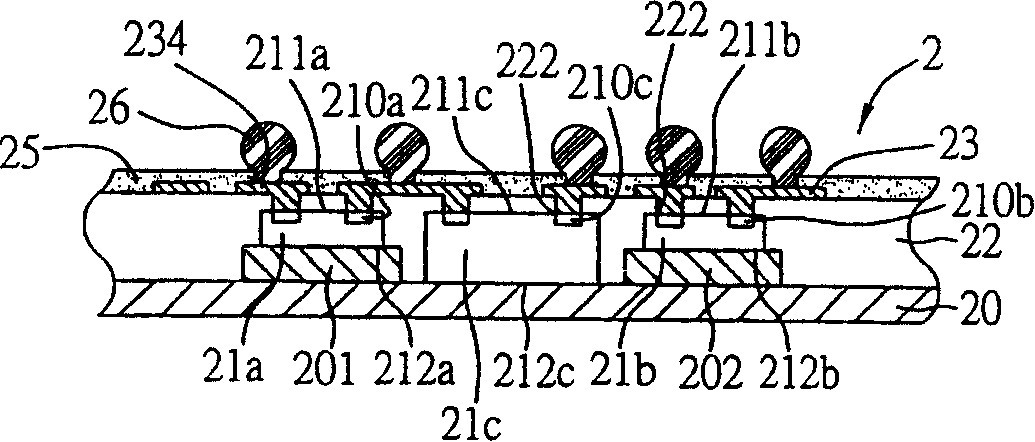

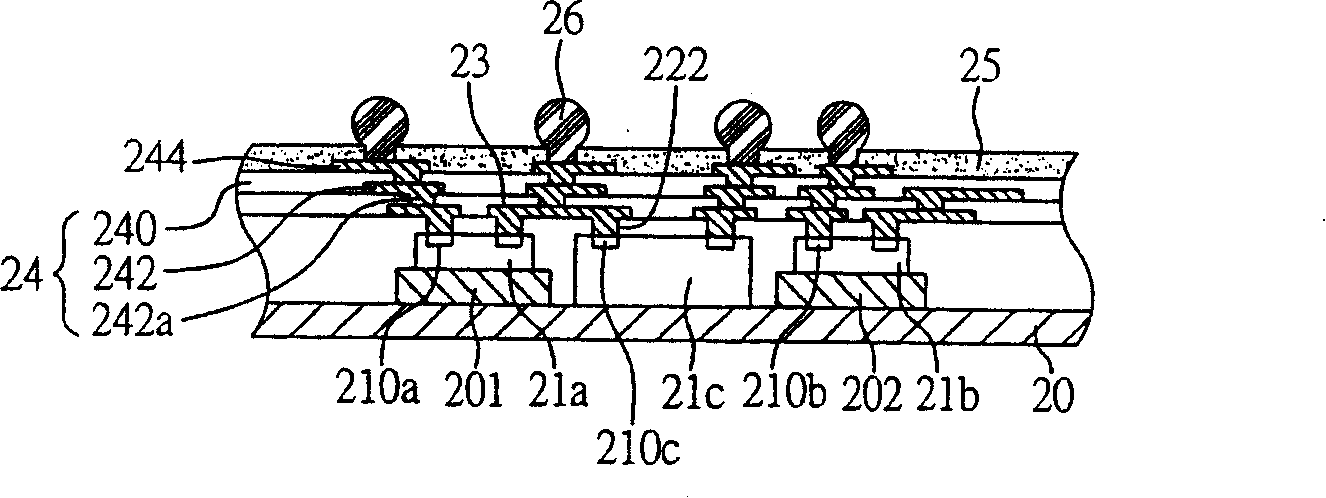

[0052] see Figure 2A , is a schematic cross-sectional view of a preferred embodiment of the chip-embedded package structure of the present...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More