Shallow impurity drain domain logical operation method suitable for active region read only memory

A read-only memory and logic operation technology, applied in the field of shallow-doped drain layout logic operation, can solve problems such as errors and inability to apply active area read-only memory, and achieve the effect of small layout area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

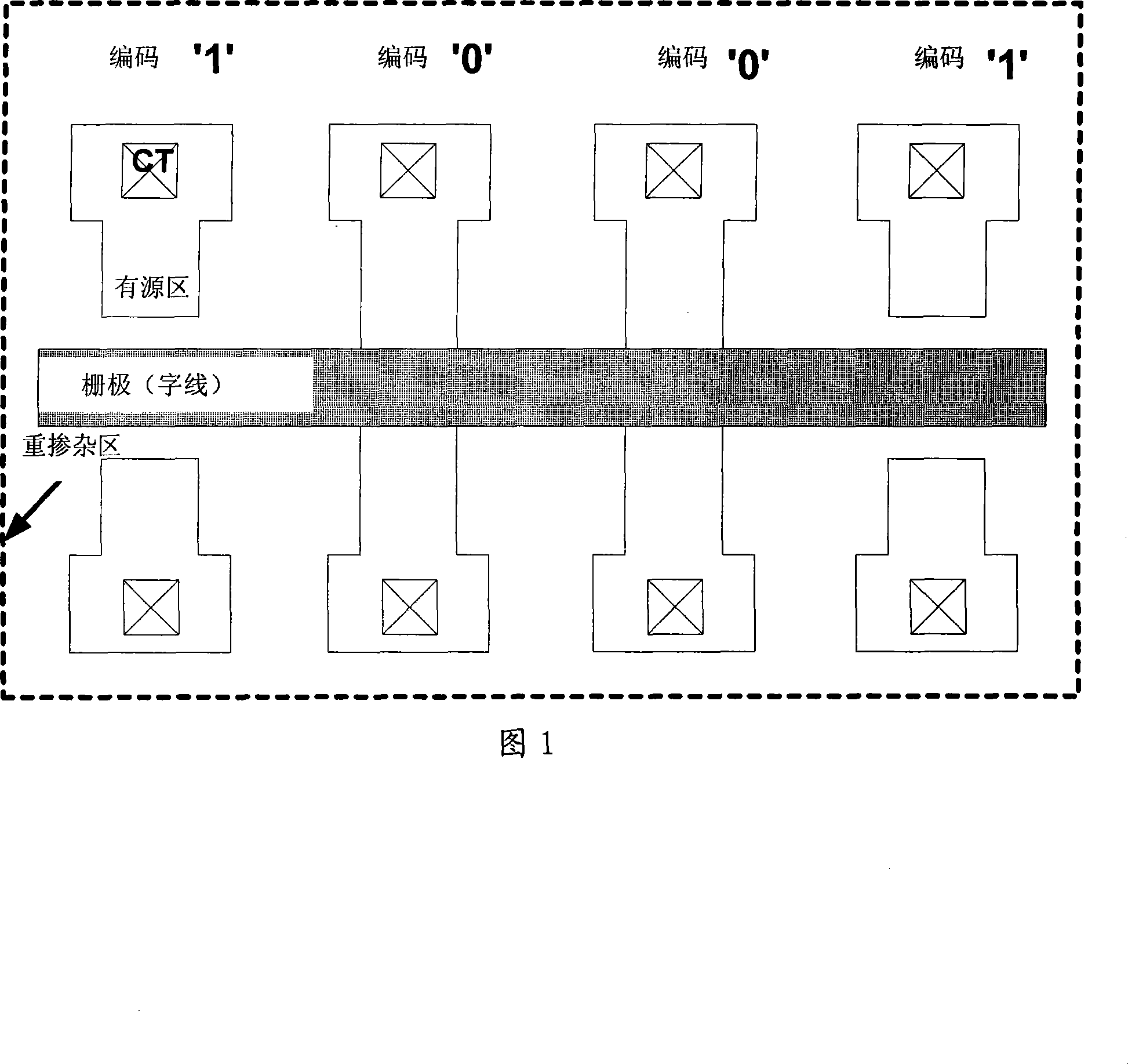

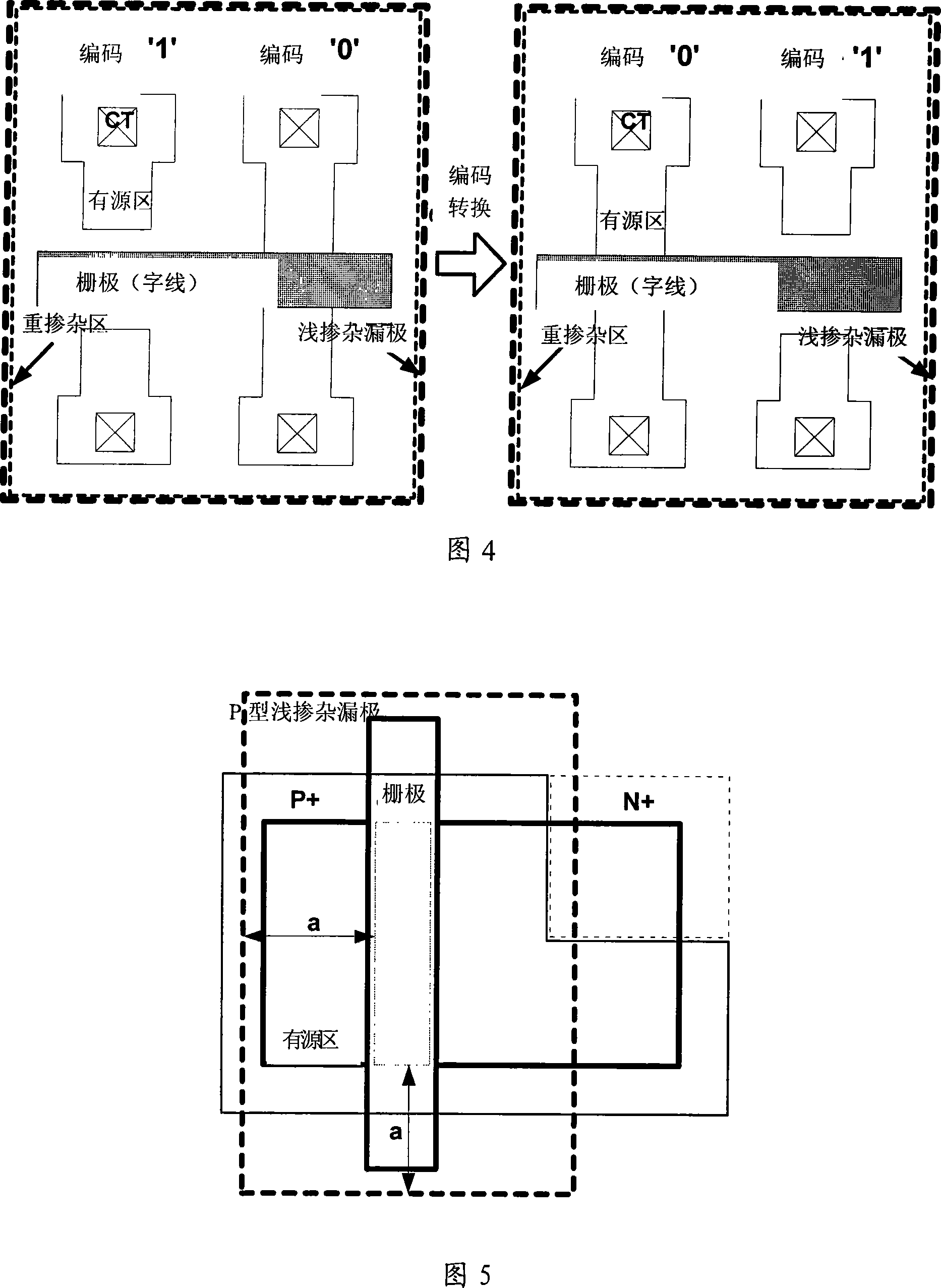

[0021] As shown in FIG. 7, the present invention provides a shallowly doped drain layout logic operation method suitable for active area read-only memory, comprising the following steps:

[0022] Step 1. Determine the boundary of the re-injection layer to obtain area A;

[0023] Step 2, determining the channel region of the Metal Oxide Semiconductor (MOS) transistor where the grid gate overlaps with the active region;

[0024] Step 3. Increase a on each side of the area determined in step 2 to obtain area B, where a can be adjusted according to the specific process capability. In some 0.15 micron logic processes, the range of a value can be selected to be 0.3-0.5um;

[0025] Step 4. Collect the two areas A and B respectively obtained in Step 1 and Step 3 to obtain Area C;

[0026] Step 5. In the region C determined in step 4, perform ion implantation to generate LDD.

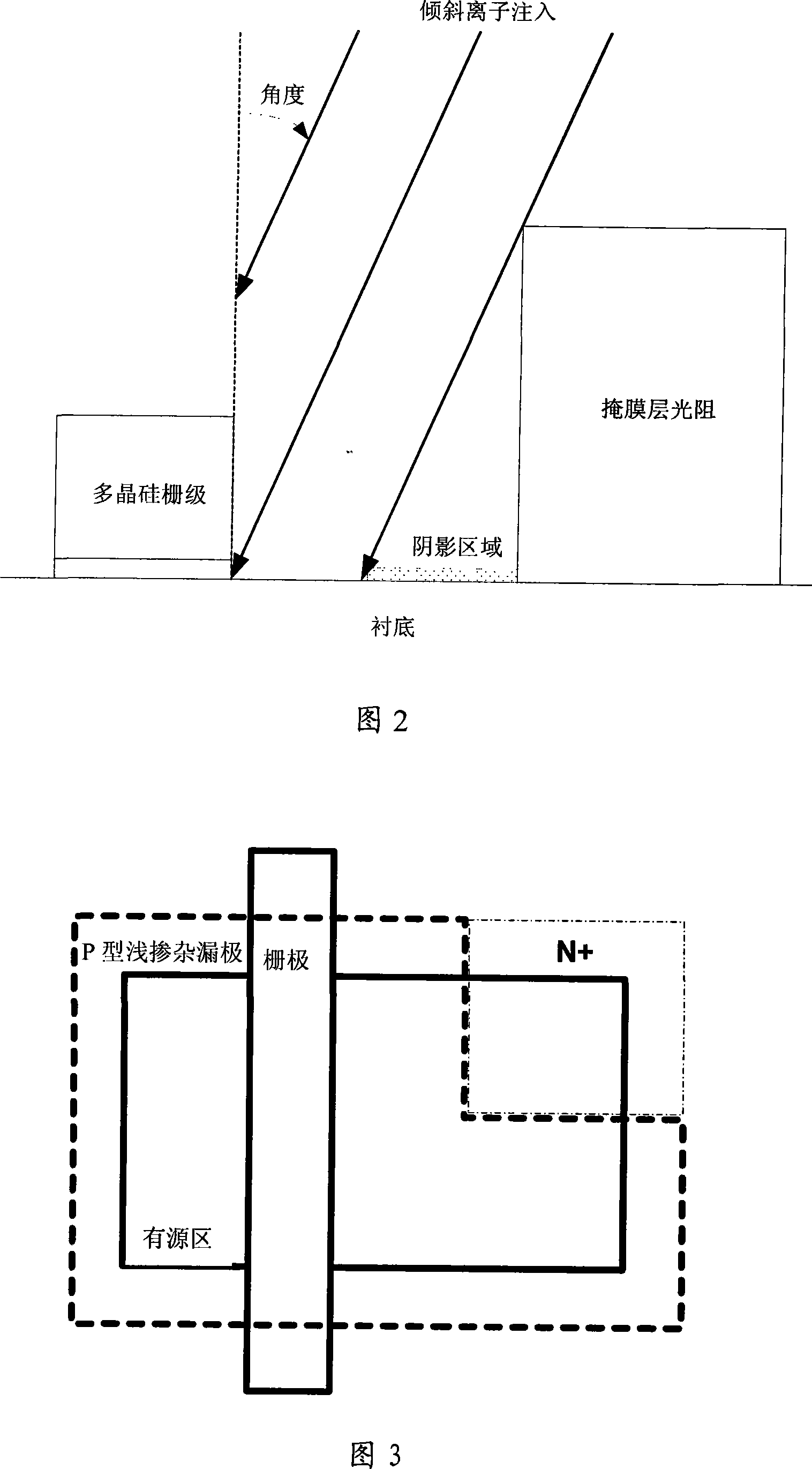

[0027] The N-type or P-type LDD layer (NLDD / PLDDlayer) produced by the logic process provided by the presen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com