HVMOS and semiconductor device integrating HVMOS and CMOS

A semiconductor and conductor technology, applied in the field of semiconductor devices, can solve the problems of long channel, increased unit area, and high energy consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

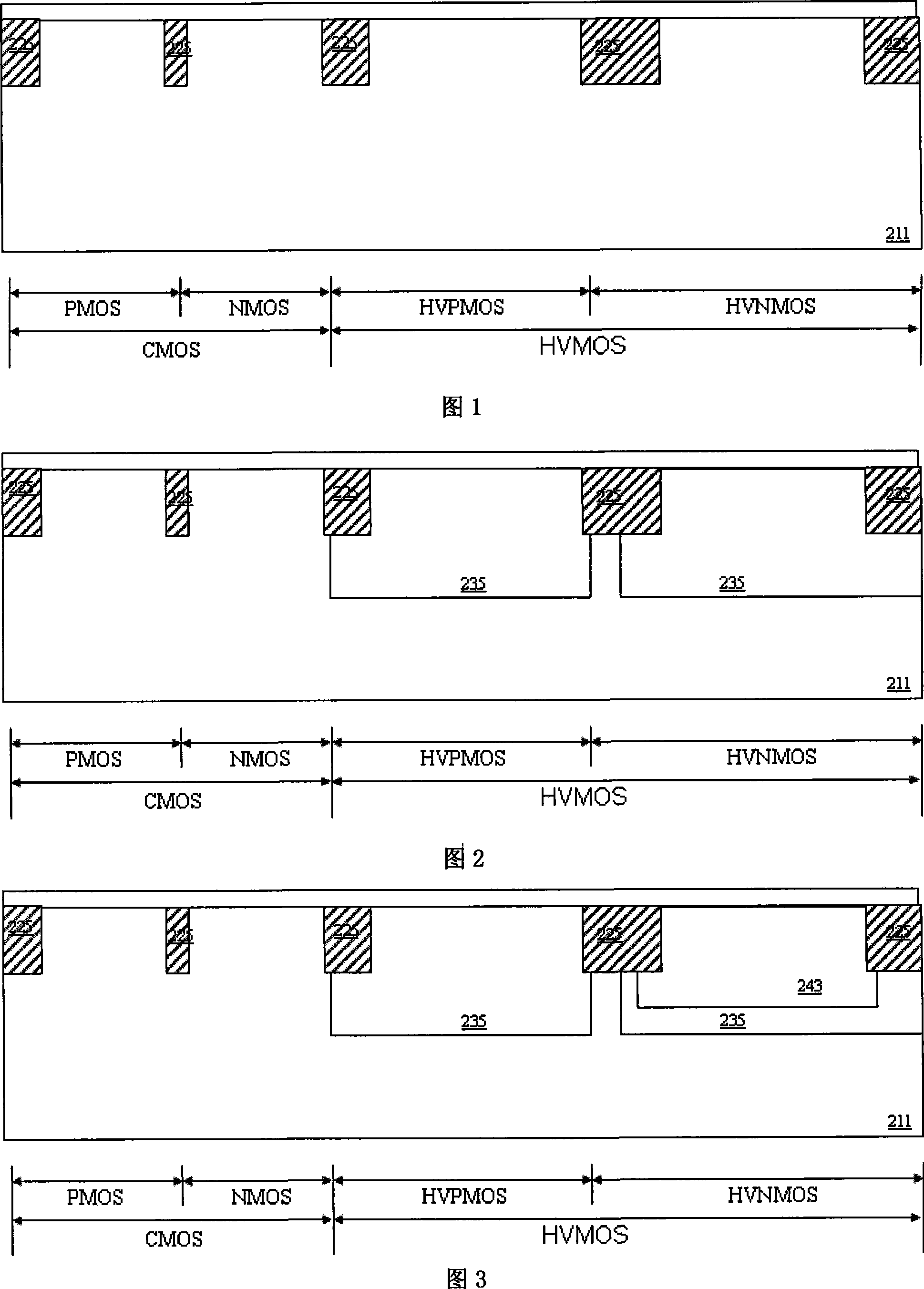

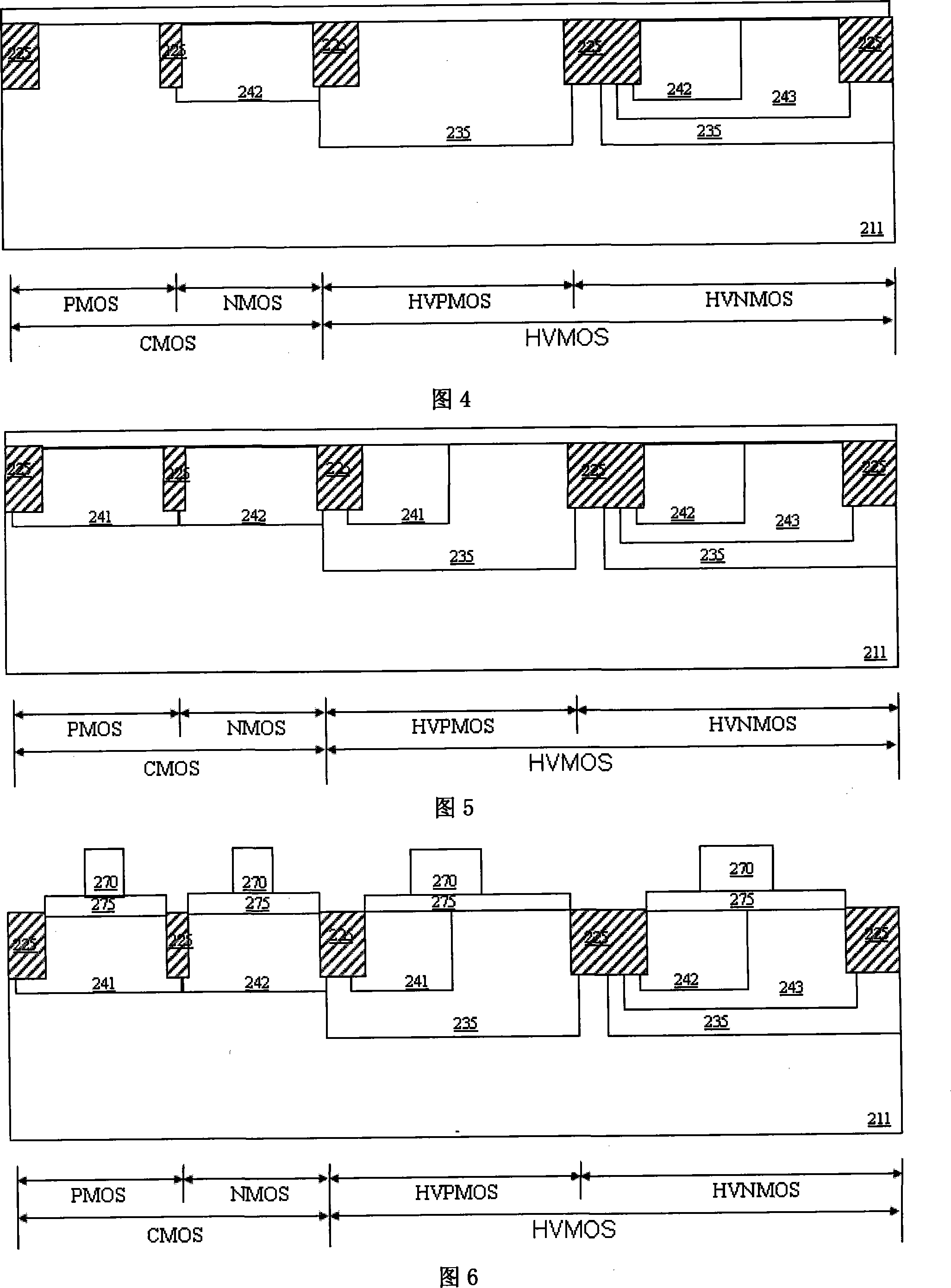

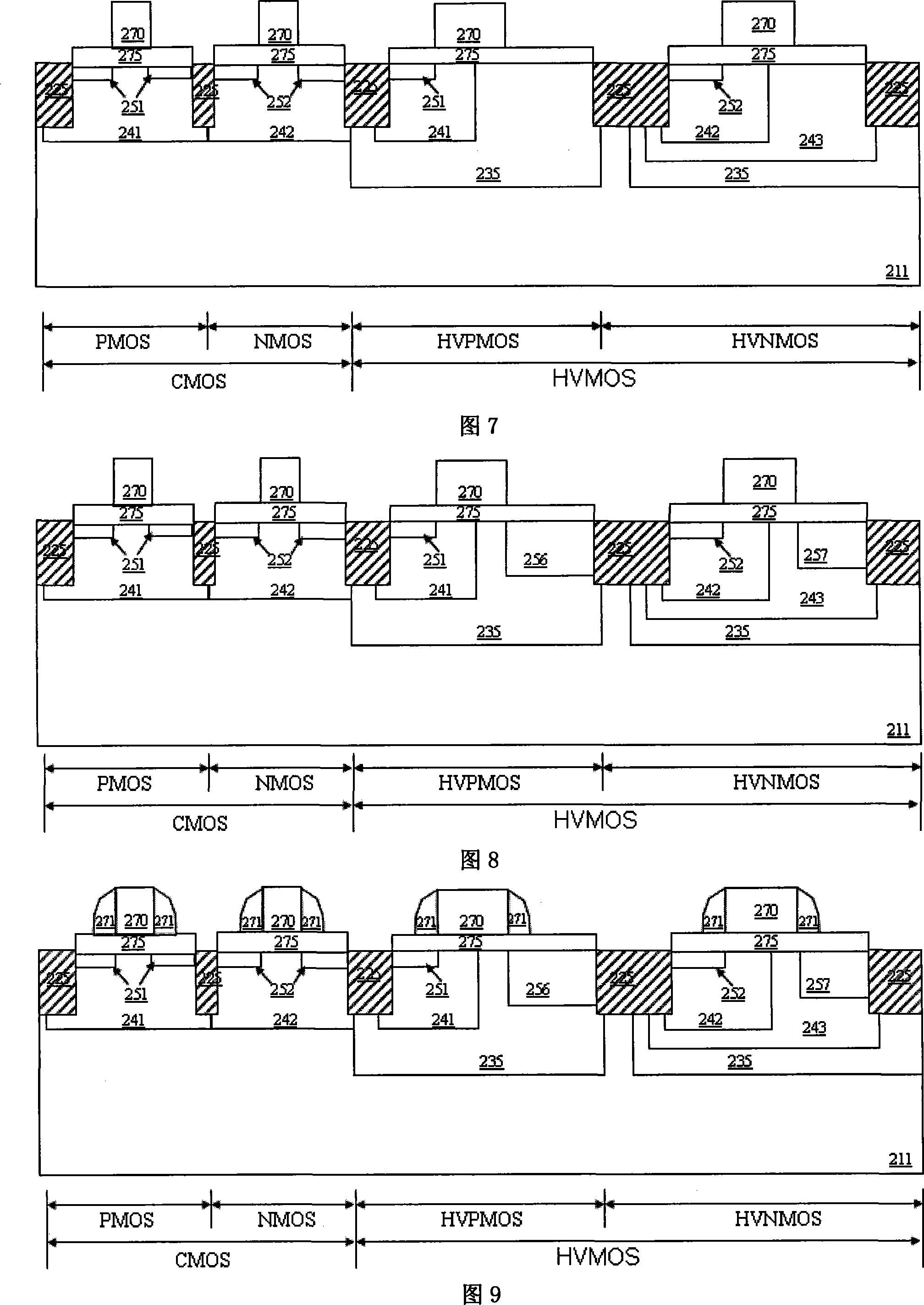

[0015] A kind of HVMOS as shown in Figure 14, can be either a HVPMOS or a HVNMOS, located on a semiconductor substrate / epitaxial layer 211, each of the HVPMOS and HVNMOS includes a channel located on the surface of the substrate / epitaxial layer 211, and a gate 270 on the channel. The HVPMOS also includes: a source / drain, the source / drain includes a lightly doped region 251 next to the channel and next to the channel and a lightly doped region 251 next to the channel heavily doped region 261; another source / drain, the other source / drain includes another lightly doped region 256 next to the channel and next to the channel and a next to the other A heavily doped region 261 of a lightly doped region 256, the other lightly doped region 256 is of the same doping type as the lightly doped region 251; A heterowell 241, the oppositely doped well 241 is located below the channel and does not completely contain the channel; another oppositely doped well 235 with the opposite doping type...

Embodiment 2

[0025] As shown in Figure 14, a semiconductor device integrating HVMOS and CMOS includes a CMOS and an HVMOS disposed on a semiconductor substrate / epitaxial layer 211, and the CMOS can be either an NMOS or a PMOS, or both Both are included, the HVMOS can be either a HVNMOS or a HVPMOS, or both can be included. It is characterized in that the PMOS and the NMOS respectively include:

[0026] a channel on the surface of the substrate / epitaxial layer 211, a gate 270 on the channel,

[0027] a source / drain comprising a lightly doped region 251, 252 and heavily doped regions 261, 262 adjacent to the lightly doped region 251, 252,

[0028] A counter-doped well 241, 242 of opposite doping type to the source / drain.

[0029] It is also characterized in that the HVPMOS and the HVNMOS respectively include:

[0030] a channel on the surface of the substrate / epitaxial layer 211, a gate 270 on the channel,

[0031] A source / drain comprising a lightly doped region 251, 252 next to the cha...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More