Singlechip adopting RISC structure

A single-chip, arithmetic logic unit technology, applied in machine execution devices, concurrent instruction execution, etc., can solve problems such as unfavorable compatibility and popularization, inability to use program resources, and difficulty in improving running speed, reducing redundant cycles, high-speed A large amount of data circulation, cost-effective effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] CISC is to use the least machine language instructions to complete the required computing tasks. For example, for multiplication, on a CPU with a CISC architecture, such an instruction may be required: MUL A, B; you can multiply the numbers in A and B and store the result in A. The operations of reading the data in A and B into registers, multiplying them and writing the results back to memory all rely on the logic designed in the CPU to achieve.

[0033] The RISC architecture requires software to specify the individual steps of operation. If the above example is to be implemented on the RISC architecture, the operations of reading the data in the address ADDRA and ADDRB into the register, multiplying and writing the result back to the memory must be implemented by software, for example: MOV A, ADDRA; MOV B, ADDRB;MUL A,B;STR ADDRA,A.

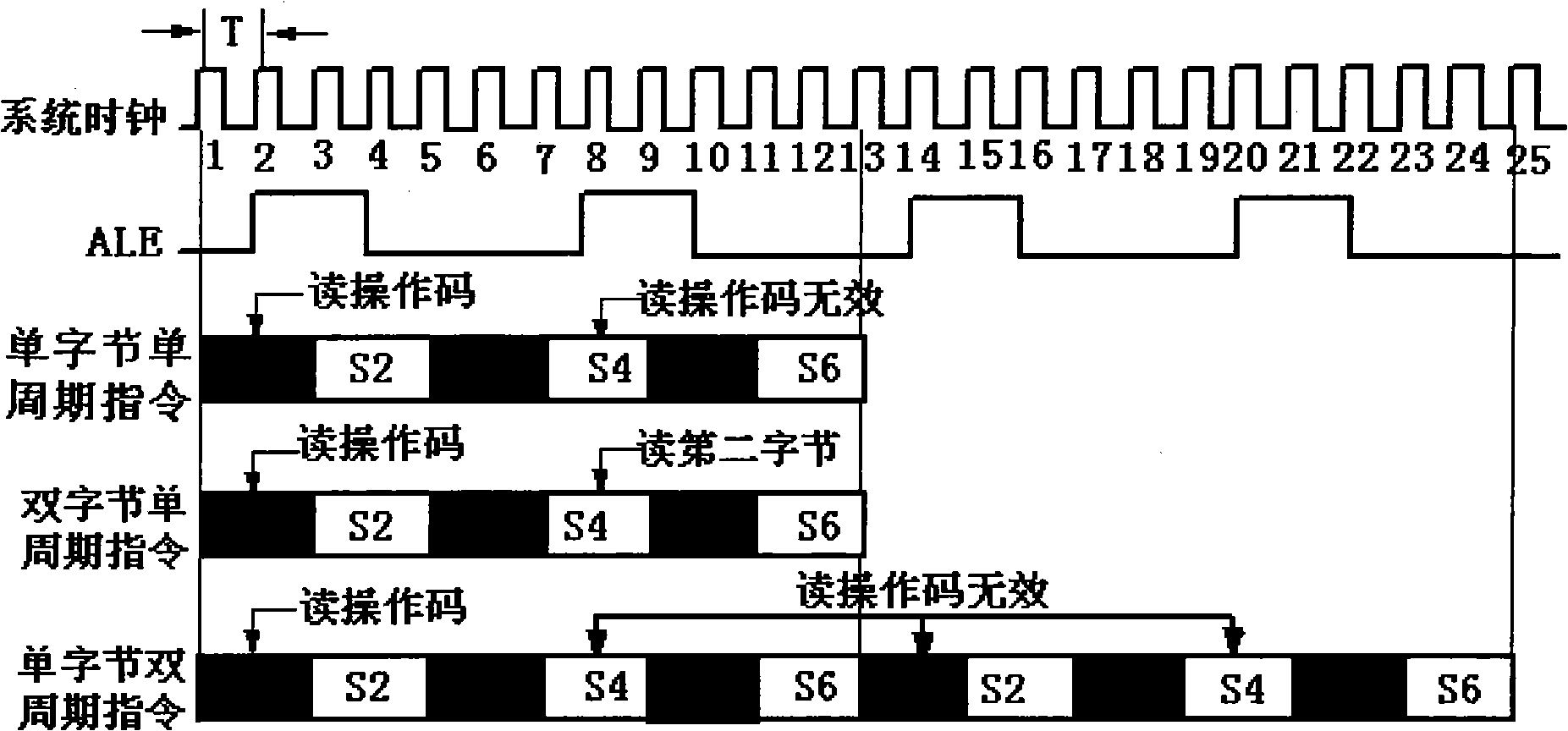

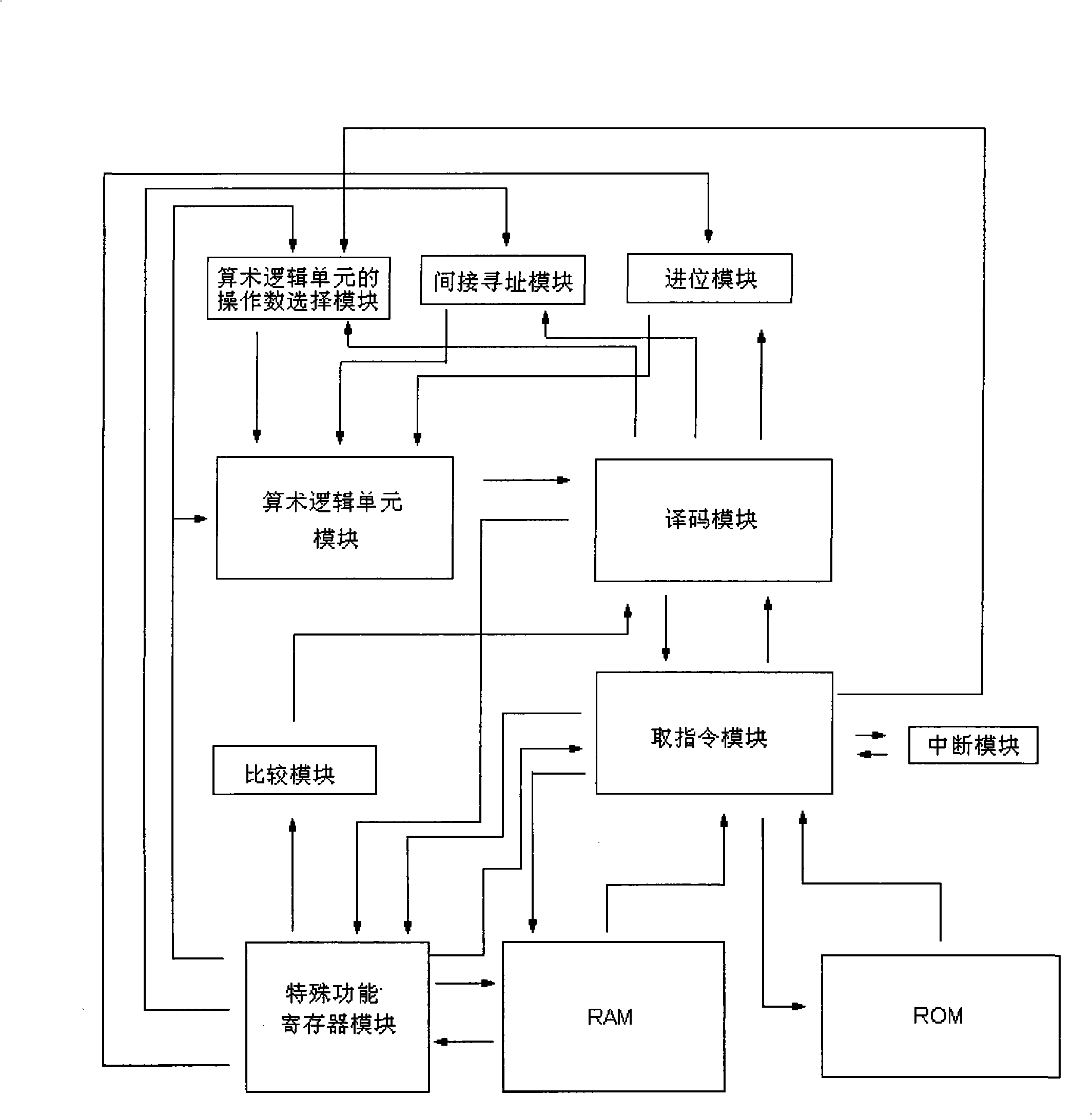

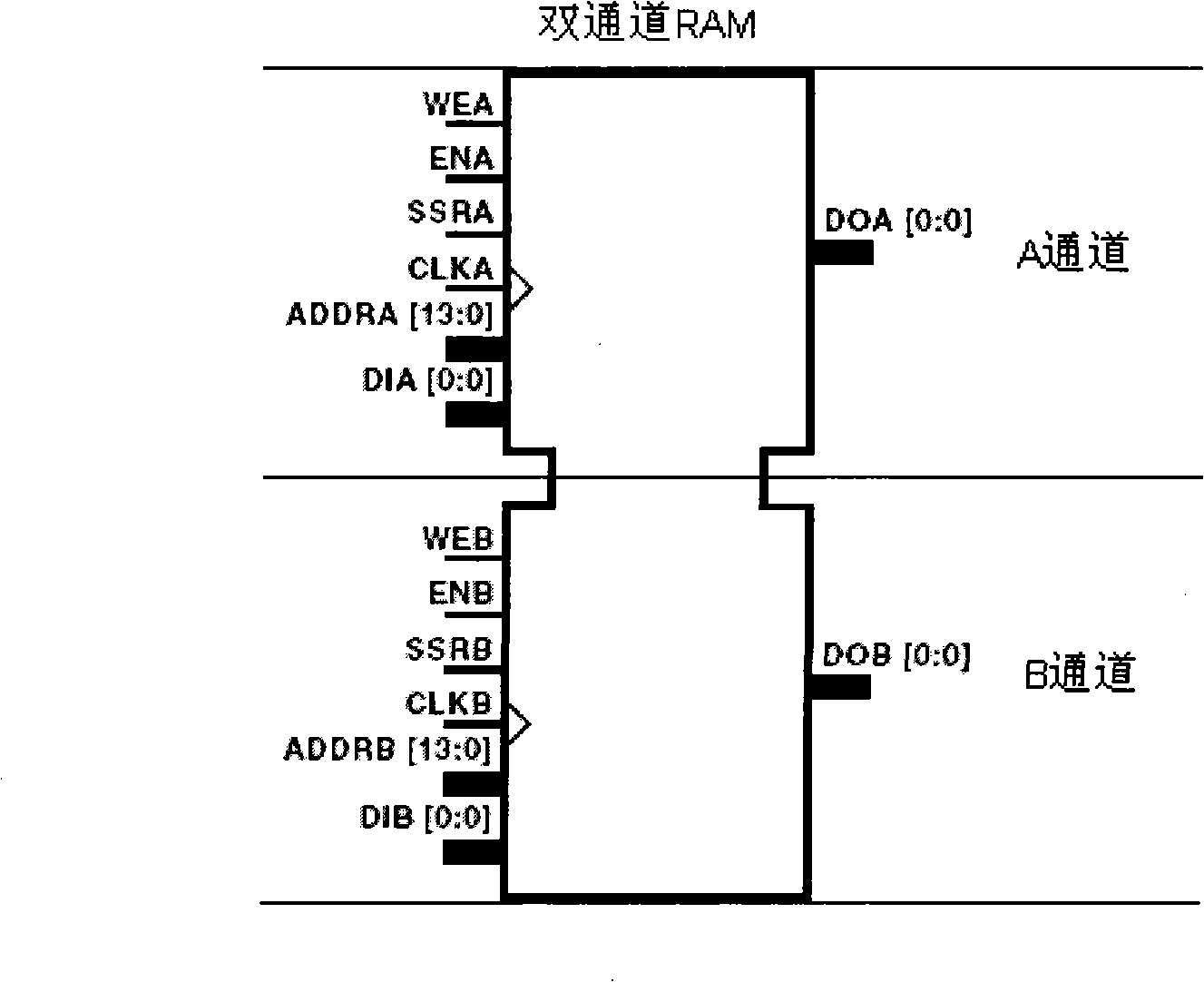

[0034] In the embodiment of the present invention, the single-chip microcomputer uses a new kernel scheme, under the constant situati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More