Multi-layer substrate and manufacturing method thereof

A technology of multi-layer substrate and manufacturing method, which is applied in the direction of multi-layer circuit manufacturing, printed circuits connected with non-printed electrical components, printed circuit components, etc., can solve problems affecting the yield and reliability of flip-chip packaging, etc. Achieve the effect of improving yield rate and reliability, and good flatness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

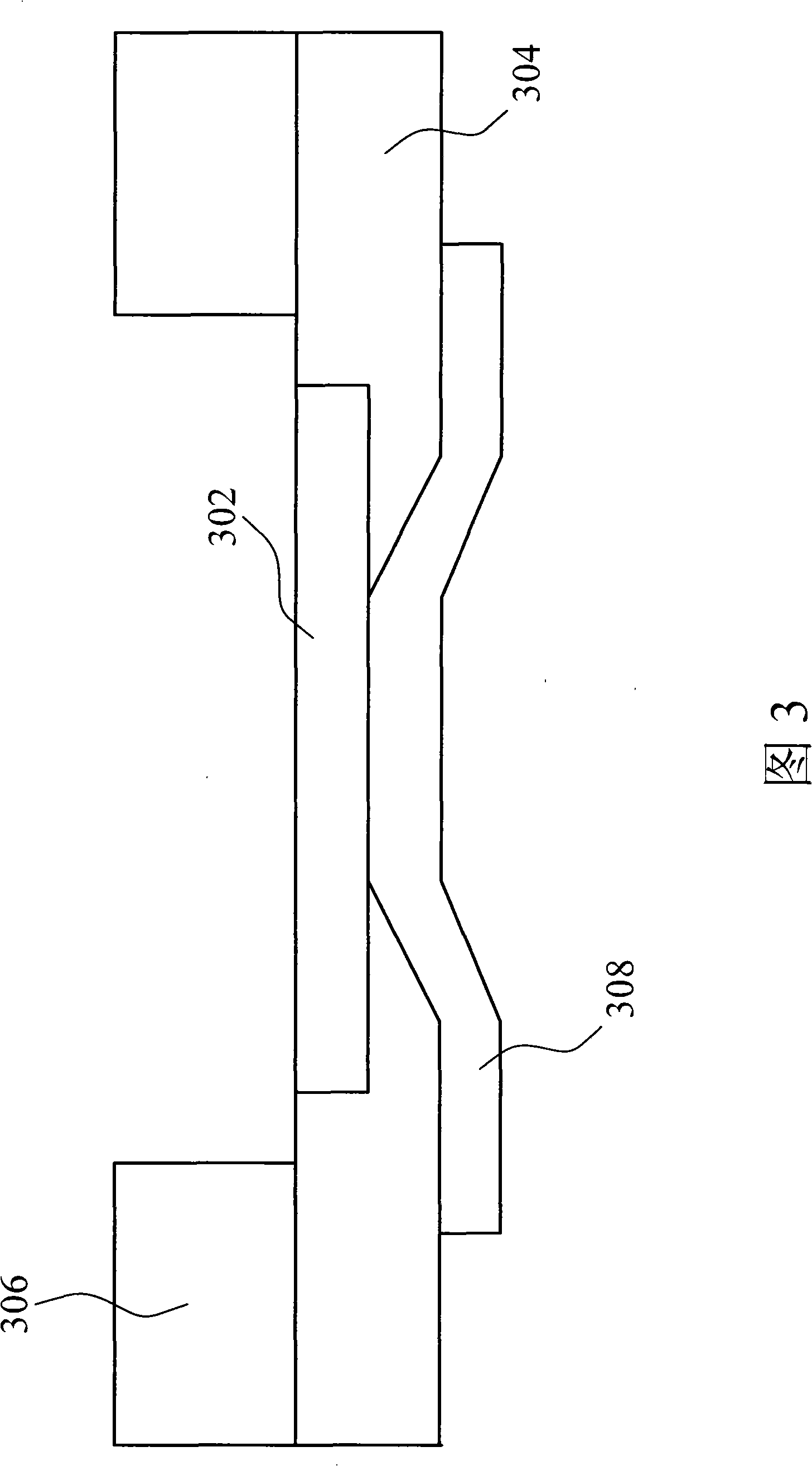

[0023] Please refer to FIG. 3 , which is a simple schematic diagram of the surface of the multilayer substrate of the present invention. The multilayer substrate of the present invention includes at least one pad layer 302 and one surface dielectric layer 304 . Moreover, the multi-layer substrate may further include a solder resist layer 306 . Below the pad layer 302 is a metal circuit layer 308 of the multi-layer substrate. The pad layer 302 of the present invention is embedded in the surface dielectric layer 304 , and the sides of the pad layer 302 are in close contact with the surface dielectric layer 304 , which can enhance the adhesion strength between the two. Furthermore, the surface of the pad layer 302 and the surface of the surface dielectric layer 304 have a coplanarity, so that the surface of the multilayer substrate of the present invention has high flatness, that is, the surface of the pad layer 302 and the surface of the surface dielectric layer 304 There is n...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More