Integrated semiconductor light emitting device and method for manufacturing same

A technology for light-emitting devices and semiconductors, which is applied in the manufacture of semiconductor/solid-state devices, semiconductor devices, and electric solid-state devices, etc., can solve the problems of overall aging of the device, low current injection efficiency of light-emitting devices, etc., and achieves improved integration density, sufficient heat dissipation, The effect of excellent reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0812] Examples are given below to describe the features of the present invention more specifically. The materials, usage amounts, proportions, treatment contents, treatment procedures and the like shown in the following examples can be appropriately changed within the scope not departing from the gist of the present invention. Therefore, the interpretation of the scope of the present invention should not be limited to the specific examples shown below. In addition, in the drawings referred to in the following embodiments, there are parts whose dimensions are changed to facilitate understanding of the structure, and the actual dimensions are as follows.

[0813] "

Embodiment A-1

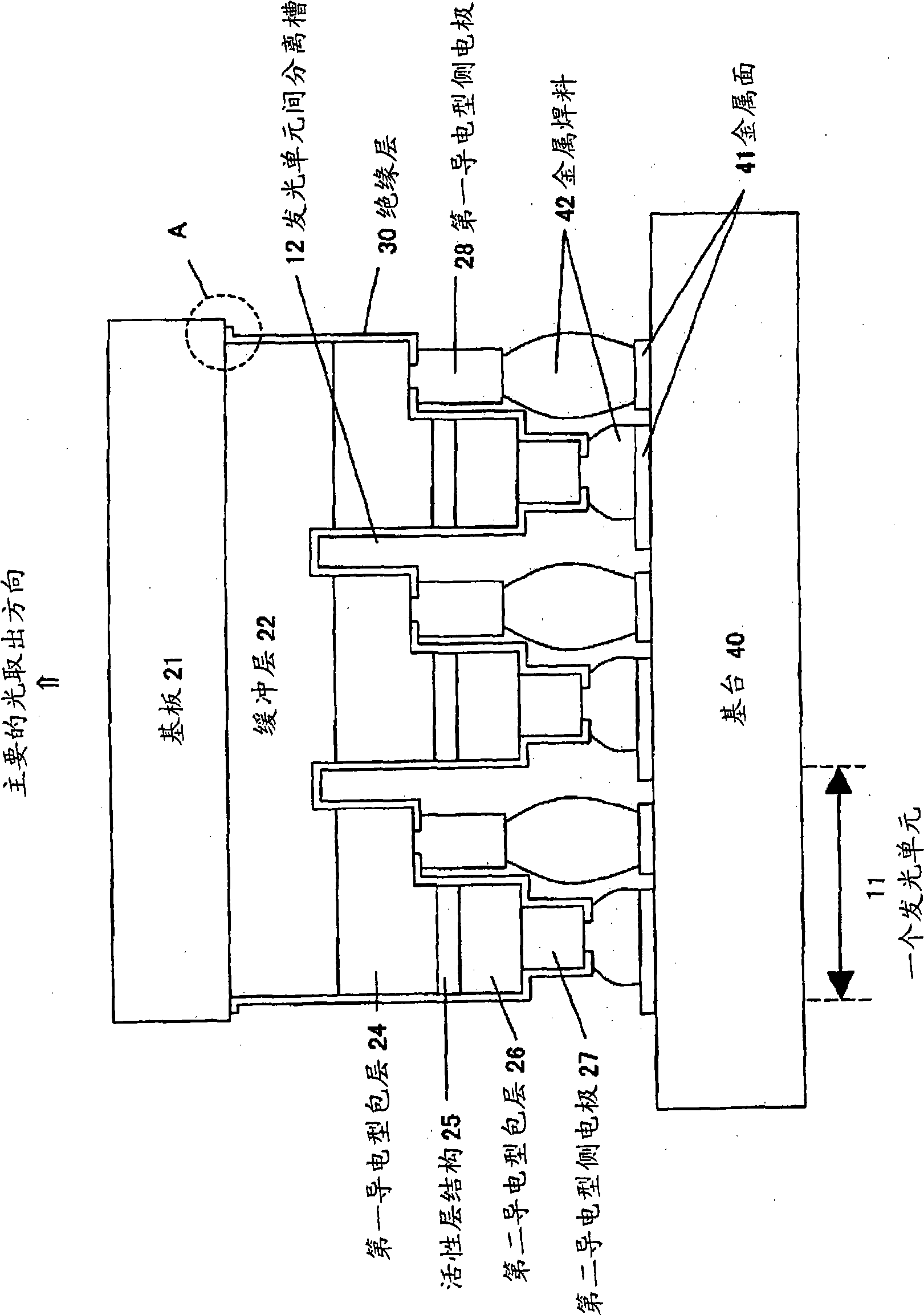

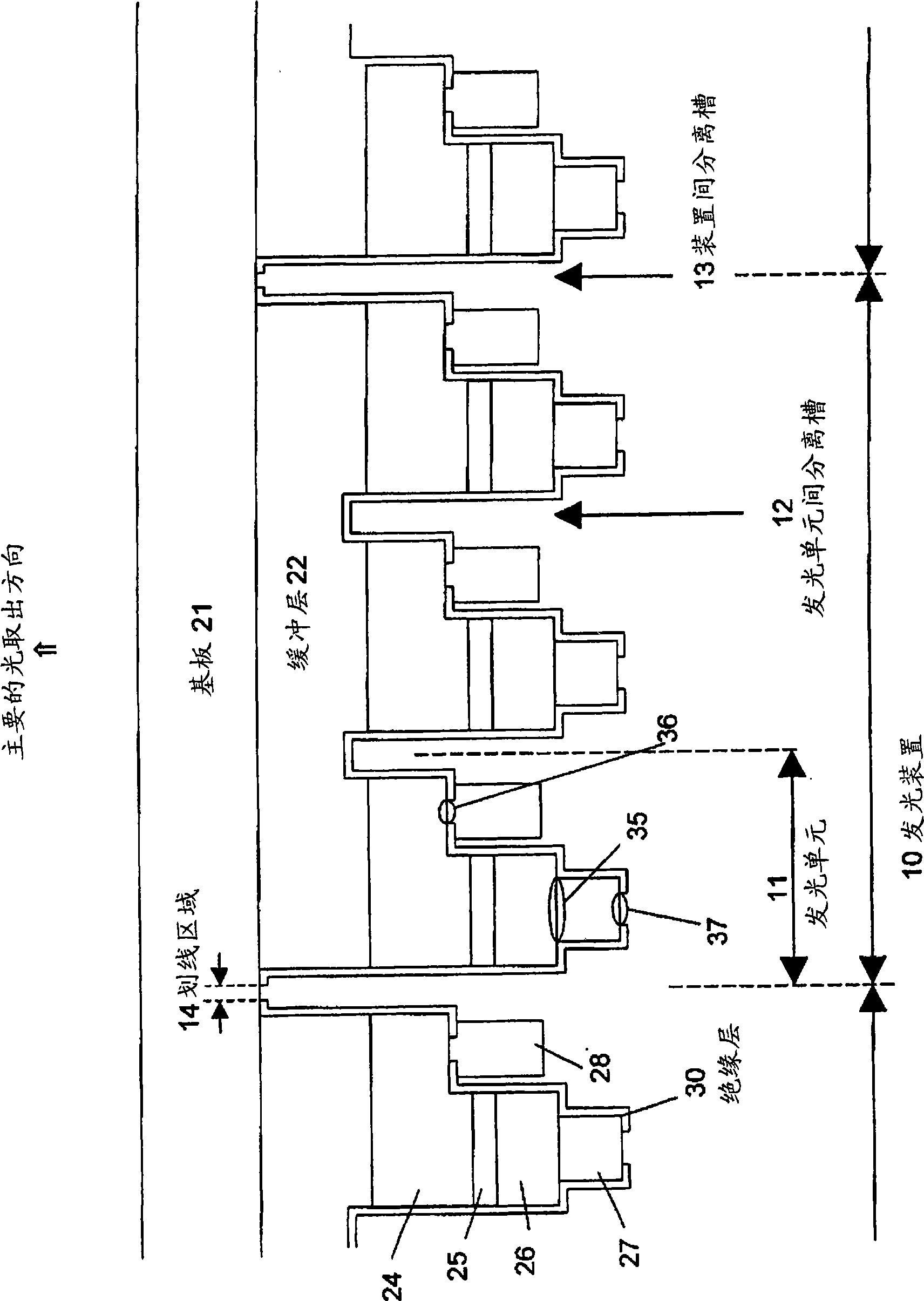

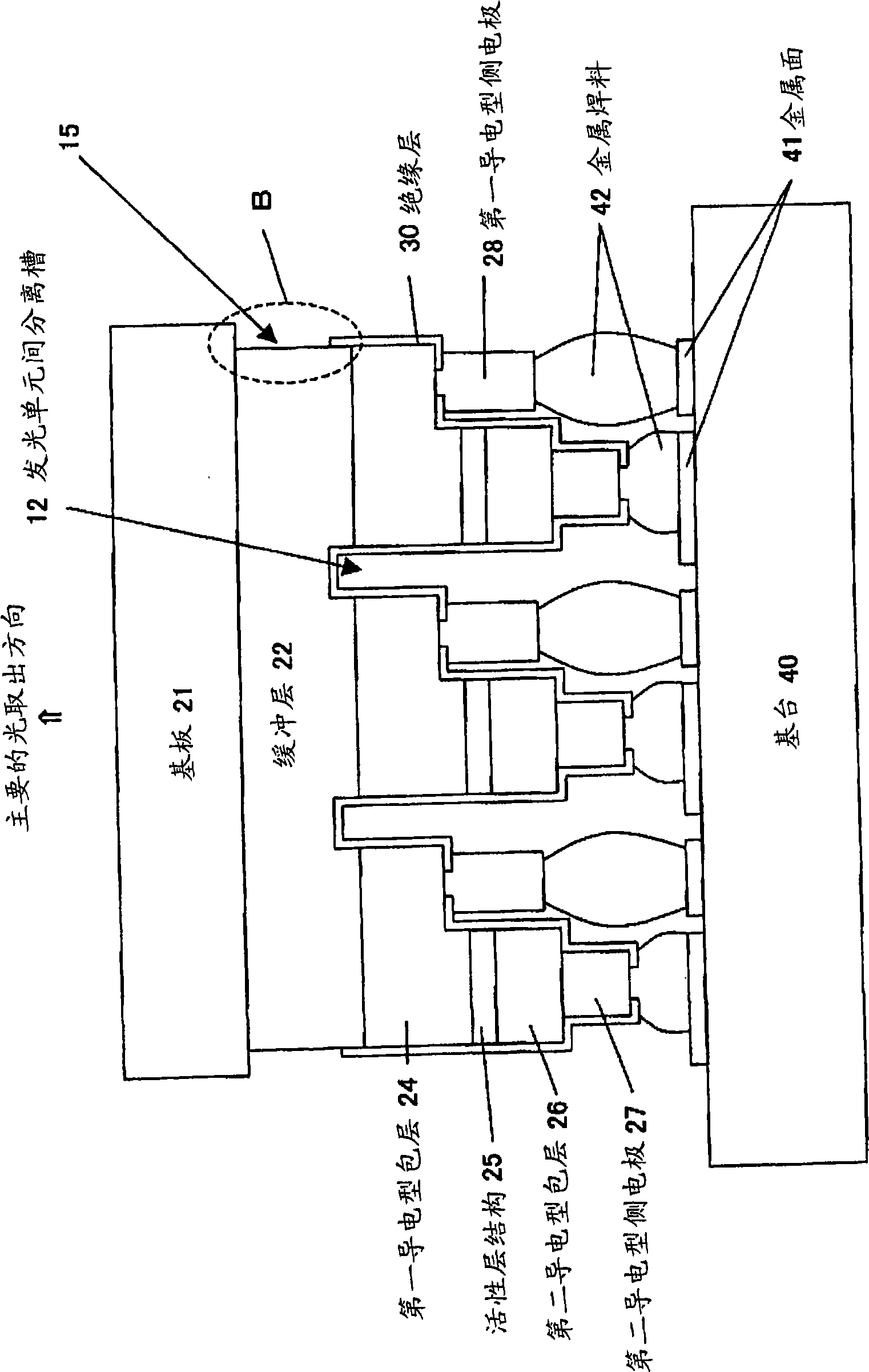

[0815] Make in the following order Figure 1-15 The semiconductor light-emitting device shown. Relevant process diagram reference Figure 1-6 ~ 10, 12 and 14.

[0816] Prepare a c+ plane sapphire substrate 21 with a thickness of 430 μm. First, a 10 nm thick undoped GaN layer grown at a low temperature is formed on it by MOCVD as the first buffer layer 22a, and then a 4 μm thick undoped GaN layer is formed at 1040° C. The doped GaN layer serves as the second buffer layer 22b.

[0817] Further, Si doping (Si concentration 1×10 18 cm -3 ) GaN layer as the first conductivity type (n-type) second cladding layer 24b, with Si doping (Si concentration 3×10 18 cm -3 ) GaN layer as the first conductivity type (n-type) contact layer 24c, and further Si-doped (Si concentration 1.5×10 18 cm -3 ) Al 0.15 Ga 0.85 The N layer serves as the first conductivity type (n-type) first cladding layer 24a. Next, as the active layer structure 25, a barrier layer and a quantum well layer were...

Embodiment A-2

[0837] As in Example A-1, wherein the film formation of the thin-film crystal layer after the buffer layer 22 was formed was performed as follows, and Example A-1 was repeated. That is, in Example A-1, after forming undoped GaN with a thickness of 4 μm as the second buffer layer 22 b at 1040° C., Si doping (Si concentration 5×10 18 cm -3 ) GaN layer as the first conductivity type (n-type) second cladding layer 24b, with Si doping (Si concentration 8×10 18 cm -3 ) GaN layer as the first conductivity type (n-type) contact layer 24c, and further Si-doped (Si concentration 5.0×10 18 cm -3 ) Al 0.10 Ga 0.90 The N layer serves as the first conductivity type (n-type) first cladding layer 24a. Next, barrier layers and quantum well layers are alternately formed to form an active layer structure 25, wherein the barrier layer is an undoped GaN layer formed at 850°C with a thickness of 13nm, and the quantum well layer is formed at 720°C with a thickness of 2nm undoped In 0.1 Ga 0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More