Dynamic boundary scanning chain test method based on programmable devices

A technology of boundary scan and link test, applied in the field of electronic circuit test and boundary scan test of printed circuit assembly board, can solve the problems of increasing the cost of components and printed boards, and achieve the goal of reducing costs and layout expenses Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

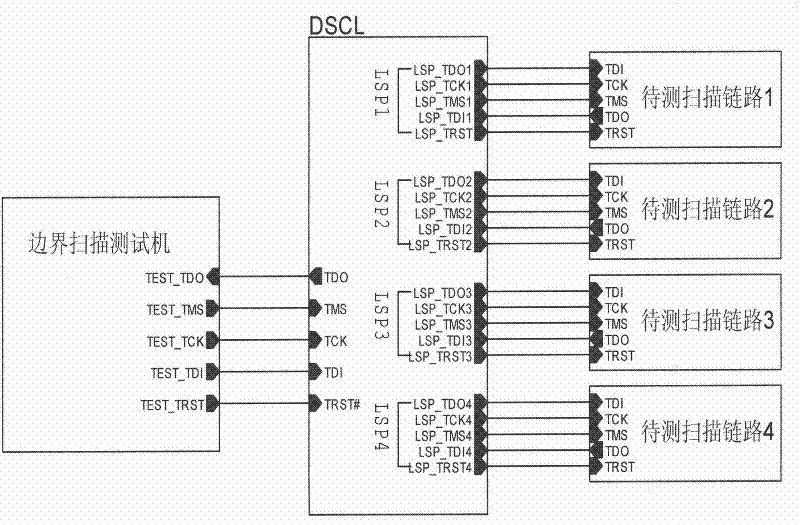

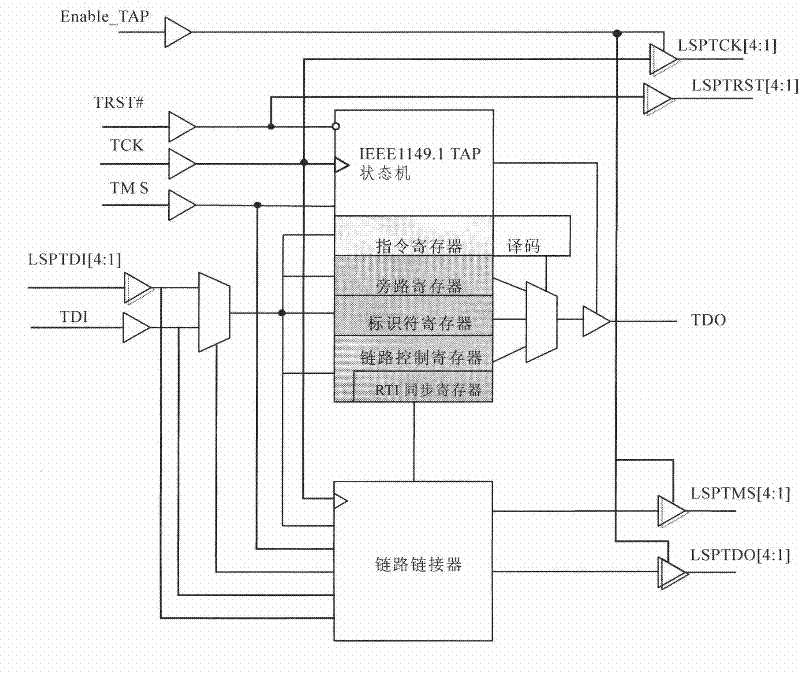

[0032] The present invention proposes a kind of dynamic, boundary-scan link test method based on PLD, FPGA device, has designed a kind of dynamic boundary-scan link linker (DSCL, DynamicScan Chain Linker), adopts HDL RIL code to DSCL It can be instantiated into a PLD or FPGA programmable device, especially it can be directly instantiated into a programmable device with surplus internal and IO resources on the assembly board to be tested, so as to realize multiple boundary scan chains during boundary scan testing The dynamic loading and unloading of the circuit, so as to test the boundary scan circuit flexibly. The so-called instantiation refers to the use of HDL RIL codes to describe the scan link linker (DSCL) through logic synthesis (synthesis), layout and routing (place & route) into target PLD / FPGA technology library logic units and connections, And finally generate a programming file and upload it to the programmable device.

[0033] Such as figure 1 As shown, the bound...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More