Packaging method used for high-power integrated circuit

An integrated circuit and packaging method technology, applied in the field of semiconductor packaging manufacturing, can solve the problems of poor heat dissipation, affecting heat dissipation, and large thermal resistance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The packaging process for high-power integrated circuits adopts metal base embedded metal substrate packaging, and the specific implementation methods are as follows:

[0030] 1. Drill a hole on the metal substrate with a size slightly smaller than the metal base,

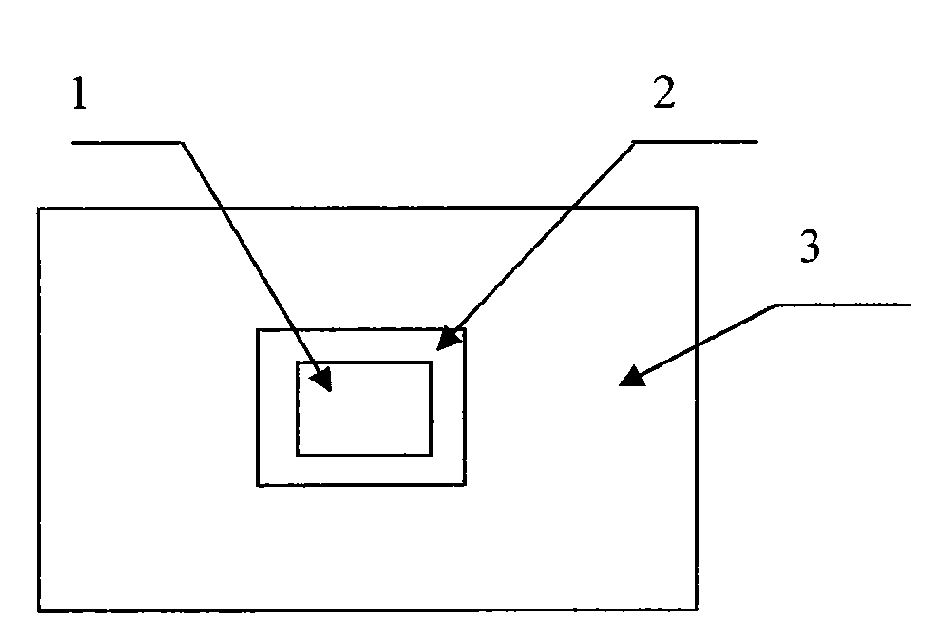

[0031] 2. Embed the metal base into the metal substrate,

[0032] 3. Print solder paste on metal base and metal substrate,

[0033] 4. Install the chip and lead pins on the metal base and metal substrate respectively,

[0034] 5. Put the chip, lead pins, metal base and metal substrate together in a sintering furnace for sintering at a temperature of 210°C~230°C.

[0035] 6. The chip and the lead pin are bonded by wire,

[0036] 7. Check under the microscope whether there is detachment or missing bonding,

[0037] 8. Coat the surface of the chip with glue,

[0038] 9. Seal the case, cover the metal substrate with a case,

[0039] 10. Cut the ribs and bend the leads,

[0040] 11. Test open and short cir...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More