High-speed multi-channel clock data recovery circuit

A clock data recovery, high-speed clock technology, applied in electrical components, pulse technology, automatic power control, etc., can solve problems such as narrow tuning range, inappropriate multi-phase signal high-speed transmission, etc., to achieve wide adaptability and programmable capability strong effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] In order to better understand the present invention, the present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

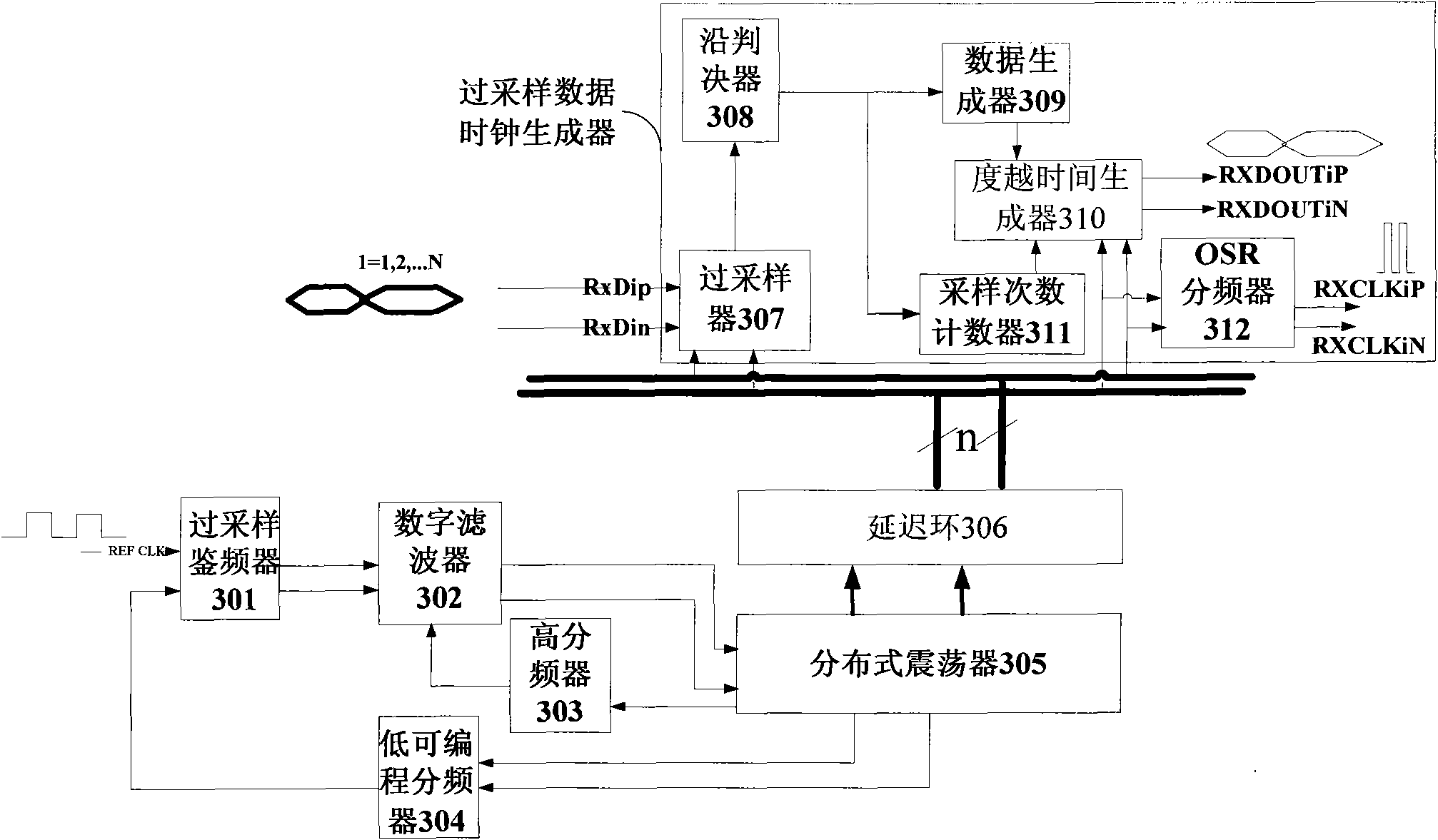

[0041] see image 3 , the high-speed multi-channel clock data recovery circuit of the present invention comprises oversampling discriminator 301, digital filter 302, distributed oscillator (DOSC) 305, low programmable frequency divider 304, high frequency divider 303 and n(n is a natural number) oversampled data clock generators. Wherein, the distributed oscillator 305 is a fully differential distributed oscillator; each oversampled data clock generator includes a delay loop 306, an oversampler 307, an edge decider 308, a data generator 309, a sampling frequency counter 311, a over time generator 310 and OSR divider 312 . see Figure 5 , the delay loop 306 includes a phase detector filter 3060 and a first delay 3061 , a second delay 3062 , a third delay 3063 , . . . , an nth delay 30...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More