Lamination type piezoresistor network and making method thereof

A varistor and chip technology, used in varistor, resistor manufacturing, resistors, etc., can solve the problems of unfavorable equipment miniaturization, low component installation efficiency, and large occupied area, so as to reduce the cost of the whole machine and improve the Installation density and efficiency, the effect of solving performance deterioration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

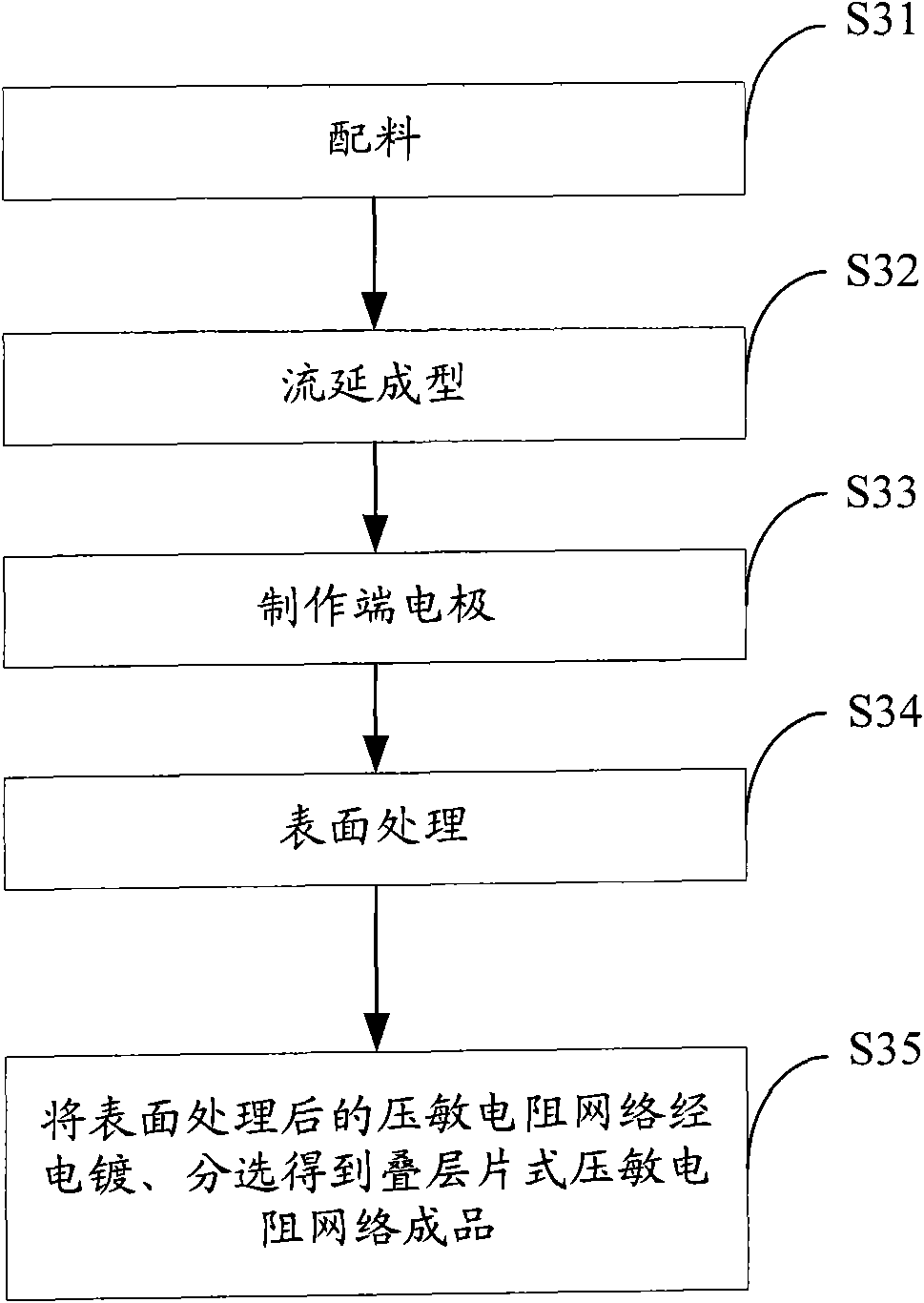

[0026] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

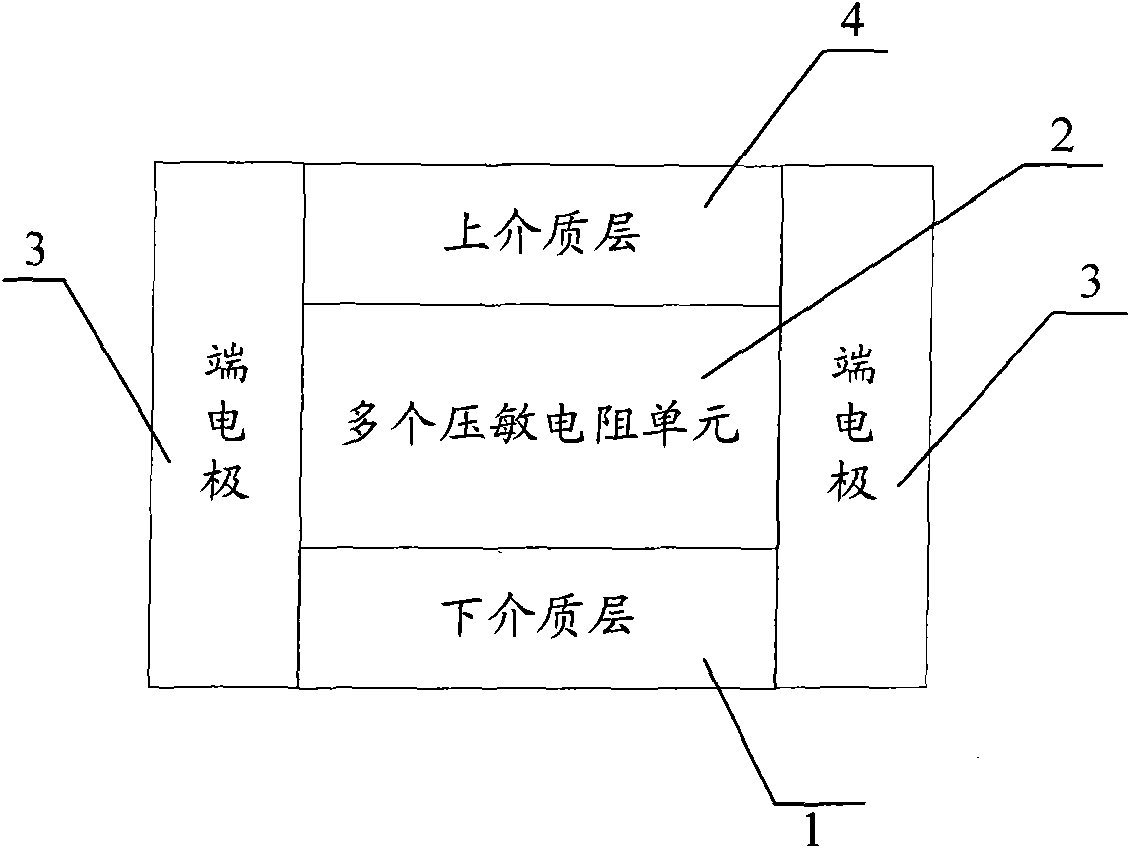

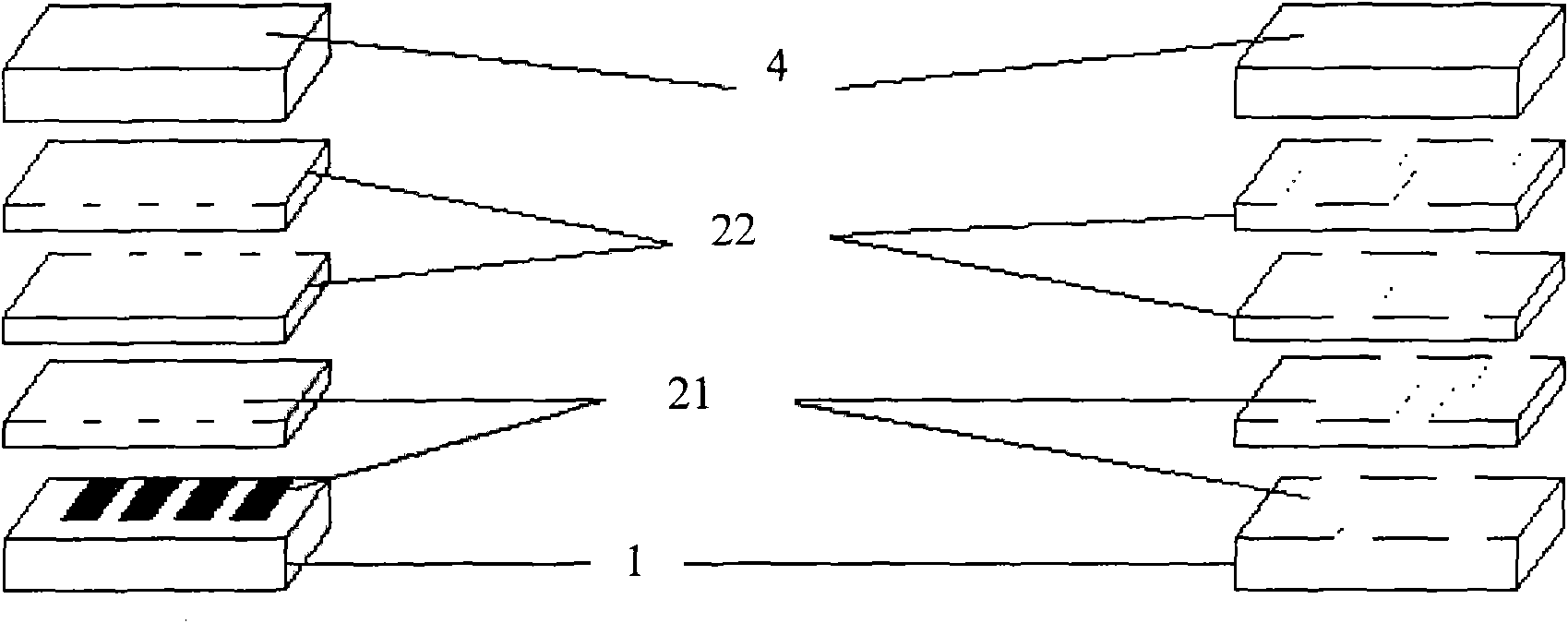

[0027] The multilayer chip varistor network provided by the embodiment of the present invention integrates a plurality of discrete varistor units, which is convenient to use in multi-line overvoltage protection, improves the component installation density and efficiency, and reduces the cost of the whole machine , to achieve miniaturization.

[0028] The multilayer chip varistor network provided by the embodiment of the present invention can be applied to the efficient installation of electronic equipment such as mobile communications, PDAs, and computers in multi-line overvoltage protection circui...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More