Method for preparing ultra-shallow junction on surface of semiconductor chip through laser

A semiconductor, N-type semiconductor technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of doping lateral and vertical diffusion, PN junction size limitations, complex processes, etc., to simplify the process, save Annealing process, the effect of shortening the process time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

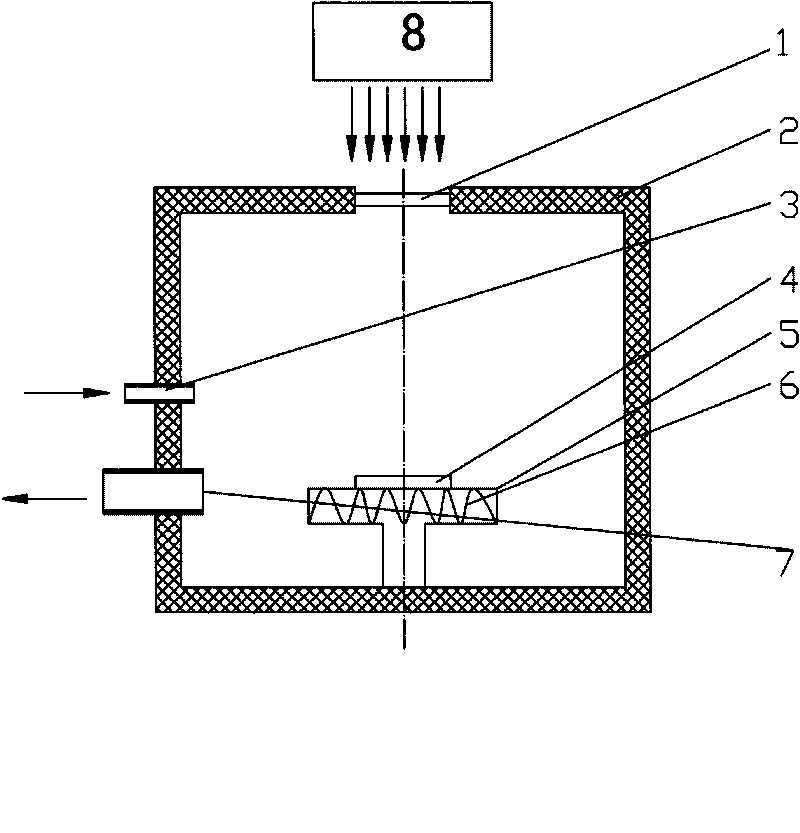

Embodiment 1

[0030] Using the N-type single crystal silicon of 156mm×156mm×180 μm as the substrate, the present invention is used to perform doping on the N-type semiconductor substrate to form an ultra-shallow junction, so as to further illustrate the present invention. The process steps are as follows: 1. Put the cleaned N-type silicon wafer on the slide table in the vacuum chamber, and the silicon wafer is facing the transparent glass window 1. 2. Close the vacuum chamber door, and evacuate the vacuum chamber to 3.0 ×10 -3 Pa, turn on the heater at the same time to heat the substrate, the heating temperature is 350°C. 3. When the vacuum degree reaches the background vacuum degree, the heating temperature is stabilized at 350°C for more than 10 minutes, and after the silicon wafer is evenly heated, the flow rate of 500 sccm is passed into the vacuum chamber. 2 h 6 and H 2 The mixed gas, where B 2 h 6 The percentage content is 5%. At the same time, adjust the pumping rate to keep th...

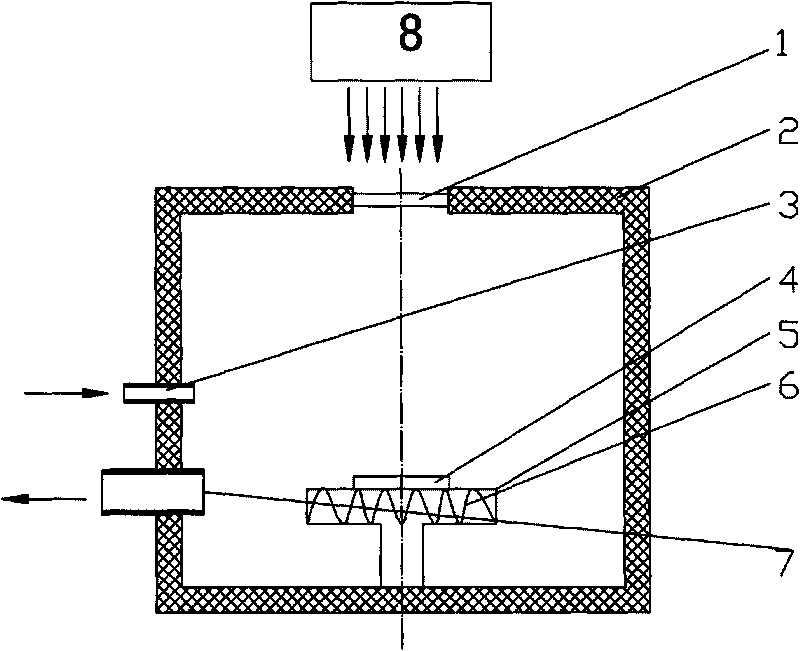

Embodiment 2

[0032] Using the P-type single crystal silicon of 156mm×156mm×180 μm as the substrate, the present invention is used to perform doping on the P-type semiconductor substrate to form an ultra-shallow junction, so as to further illustrate the present invention. The process steps are as follows: 1. Put the cleaned P-type silicon wafer on the slide table in the vacuum chamber, and the silicon wafer is facing the transparent glass window 1. 2. Close the door of the vacuum chamber, and evacuate the vacuum chamber to 10Pa , and at the same time turn on the heater to heat the substrate at a heating temperature of 400°C. 3. When the vacuum degree reaches the background vacuum degree, the heating temperature is stable at 400°C for more than 15 minutes, and after the silicon wafer is evenly heated, a PH with a flow rate of 300 sccm is introduced into the vacuum chamber. 3 and H 2 The mixed gas, where PH 3The percentage content is 8%. At the same time, adjust the pumping rate to keep th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More