Full digital phase-locked loop applying rapid frequency capture method

An all-digital phase-locked loop and frequency capture technology, applied in the automatic control of power, electrical components, etc., can solve the deterioration of the phase-locked loop, the output clock jitter performance of the phase-locked loop, the stability of the phase-locked loop system, and the locking time of the phase-locked loop Unsatisfactory and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0063] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

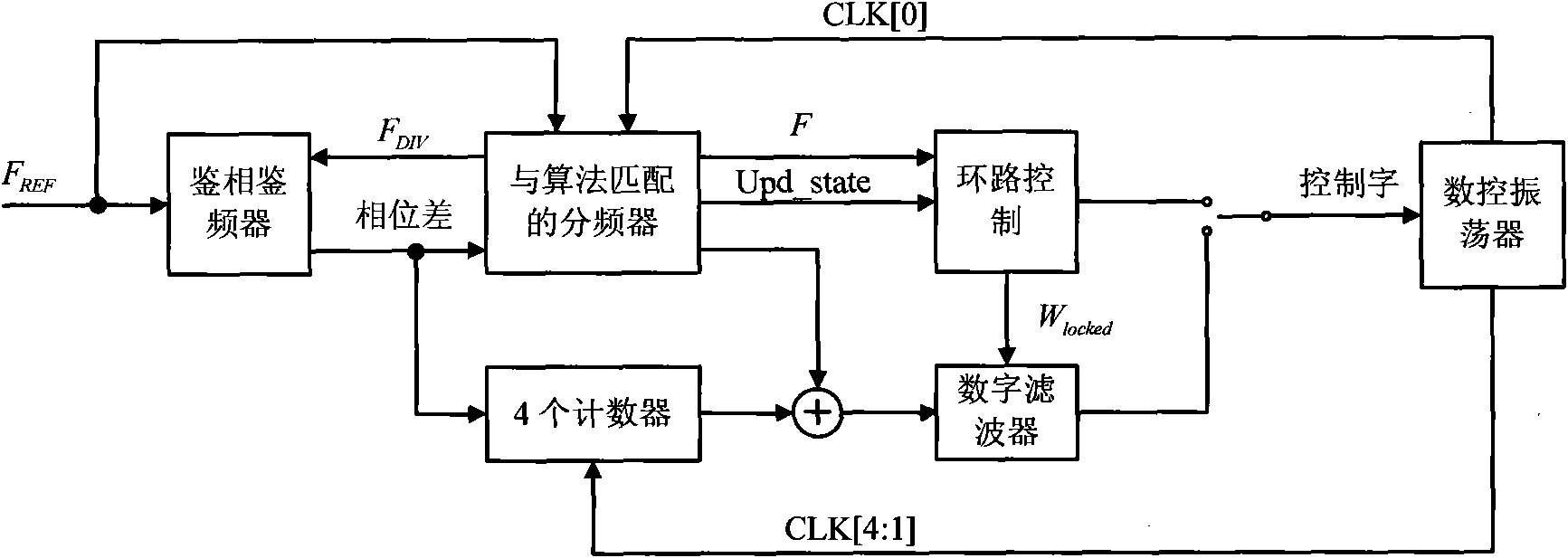

[0064] see image 3, the all-digital phase-locked loop of the fast frequency capture algorithm proposed by the present invention is provided with two loops of fast frequency capture and phase locking, and the two loops work alternately. First, the frequency capture is completed by the fast frequency capture loop, and then by A phase-locked loop completes precise locking. There are 4 counters in the figure, and the number of counters varies with the number of clocks with different phases that the numerical control oscillator can generate. The selected numerically controlled oscillator is a five-level loop numerically controlled oscillator, so five high-frequency clocks with different phases can be generated, named CLK[0], CLK[1], CLK[2], CLK[3] and CLK respectively [4]. CLK[0] is sent into the frequency divider matching the algorithm, CLK[1]...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More