Package structure and manufacture method thereof

A packaging structure and patterning technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems such as device failure, achieve the effect of improving packaging reliability and avoiding collapse

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings.

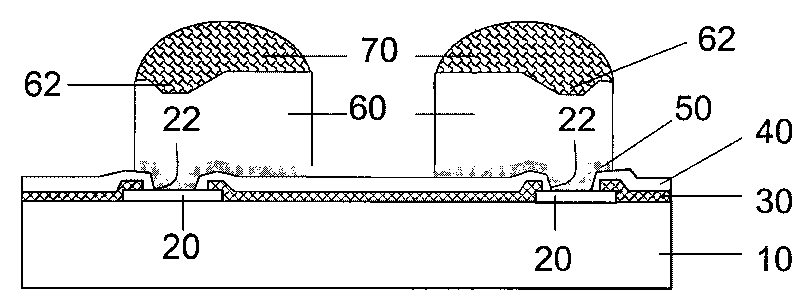

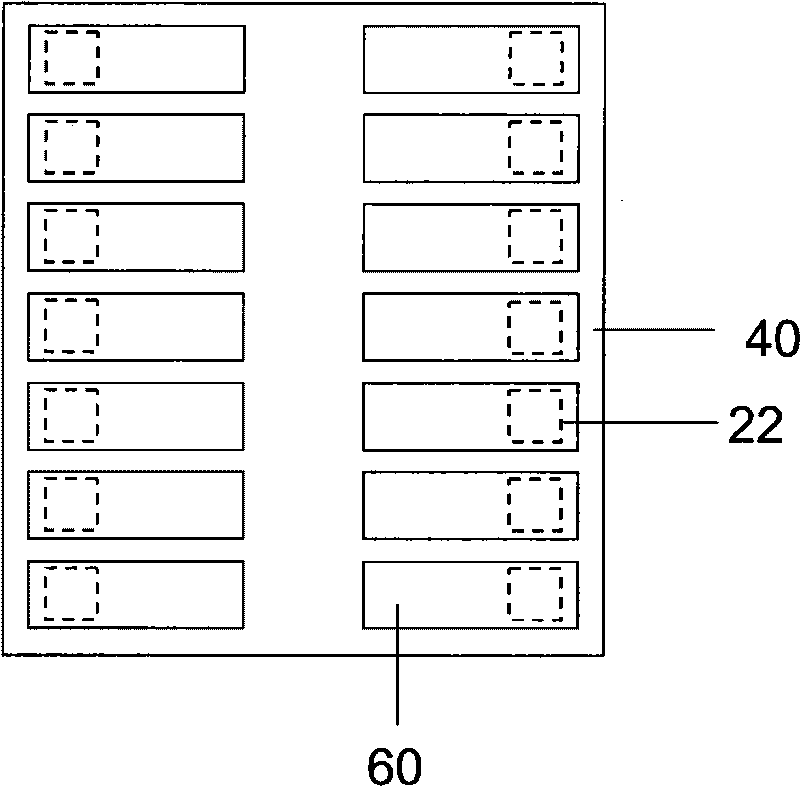

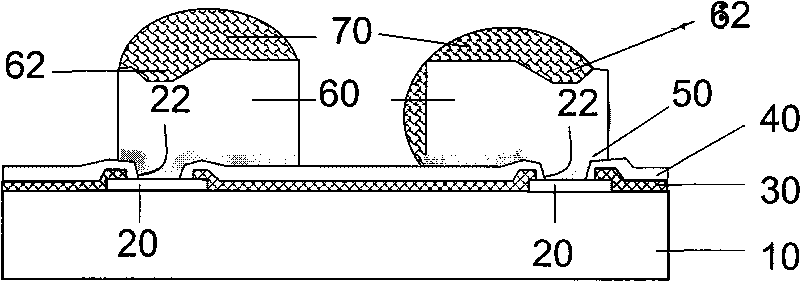

[0047] Image 6 Shown is a structural schematic diagram of an embodiment of the packaging structure of the present invention. Such as Image 6 As shown, the package structure includes a semiconductor substrate 10 , a contact pad 20 , a passivation layer 30 , a stress buffer layer 40 , and a stud bump composed of an UBM seed layer 50 , pillars 60 , and solder bumps 70 . 10 is a semiconductor substrate of a chip, and at least one active device is formed in the semiconductor substrate 10 . More than one contact pad (I / O port) 20 is formed on the semiconductor substrate 10 and is usually made of aluminum, copper, or an alloy material of the aforementioned metals. The passivation layer 30 is covered on the semiconductor substrate 10, and the contact pad 20 is expose...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More