Device and method for testing system-on-chip chip with multiple isomorphic IP cores

A system-on-chip and testing device technology, which is applied in measuring devices, digital circuit testing, electronic circuit testing, etc., can solve the problems of inconsistent running status, occupying shift time, and unintuitive processing, so as to reduce the time of vector debugging, The area overhead is small and the effect of saving test cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] In order to make the purpose, technical solution and advantages of the present invention clearer, a system-on-chip (SOC) chip testing device and method with an isomorphic IP core of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention rather than limit the present invention.

[0040] The solution provided by the invention utilizes the characteristics of the isomorphic IP core, and uses limited IO resources and simple control logic to achieve the purpose of reducing the amount of test data and test cost.

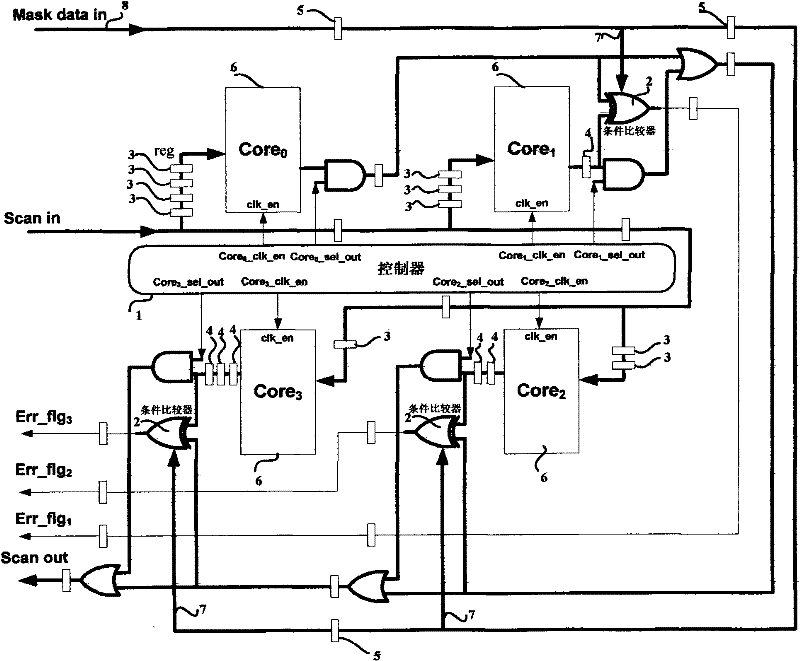

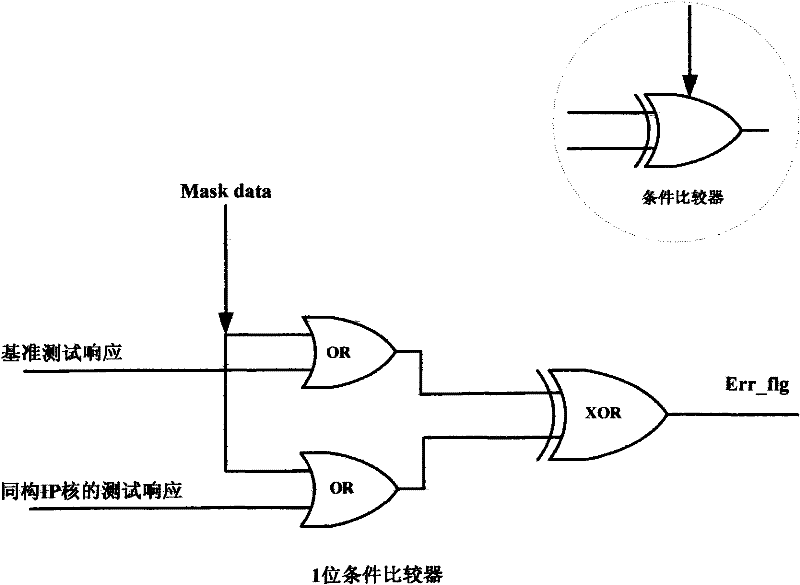

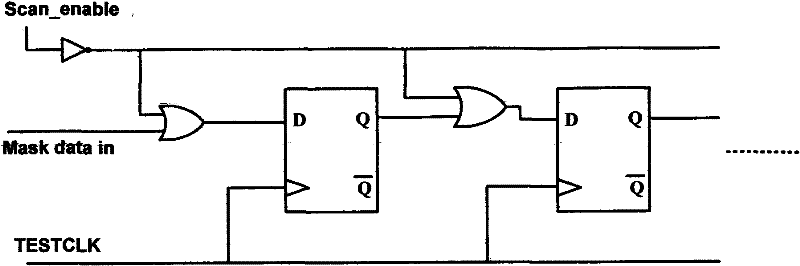

[0041] The system-on-chip (SOC) chip testing device with isomorphic IP core of the embodiment of the present invention, as figure 1 As shown, in a SoC chip with multiple isomorphic IP cores 6, including a controller 1, and a plurality of conditional comparators 2 corresponding to ea...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More