Semiconductor module and portable device

A portable device, semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

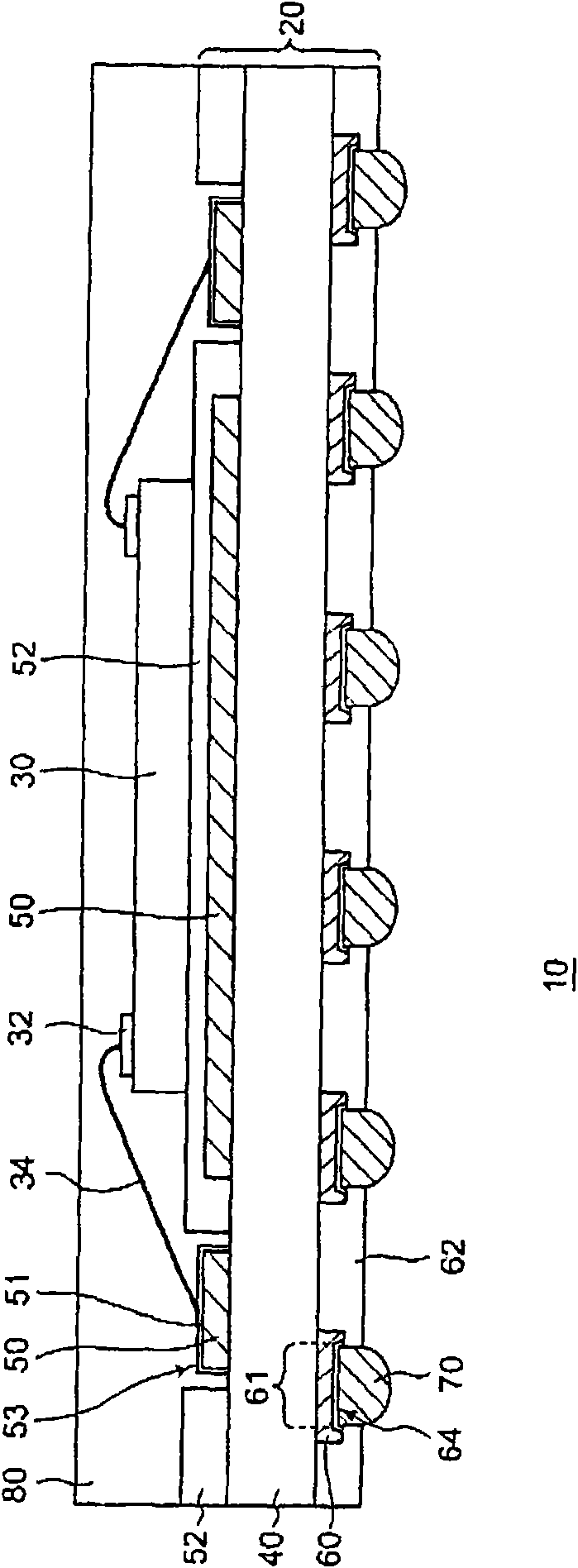

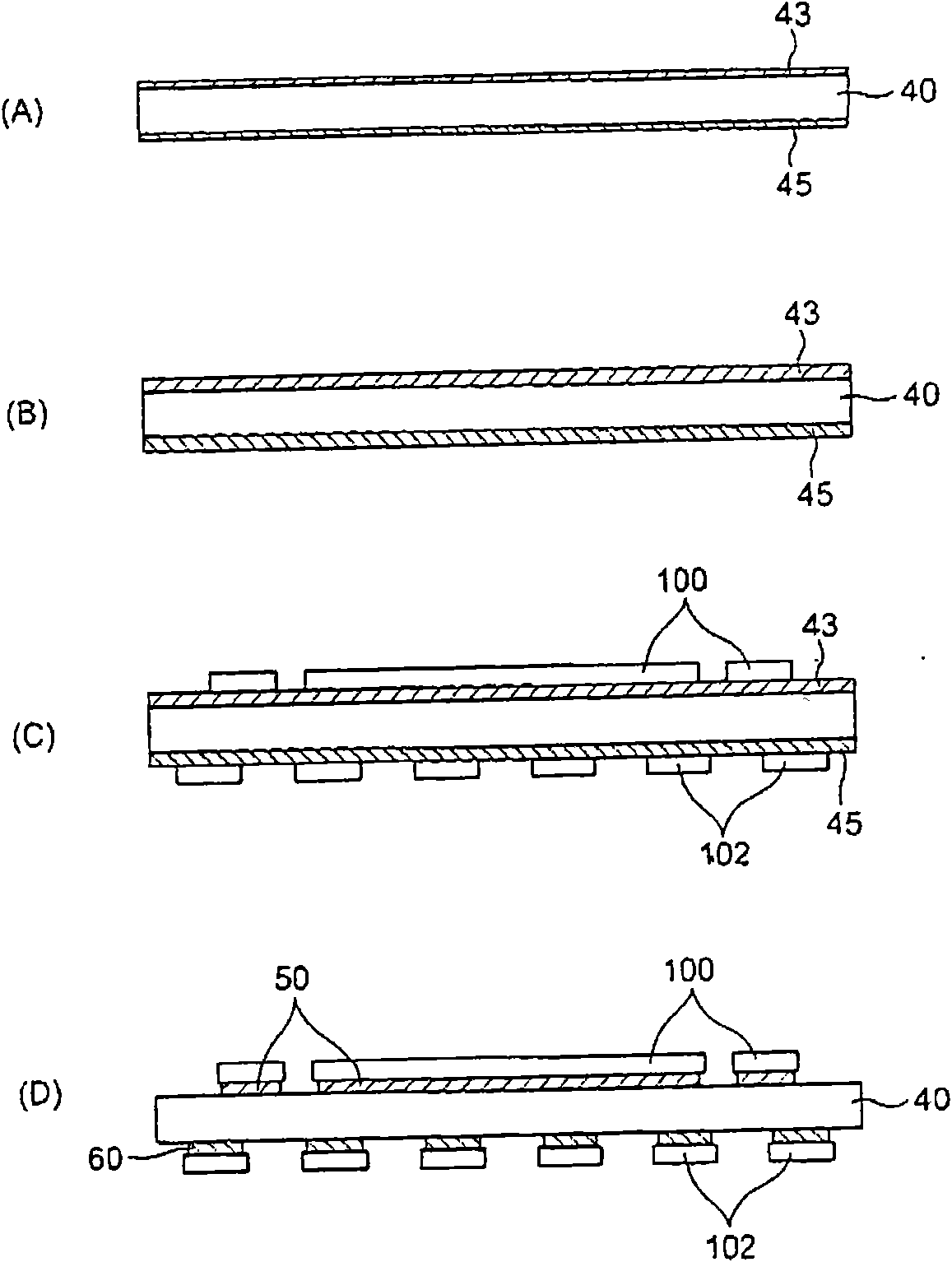

[0023] figure 1 It is a sectional view showing the structure of the semiconductor module of Embodiment 1. The semiconductor module 10 includes an element mounting substrate 20 and a semiconductor element 30 . In this embodiment, the semiconductor element 30 is connected to the element mounting substrate 20 by wire bonding.

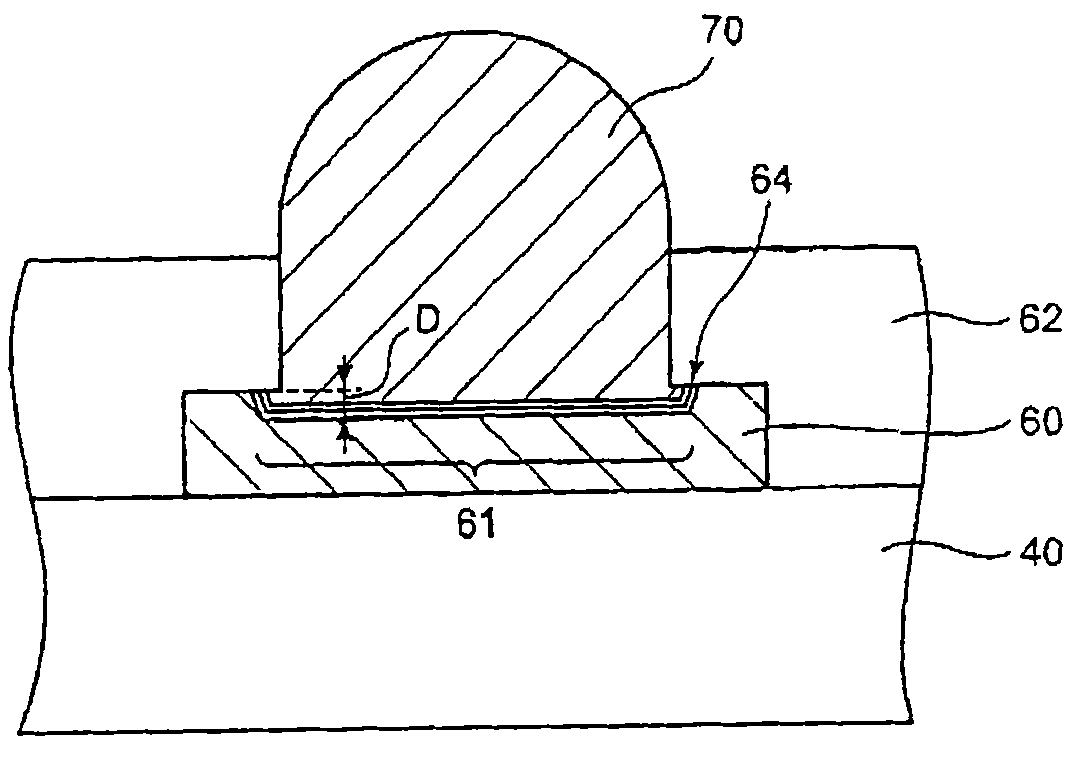

[0024] The element mounting substrate 20 includes an insulating resin layer 40, a wiring layer 50 provided on one main surface (semiconductor element mounting side) of the insulating resin layer 40, a protective layer 52, and the other main surface of the insulating resin layer 40. The wiring layer 60, the protective layer 62, and the solder ball 70.

[0025] Examples of materials constituting the insulating resin layer 40 include melamine dielectrics such as BT resins, liquid crystal polymers, epoxy resins, PPE resins, polyimide resins, fluorine-containing resins, phenolic resins, and polyamide bismaleimide. and other thermosetting resins. From the vi...

Embodiment approach 2

[0057] Figure 6 It is a sectional view showing the structure of the semiconductor module of Embodiment 2. The semiconductor module 10 of the present embodiment has a three-dimensional packaging substrate structure called a package-on-package (PoP) in which a package is mounted on a package.

[0058] In the present embodiment, the semiconductor element 30 is flip-chip connected to the element mounting substrate 20 with the electrode-formed surface facing downward.

[0059] Specifically, the wiring layer 50 includes a substrate electrode 51a for flip-chip connection and a substrate electrode 51b for stack packaging. The surface of the substrate electrode 51 a is covered with a Ni / Au layer 53 , and the element electrode 32 provided on the electrode forming surface of the semiconductor element 30 and the Ni / Au layer 53 are bonded by the solder 36 . The sealing resin 80 is provided near the semiconductor element 30 , and a part of the wiring layer 50 including the substrate elec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More